Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля цифровых устройств, в системах управления технологическими процессами, в частности в устройствах, осуществляющих обмен между ЭВМ и обьектами контроля и управления.

Целью изобретения является-расширение функциональных возможностей путем реализации универсальных диаграмм контроля.

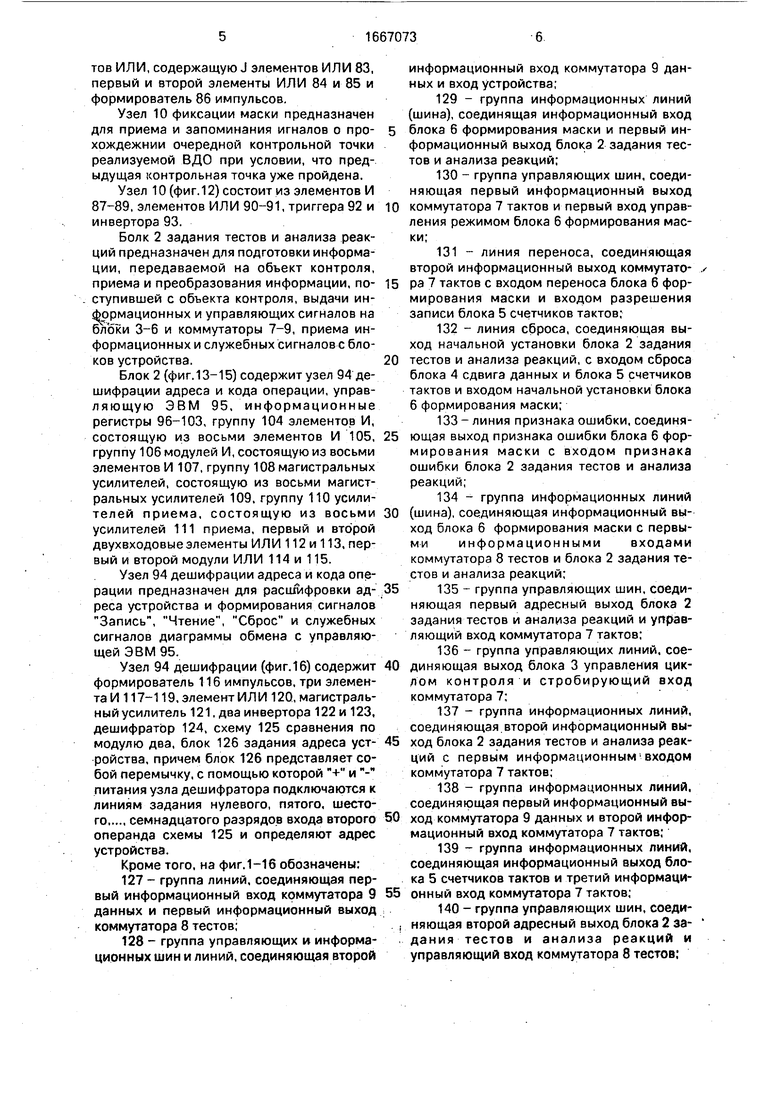

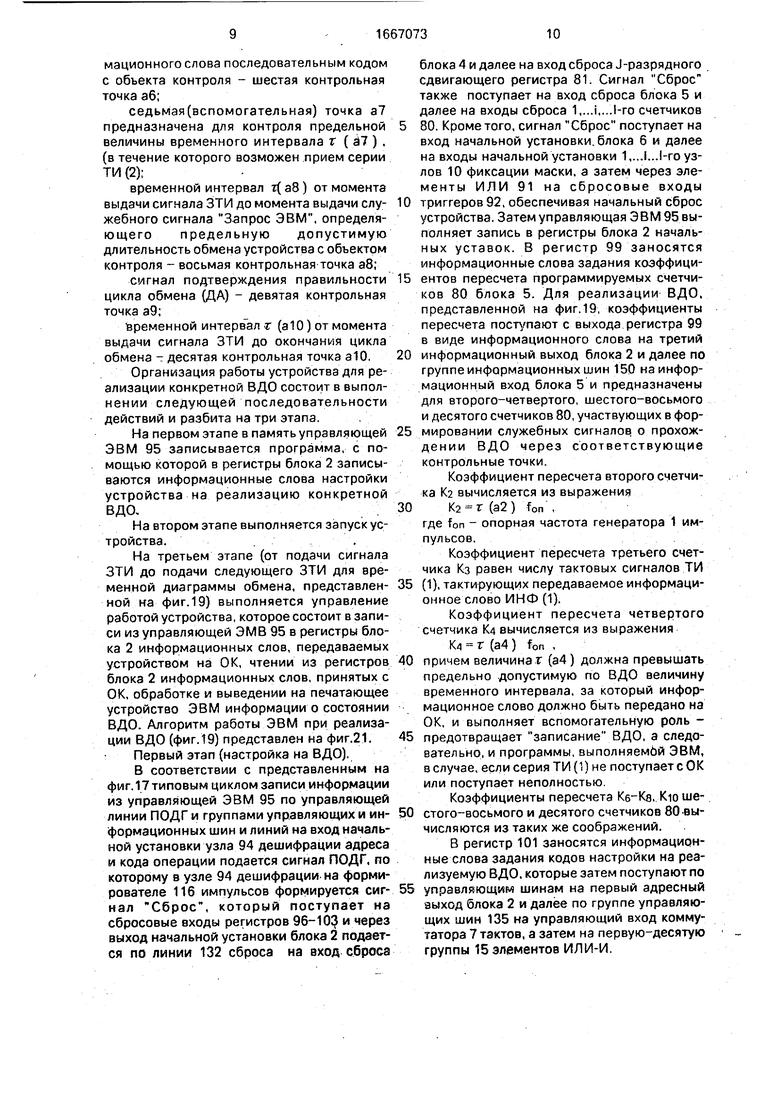

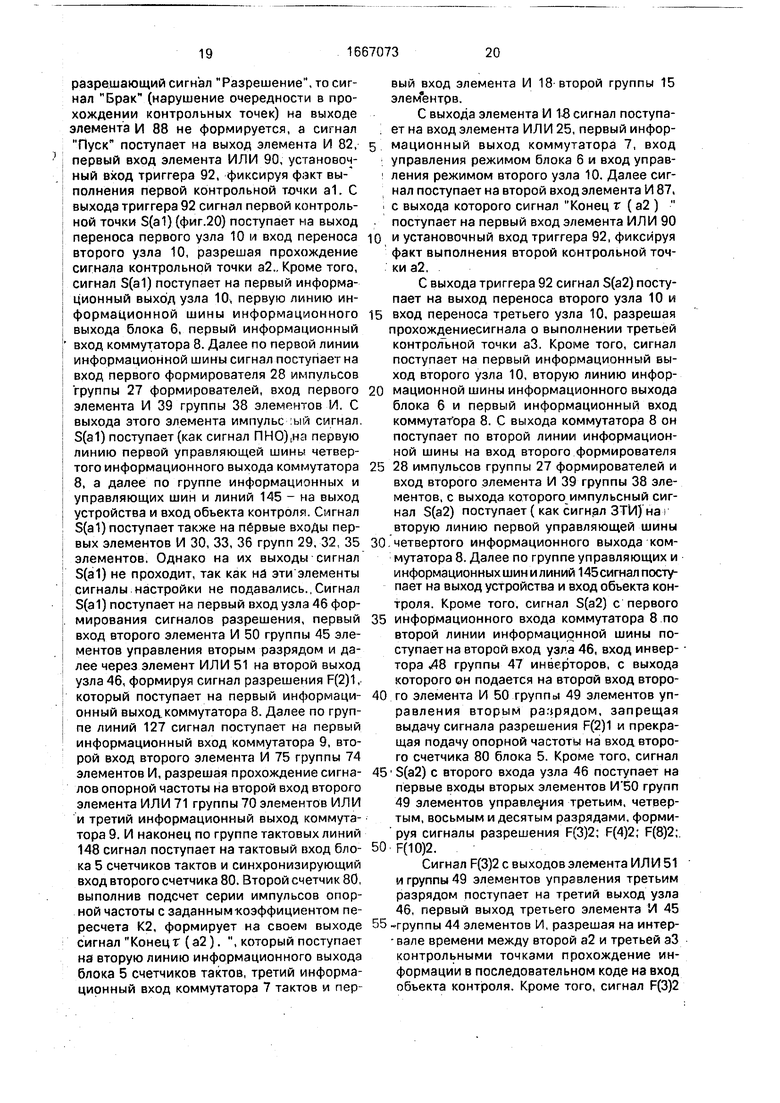

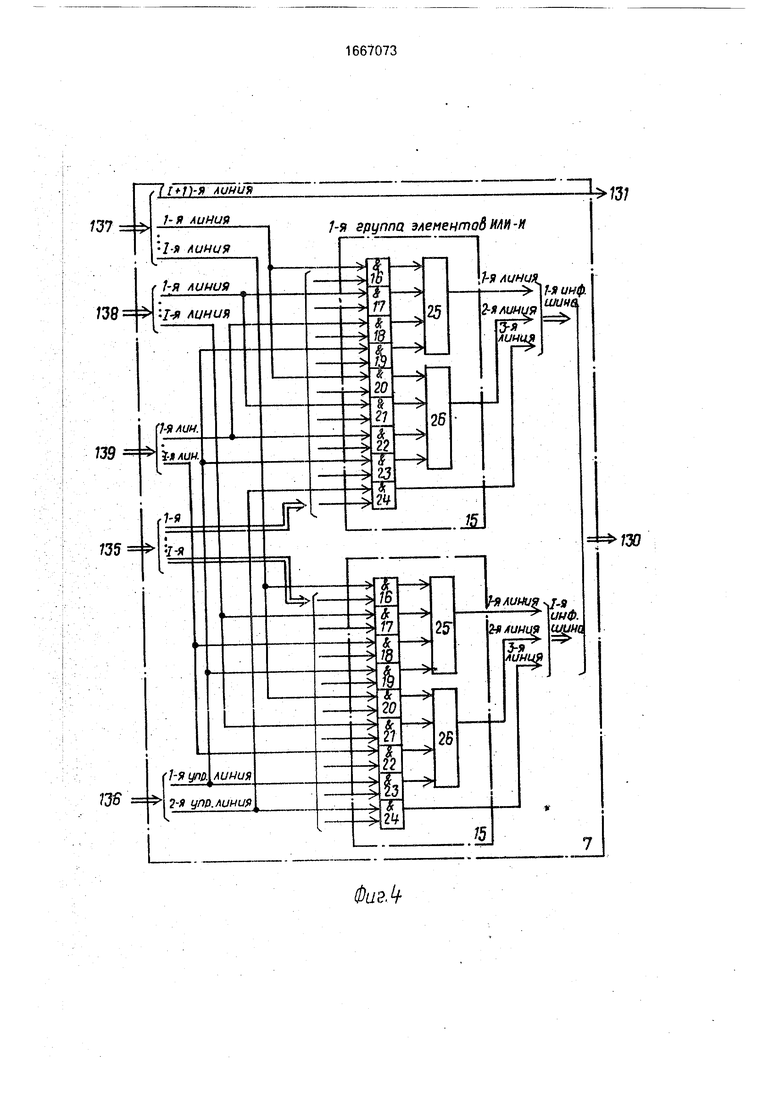

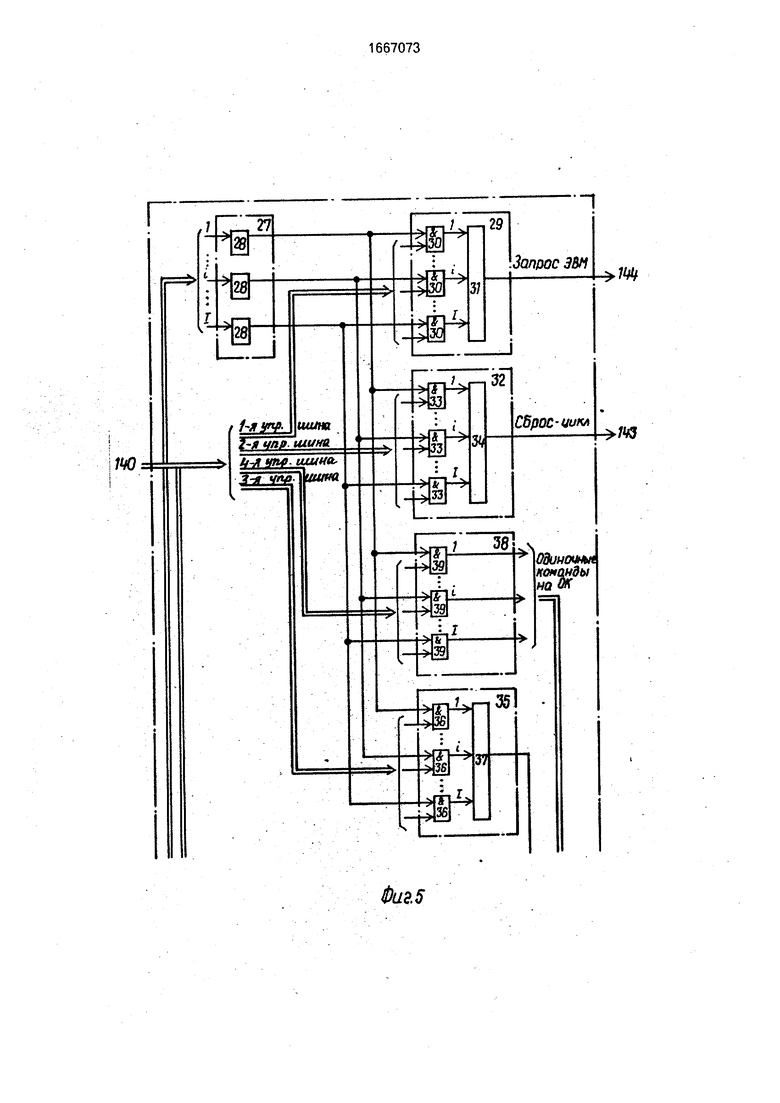

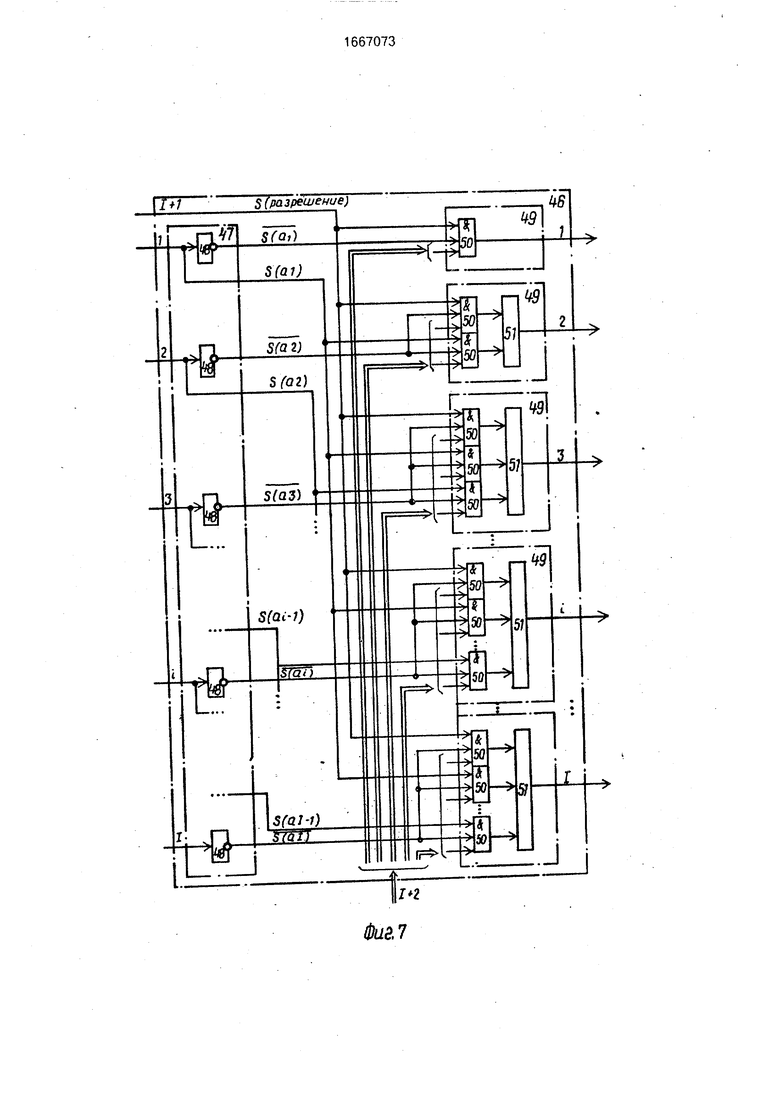

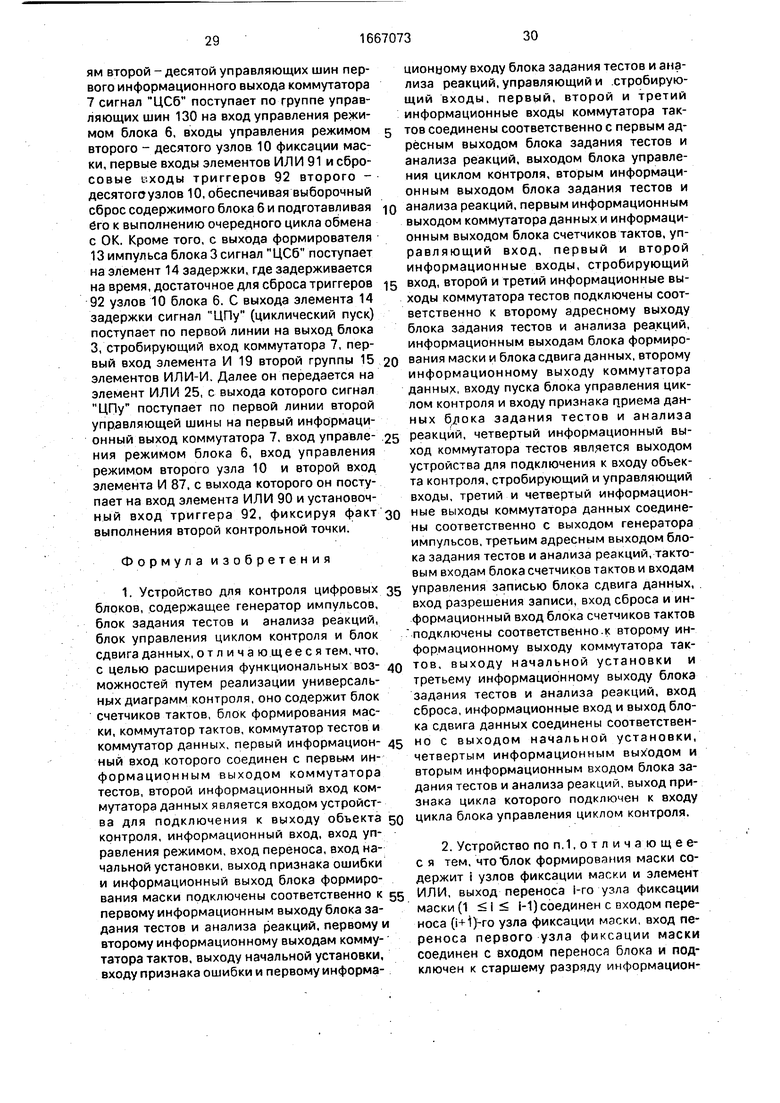

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - схема блока формирования маски; на фиг.З - схема блока управления циклом контроля; на фиг.4 - схема коммутатора тактов; на фиг.5 и 6 - схема коммутатора тестов; на фиг.7 - схема узла формирования сигналов разрешения; на фиг.8 и 9 - схема коммутатора данных; на фиг. 10 - схема блока счетчиков тактов; на фиг.11 - схема блока сдвига данных; на фиг. 12 - схема узла фиксации маски;

на фиг.13-15 - схема блока задания тестов и анализа реакций; на фиг. 16 - схема де- , шифратора адреса и кода операции; на фиг 17 - типовой цикл записи информации из управляющей ЭВМ в регистры блока задания тестов и анализа реакций; на фиг. 18 - типовой цикл чтения информации из регистров блока задания тестов и анализа реакций в управляющую ЭВМ; на фиг 19 - пример временной диаграммы обмена с объектом контроля, на фиг.20 - распределения контрольных точек временной диаграммы обмена по узлам фиксации маски блока формирования маски: на фиг.21 - алгоритм работы ЭВМ при работе в составе блока задания тестов и анализа реакций.

Устройство (фиг.1) содержит генератор 1 импульсов, блок 2 задания тестов и анализа реакций, блок 3 управления циклом контроля, блок 4 сдвига данных, блок 5 счетчиков тактов, блок 6 формирования масл

с

ON ON V4

О V4 CJ

ски, коммутатор 7 тактов, коммутатор 8 тестов и коммутатор 9 данных.

Блок 6 формирования маски предназначен для приема поступающих с коммутатора 7 тактов служебных сигналов об очередности прохождения I контрольных точек реа- .лизуемой временной диаграммы обмена (ВДО).

Блок 6 (фиг.2) состоит из I узлов 10 фиксации маски и схемы ИЛИ 11 ,на I входов.

Блок 3 управления циклом контроля предназначен для обеспечения возможности зацикливания фрагментов временных диаграмм обмена.

Блок 3 (фйг.З) содержит элемент И 12, формирователь 13 импульсов и элемент 14 задержки.

Коммутатор 7 тактов предназначен для сбора служебных сигналов о прохождении контрольных точек ВДО, поступающих с выхода блоков 2, 3 и 5 и коммутатора 9.

Коммутатор 7 (фиг.4) состой из I групп 15 элементов ИЛИ-И, каждая ,з которых содержит элементы И 16-24 и элементы ИЛИ 25 и 26.

Коммутатор 8 тестов предназначен для приема информационных слов, тактовых сигналов и одиночных команд, поступающих соответственно с блока 4, коммутатора 9 и блока 6, и дальнейшей передачи их на выход устройства и далее на объект контроля.

Коммутатор 8 (фиг.5 и 6) содержит группу 27 формирователей импульсов, состоящую из I формирователей 28, первую группу 29 элементов ИЛИ-И, состоящую из I элементов И 30 и одного элемента ИЛИ 31, вторую группу 32 элементов ИЛИ-И. состоящую из I элементов И 33 и одного элемента ИЛИ 34, третью группу 35 элементов ИЛИ- И, состоящую из I элементов И 36 и одного элемента ИЛИ 37, i руппу 36 двухвходовых элементов И, состоящую из I элементов И 39, первую группу 40 трехвходовых элементов И, состоящую из J элементов И 41, вторую группу 42 трехвходовых элементов И, состоящую из I элементов И 43, группу 44 четырехвходовых элементов И, состоящую из I элементов И 45, и узел 46 формирования сигналов разрешения.

Узел 46 формирования сигналов разрешения предназначен для фомирования I сигналов (I 11); каждый i-й сигнал предназначен для управления группами элементов коммутаторов 8 и 9 и в зависимости от реализуемой ВДО может формироваться на i-м выходе узла 46.

Узел 46 (фиг.7) содержит группу 47 инверторов, состоящую из I инверторов 48, и I групп 49 элементов управления 1,...,..,1-м

разрядами, причем группа 49 элементов управ/Гения 1-м разрядом содержит элемент И 50, группа 49 элементов управления 2-м разрядом - два элемента И 50 и элемент ИЛИ

51 на два входа, группа 49 элементов управления 3-м разрядом - три элемента И 50 и

элемент ИЛИ 51 на три входагруппа 49

элементов управления 1-м разрядом - 1 элементов И 50 и элемент ИЛИ 51 на I входов

0 группа 49 элементов управления I-м разрядом - I элементов И 50 и элемент ИЛИ 51 на I входов.

Коммутатор 9 данных предназначен для приема информационных слов, тактовых

5 сигналов и одиночных команд, поступающих с объекта контроля на вход устройства, и дальнейшей передачи на блоки 4 и 5 и коммутаторы 7 и 8,

Коммутатор 9 (фиг.8 и 9) содержит пер0 вую группу 52 элементов ИЛИ-И, состоящую из N элементов И 53 и одного элемента ИЛИ 54, вторую группу 55 элементов ИЛИ-И, со- стоящукгиз I элементов И 56 и одного элемента ИЛИ 57, третью группу 58 элементов

5 ИЛИ-И. состоящую из М элементов И 59 и одного элемента ИЛИ 60, четвертую группу 61 элементов ИЛИ-И, состоящую из I элементов И 62 и одного элемента ИЛИ 63, первую группу 64 двухвходовых элементов

0 И, состоящую из J элементов И 65, вторую группу 66 двухвходовых элементов И, состоящую из I элементов И 67, третью группу 68 двухвходовых элементов И; состоящую из I элементов И 69, группу 70 элементов ИЛИ,

5 состоящую из I элементов ИЛИ 71, первую группу 72 трехвходовых элементов И, состоящую из элементов И 73, вторую группу 74 трехвходовых элементов И, состоящую из I элементов И 75, первого и второго элемен0 тов ИЛИ 76 и 77, первого и второго элементов 78 и 79 задержки.

Блок 5 счетчиков т.чктов предназначен для подсчета числа тактовых сигналов, стро- бирующих передачу информации на обьект

5 или с объекта контроля, а также для подсчета сигналов опорной частоты, с помощью которой задаются величины временных интервалов реализуемой ВДО.

Блок 5 (фиг. 10) состоит из I счетчиков 80

0 с программируемым коэффициентом пересчета.

Блок 4 сдвига данных предназначен для приема информации в формате блока 2 задания тестов и анализа реакций и преобра5 зования ее в формат объекта контроля, а также для приема информации в формате объекта контроля и преобразования ее в формат блока 2.

Блок 4 (фиг.11) содержит J-разрядный сдвигающий регистр 81, группу 82 элементов ИЛИ, содержащую J элементов ИЛИ 83, первый и второй элементы ИЛИ 84 и 85 и формирователь 86 импульсов.

Узел 10 фиксации маски предназначен для приема и запоминания игналов о про- хождежнии очередной контрольной точки реализуемой ВДО при условии, что предыдущая контрольная точка уже пройдена.

Узел 10 (фиг. 12) состоит из элементов И 87-89, элементов ИЛИ 90-91, триггера 92 и инвертора 93.

Болк 2 задания тестов и анализа реакций предназначен для подготовки информации, передаваемой на объект контроля, приема и преобразования информации, по- ступившей с объекта контроля, выдачи информационных и управляющих сигналов на блоки 3-6 и коммутаторы 7-9, приема информационных и служебных сигналов с блоков устройства,

Блок 2 (фиг. 13-15) содержит узел 94 дешифрации адреса и кода операции, управляющую ЭВМ 95, информационные регистры 96-103, группу 104 элементов И, состоящую из восьми элементов И 105, группу 106 модулей И, состоящую из восьми элементов И 107, группу 108 магистральных усилителей, состоящую из восьми магистральных усилителей 109, группу 110 усилителей приема, состоящую из восьми усилителей 111 приема, первый и второй двухвходовые элементы ИЛИ 112 и 113, первый и второй модули ИЛИ 114 и 115.

Узел 94 дешифрации адреса и кода операции предназначен для расшифровки ад- реса устройства и формирования сигналов Запись, Чтение, Сброс и служебных сигналов диаграммы обмена с управляющей ЭВМ 95.

Узел 94 дешифрации (фиг. 16) содержит формирователь 116 импульсов, три элемента И 1 17-119, элемент ИЛИ 120, магистральный усилитель 121, два инвертора 122 и 123, дешифратор 124, схему 125 сравнения по модулю два, блок 126 задания адреса уст- ройства, причем блок 126 представляет собой перемычку, с помощью которой + и - питания узла дешифратора подключаются к линиям задания нулевого, пятого, шестогосемнадцатого разрядов входа второго

операнда схемы 125 и определяют адрес устройства.

Кроме того, на фиг. 1-16 обозначены:

127- группа линий, соединяющая первый информационный вход коммутатора 9 данных и первый информационный выход коммутатора 8 тестов;

128- группа управляющих и информационных шин и линий, соединяющая второй

информационный вход коммутатора 9 данных и вход устройства;

129- группа информационных линий (шина), соединящая информационный вход блока 6 формирования маски и первый информационный выход блока 2 задания тестов и анализа реакций;

130- группа управляющих шин, соединяющая первый информационный выход коммутатора 7 тактов и первый вход управления режимом блока 6 формирования маски;

131- линия переноса, соединяющая второй информационный выход коммутатора 7 тактов с входом переноса блока 6 формирования маски и входом разрешения записи блока 5 счетчиков тактов;

132- линия сброса, соединяющая выход начальной установки блока 2 задания тестов и анализа реакций, с входом сброса блока 4 сдвига данных и блока 5 счетчиков тактов и входом начальной установки блока 6 формирования маски;

133- линия признака ошибки, соединяющая выход признака ошибки блока 6 формирования маски с входом признака ошибки блока 2 задания тестов и анализа реакций;

134- группа информационных линий (шина), соединяющая информационный выход блока 6 формирования маски с первыми информационными входами коммутатора 8 тестов и блока 2 задания тестов и анализа реакций;

135- группа управляющих шин, соединяющая первый адресный выход блока 2 задания тестов и анализа реакций и управляющий вход коммутатора 7 тактов;

136- группа управляющих линий, соединяющая выход блока 3 управления циклом контроля и стробирующий вход коммутатора 7;

137- группа информационных линий, соединяющая второй информационный выход блока 2 задания тестов и анализа реакций с первым информационным входом коммутатора 7 тактов;

138- группа информационных линий, соединяющая первый информационный выход коммутатора 9 данных и второй информационный вход коммутатора 7 тактов;

139- группа информационных линий, соединяющая информационный выход блока 5 счетчиков тактов и третий информационный вход коммутатора 7 тактов;

140- группа управляющих шин, соединяющая второй адресный выход блока 2 за- дания тестов и анализа реакций и управляющий вход коммутатора 8 тестов:

141- группа информационных линий, соединяющая информационный выход блока 4 сдвига данных с вторым информационным входом блока задания тестов и анализа реакций и вторым информационным входом коммутатора 8 тестов;

142- линия строба, соединяющая второй информационный выход коммутатора 9 данных и стробирующий вход коммутатора 8 тестов;

143- линия циклического перезапуска, соединяющая второй информационный выход коммутатора 8 тестов с входом пуска блока 3 управления циклом контроля;

144- линия признака приема, соединяющая третий информационный выход ком мутатора 8 тестов с входом признака приема данных блока 2 задания тестов и анализа реакций;

145- группа управляющих и информационных шин и линий, соединяющая четвертый информационнывыход коммутатора 8 тестов с выходе устройства;

146- линия стробирующей частоты, соединяющая выход генератора 1 импульсов со стробирующим входом коммутатора 9 данных;

147- группа управляющих шин, соединяющая третий адресный выход блока 2 задания тестов и анализа реакций с управляющим входом коммутатора 9 данных;

148- группа тактовых линий, соединяющая третий информационный выход коммутатора 9 данных и тактовый вход блока 5 счетчика тактов;

149- группа управляющих и информационных шин и линий, соединяющая четвертый информационный выход коммутатора 9 данных с входом управления записью блока 4 сдвига данных;

150- группа информационных шин, соединяющая третий информационный выход блока 2 задания тестов и анализа реакций с информационным входом блока 5 счетчиков тактов;

151- группа информационных и управляющих линий, соединяющая четвертый информационный выход блока 2 задания тестов и анализа реакций с информационным входом блока 4 сдвига данных;

152- управляющая линия, соединяющая выход признака цикла блока 2 задания тестов и анализа реакций с входом цикла блока 3 управления циклом контроля

Устройство работает следующим образом.

Контроль цифровых блоков состоит в выполнении информационного обмена устройства (входящей в его состав управляющей ЭВМ 95) с объектом контроля (ОК) и заключается в преобразовании временной диаграммы обмена (ВДО) ЭВМ в ВДО объекта контроля. Основными элементами такой диаграммы являются:

одиночные команды: инициация начала обмена, запрос тактовых импульсов, стро- бирование передачи информационных слов параллельным кодом и т.д.;

информационные слова, передаваемые параллельным или последовательным кодом словами различного формата;

тактовые сигналы, стробирующие передачу информационных слов;

временные интервалы между одиночными командами, информационными словами;

число тактовых сигналов, стробирую- щих информационные слова, передаваемые

последовательным кодом.

Контрольная точка ВДО представляет собой факт выполнения основного элемента диаграммы обмена: саму ВДО можно представить в виде последовательности выполнения контрольных точек.

Работу устройства рассмотрим на примере реализации ВДО, представленной на фиг. 19; распределение сигналов на входах и выходах блока 6 формирования маски представлено на фиг.20.

Реализация указанной ВДО состоит в выполнении следующих основных элементов:

признак начала обмена (ПНО) - инициация объекта контроля на выполнение ВДО - первая контрольная точка а1;

временной интервал т( а2) от момента выдачи сигнала ПНО до выдачи сигнала ЭТИ (запрос тактовых импульсов) - вторая контрольная точка а2;

прием первой серии тактовых импульсов ТИ (1), стробирующих передачу информационного слова постедовательным кодом на объект контроля -- третья контрольная точка аЗ;

четвертая (вспомогательная) точка а4

предназначена для онтроля предельной

величины временного интервала г( а4) , (в

течение которого возможен прием серии

ТИ (1);

признак перезаписи (ПРЗ) - сигнал, поступающий с объекта контроля и предназначенный для инициации устройства на прием информационного слова последовательным кодом - пятая контрольная точка а5:

прием второй серии тактовых импульсов ТИ (2), стробирующих передачу информационного слова последовательным кодом с объекта контроля - шестая контрольная точка аб;

седьмая(вспомогательная) точка а7 предназначена для контроля предельной величины временного интервала т ( а7 ) , (в течение которого возможен прием серии ТИ (2):

временной интервал т{ а8 ) от момента выдачи сигнала ЭТИ до момента выдачи слу- жебного сигнала Запрос ЭВМ, определяющего предельную допустимую длительность обмена устройства с объектом контроля - восьмая контрольная точка а8;

сигнал подтверждения правильности цикла обмена (ДА) - девятая контрольная точка а9;

временной интервал t (аЮ) от момента выдачи сигнала ЭТИ до окончания цикла обмена - десятая контрольная точка аЮ.

Организация работы устройства для реализации конкретной ВДО состоит в выполнении следующей последовательности действий и разбита на три этапа.

На первом этапе в память управляющей ЭВМ 95 записывается программа, с помощью которой в регистры блока 2 записываются информационные слова настройки устройства на реализацию конкретной ВДО,

На втором этапе выполняется запуск устройства.

На третьем этапе (от подачи сигнала ЭТИ до подачи следующего ЭТИ для временной диаграммы обмена, представлен- ной на фиг.19) выполняется управление работой устройства, которое состоит в записи из управляющей ЭМВ 95 в регистры блока 2 информационных слов, передаваемых устройством на О К, чтении из регистров блока 2 информационных слов, принятых с ОК, обработке и выведении на печатающее устройство ЭВМ информации о состоянии ВДО. Алгоритм работы ЭВМ при реализации ВДО (фиг. 19) представлен на фиг.21.

Первый этап (настройка на ВДО).

В соответствии с представленным на фиг. 17 типовым циклом записи информации из управляющей ЭВМ 95 по управляющей линии ПОДГ и группами управляющих и ин- формационных шин и линий на вход начальной установки узла 94 дешифрации адреса и кода операции подается сигнал ПОДГ, по которому в узле 94 дешифрации на формирователе 116 импульсов формируется сиг- нал Сброс, который поступает на сбросовые входы регистров 96-103 и через выход начальной установки блока 2 подается по линии 132 сброса на вход сброса

блока 4 и далее на вход сброса J-разрядного сдвигающего регистра 81. Сигнал Сброс также поступает на вход сброса блока 5 и далее на входы сброса 1,...i,...l-ro счетчиков 80. Кроме того, сигнал Сброс поступает на вход начальной установки блока 6 и далее на входы начальной установки 1,.....,1-го узлов 10 фиксации маски, а затем через элементы ИЛИ 91 на сбросовые входы т риггеров 92, обеспечивая начальный сброс устройства. Затем управляющая ЭВМ 95 выполняет запись в регистры блока 2 начальных уставок. В регистр 99 заносятся информационные слова задания коэффициентов пересчета программируемых счетчиков 80 блока 5. Для реализации ВДО, представленной на фиг. 19. коэффициенты пересчета поступают с выхода регистра 99 в виде информационного слова на третий информационный выход блока 2 и далее по группе информационных шин 150 на информационный вход блока 5 и предназначены для второго-четвертого, шестого-восьмого и десятого счетчиков 80, участвующих в формировании служебных сигналов о прохождении ВДО через соответствующие контрольные точки.

Коэффициент пересчета второго счетчика К2 вычисляется из выражения

К2 г (а2 ) fon ,

где ton - опорная частота генератора 1 импульсов,

Коэффициент пересчета третьего счетчика Кз равен числу тактовых сигналов ТИ (1), тактирующих передаваемое информационное слово ИНФ (1).

Коэффициент пересчета четвертого счетчика К4 вычисляется из выражения

Кл т (а4 ) f0n ,

причем величина г (а4 ) должна превышать предельно допустимую по ВДО величину временного интервала, за который информационное слово должно быть передано на ОК, и выполняет вспомогательную роль - предотвращает записание ВДО, а следовательно, и программы, выполняемой ЭВМ, в случае, если серия ТИ() не поступает с ОК или поступает неполностью

Коэффициенты пересчета Ke-Ke, Kio шестого-восьмого и десятого счетчиков 80 вычисляются из таких же соображений.

В регистр 101 заносятся информационные слова задания кодов настройки на реализуемую ВДО. которые затем поступают по управляющим шинам на первый адресный аыход блока 2 и далее по группе управляющих шин 135 на управляющий вход коммутатора 7 тактов, а затем на первую-десятую группы 15 элементов ИЛИ-И.

В первую группу 15 элементов ИЛИ-И сигналы настройки поступают с выхода регистра 101 по первой управляющей шине на первый адресный выход блока 2 и далее по первой управляющей шине группы управляющих шин 135 на управляющий вход коммутатора 7, затем на второй вход элемента И 16, разрешая прохождение сигнала Пуск.

Во вторую группу 15 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 7 по второй управляющей шине на вторые входы элементов И 18. 23, 24, разрешая прохождение сигналов Конец т (а2 ), ЦСб (циклический сброс), ЦПу (циклический пуск).

В третью группу 15 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 7 по третьей управляющей шине на вторые входы элементов И 18 и 24, разрешая прохождение сигналов Конец ТИ (1), ЦСб.

В четвертую группу 15 элв энтов ИЛИ- И, сигналы поступают с управляющего входа коммутатора 7 по четвертой управляющей шине на вторые входы элементов И 18 и 24, разрешая прохождение сигналов Конец г (а4), ЦСб.

В пятую группу 15 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 7 по пятой управляющей шине на вторые входы элементов И 17 и 24, разрешая прохождение сигналов ПРЗ, ЦСб.

В шестую группу 15 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 7 по шестой управляющей шине на вторые входы элементов И 18 и 24, разрешая прохождение сигналов Конец ТИ (2), ЦСб.

В седьмую группу 15 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 7 по седьмой управляющей шине на вторые входы элементов И 18 и 24, разрешая прохождение сигналов Конец г (а7), ЦСб.

В восьмую группу 15 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 7 по восьмой управляющей шине на вторые входы элементов И 18 и 24, разрешая прохождение сигналов Конец т (а8), ЦСб.

В девятую группу 15 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 7 по девятой управляющей шине на вторые входы элементов И 16 и 24, разрешая прохождение сигналов ДА ЭВМ, ЦСб.

В десятую группу 15 элементов ИЛИ-И сигналы поступают с управляющего входа

коммутатора 7 по десятой управляющей ши- не на вторые входы элементов И 18 и 24, разрешая прохождение сигналов Конец г(аЮ), ЦСб.

. В регистр 102 заносятся информационные слова задания кодов настройки на реализуемую временную диаграмму обмена, которые затем поступают по управляющим шинам на второй адресный выход блока 2 и

0 далее по группе управляющих шин 140 на управляющий вход коммутатора 8 тестов, а затем на группы 29, 32, 35, 38, 40, 42, 44 элементов и узел 46 формирования сигналов разрешения.

5 ДЛР реализации ВДО(фиг.19) необходимы следующие сигналы настройки.

Во вторую группу 32 элементов ИЛИ-И сигналы настройки поступают с выхода регистра 102 по второй управляющей шине на

0 второй адресный выход блока 2, далее на управляющий вход коммутатора 8, и затем по десятой линии - на второй вход десятого элемента И 33. разрешая прохождение сигнала о выполнении контрольной точки аЮ

5 на второй информационный выход коммутатора 8 для формирования сигнала Сброс - Цикл.

В группу 38 двухвходовых элементов И сигналы поступают с управляющего входа

0 коммутатора 8 по четвертой управляющей шине, по первой, второй и девятой линиям на вторые входы первого, второго и девятого элементов И 39. разрешая прохождение сигналов о выполнении первой (а1), второй

5 (а2) и девятой (а9) контрольных точек, и далее по первой управляющей шине на четвертый информационный выход коммутатора 8 для формирования сигналов ЭТИ ПНО, ДА, передаваемых на ОК(фиг.20).

0 В группу 44 четырехвходовых элементов И сигналы поступают с управляющего входа коммутатора 8 по шестой управляющей шине на второй иход одного из I элементов И 45, разрэшая прохождение

5 информационных слов в последовательном коде по одной из i линий (i 1,...Л).на объект контроля. Для реализации указанной ВДО сигнал поступает на второй вход второго элемента И 45, так как передача информа0 ционного слова заканчивается при достижении второй а2 контрольной точки.

Во вторую группу 42 трехвходовых элементов И 43 сигналы поступают с управляющего входа коммутатора 8 по седьмой

5 управляющей шине на второй вход одного из I элементов И 43, разрешая прохождение тактовых импульсов, стробирующих передачу информационных слов в последовательном коде по одной из I линий на объект контроля. Для реализации данной ВДО сигнал настройки поступает на второй вход второго элемента И 43.

В первую группу 29 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 8 по первой управляющей шине ,по восьмой линии на второй вход восьмого элемента И 30, разрешая прохождение сигнала о выполнении восьмой контрольной точки, и далее на третий информационный выход коммутатора 8 для формирования сигнала Запрос ЭВМ.

В группу 35 элементов ИЛИ-И сигналы поступают с управляющего входа коммутатора 8 по третьей управляющей шине, разрешая прохождение сигнала Чтение параллельного кода (в указанной ВДО не применяется).

В группу 40 элементов И сигналы поступают с управляющего входа коммутатора 8 по пятой управляющей шине, разрешая прохождение параллельного информационного слова (в данной ВДО не применяется),

В узел 46 формирования сигналов разрешения сигналы настройки поступают с выхода регистра 102 по восьмой управляющей шине на второй адресный выход блока 2 и далее по группе управляющих шин 140 на управляющий вход коммутатора 8, затем по восьмой управляющей шине - на l+2-й вход узла 46 и по первой-десятой группам управляющих линий на группы 49 управления первым-десятым разрядами.

В группе 49 элементов управления первый разряд на третьем входе элемента И 50 формируется из соотношения

F(1)P S(P) STal)

где F(1)P - сигнал разрешения на выходе группы 49 элементов управления первым разрядом;

S(P) - сигнал Разрешение, поступающий с регистра 100 по 1 + 1-й линии информационной шины на второй информационный выход блока 2 (далее по группе информационных линий 137 - на первый информационный вход коммутатора 7 тактов, на второй информационный выход коммутатора 7 - по линии 131 переноса, на вход переноса блока б формирования маски, и по 1+1-й линии - на информационный выход блока 6, а по группе информационных линий 134 - на первый информационный вход коммутатора 8 и по i+1-й линии - на вход узла 46);

S(a1) - инвертированный сигнал о выполнении первой контрольной точки.

Сигнал разрешения F(1)P формируется от момента поступления сигнала Разрешение до момента выполнения первой контрольной точки (в указанной ВДО не применяется).

В группе 49 элементов управления вторым разрядом (на третьих входах первого и второго элементов И 50) сигналы разрешения формируются из соотношений: F(2)P S(P) 5{a2):

F(2)P 1 S(a1) Sfa2).

Сигнал разрешения F(2)P формируется от момента поступления сигнала Разрешение до момента выполнения второй конт- 0 рольной точки (в данной ВДО не применяется). Сигнал разрешения F(2)1 формируется от момента поступления сигнала о выполнении первой контрольной точки до момента выполнения второй 5 контрольной точки и поступает на коммутаторы 8 и 9, разрешая прохождение опорной частоты на счетчики 80 блока 5 счетчиков тактов.

В группе 49 элементов управления 0 третьим разрядом (на третьих входах первого, второго и третьего элементов И 50) сигналы F(3)P. F(3)1. F(3)2 формируются из соотношений:

F(3)P S(P) S(a3); 5F(3)(a1)3{a3):

F(3)2 S(a2) Sfa3J.

В указанной ВДО применяется сигнал F(3)2, с помощью которого формируется разрешение на коммутаторы 8 и 9 - обеспечи- 0 вается прохождение на устройство тактовых сигналов ТИ (1). а на обьект контроля - прохождение информационных слов в интервале от второй до третьей контрольных точек.

5 В группе 49 элементов управления четвертым разрядом сигналы поступают на третьи входы первогочетвертого элементов И 50 (сигналы F(4)P; F(4)1: F(4)3 не применяются в данной ВДО). 0 Сигнал

F(4)2 S(a2) S(a4)

формирует разрешение на коммутаторы 8 и 9, обеспечивая прохождение сигналов опорной частоты на вход счетичков 80 для под- 5 счета временного интервала т ( э4 ).

В группе 49 элементов управления пятым разрядом сигналы поступают на третьи

входы первогопятого элементов И 50

(сигналы F(5)PF(5)3 не применяются в

0 данной ВДО), Сигнал

F(5)4 S(a4) S(a5)

формирует разрешение на коммутаторы 8 и 9, обеспечивая прохождение сигнала ПРЗ на вход устройства.

5В группе 49 элементов управления шестым разрядом сигналы поступают на

третьи входы первогошестого элементов

И 50 (сигналы F(6)P. F(6)1F(6)4 не применяются в данной ВДО) Сигнал

F(6)5 S(a5) Щаб)

формирует разрешение на коммутаторы 8 и 9, обеспечивая прохождение на устройство тактовых сигналов ТИ (2) и информационных слов.

В группе 49 элементов управления седьмым разрядом сигналы поступают на третьи входы первогоседьмого элементов И 50 (сигналы F(7)PF(7)4, F(7)6 не применяются в данной В ДО). Сигнал

F(7)5 S(a5) S(a7)

формирует разрешение на коммутаторы 8 и 9, обеспечивая прохождение сигналов опорной частоты на вход счетчиков 80 для подсчета временного интервала т( а7 ).

В группе 49 элементов управления восьмым разрядом сигналы поступают на третьи

входы первоговосьмого элементов И 50

(сигналы F(8)P, F(8)1, F(8)3F(8)7 не применяются в данной В ДО). Сигнал

F(8) 2 S(a2) S(a8l

формирует разрешение на коммутаторы 8 и 9, обеспечивая прохождение сигналов опорной частоты на вход счетчиког 80 для подсчета величины временного интервала г(а8).

В группе 49 элементов управления девятым разрядом сигналы поступают на третьи входы первого,....девятого элементов И 50 (сигналы F(9)P,...,F(9)7 не применяются в данной В ДО). Сигнал

F(9)8 S(a8) Sfa9)

формирует разрешение на коммутаторы 8 и 9, обеспечивая прохождение сигнала ДА на объект контроля.

В группе 49 элементов управления десятым разрядом сигналы поступают на третьи входы первогодесятого элементов И 50 (сигналы F(10)P, F(10)1, F(10)3,...,F(10)9 не применяются в данной ВДО). Сигнал

F(10)2 S(a2)S(a10)

формирует разрешение на коммутаторы 8 и 9, обеспечивая прохождение сигналов опорной частоты на вход счетиков 80 для подсчета временного интервала г( аЮ ). .

В регистр 10 заносятся информационные слова задания кодов настройки на реализуемую временную диаграмму обмена, которые затем поступают по управляющим шинам на третий адресный выход блока 2 и далее по группе управляющих шин 147 - на управляющий вход коммутатора 9 принимаемых сигналов, а затем по управляющим шинам - на группы 52, 55, 58, 61,64, 66, 68, 70, 72 и 74 элементов коммутатора 9.

Для реализации ВДО необходимы следующие сигналы настройки.

В первую группу 52 элементов ИЛИ-И сигналы настройки поступают с выхода регистра 103 по первой управляющей шине на третий адресный выход блока 2 и далее по группе управляющих шин 147 на управляющий вход коммутатора 9 и по n-й линии на

второй вход п-го элемента И 53, разрешая прохождение информационного слова последовательным кодом с объекта контроля через коммутатор 9 на вход блока 4 сдвига данных.

0 В третью группу 58 элементов ИЛИ-И сигналы настройки поступают с управляющего входа коммутатора 9 по четвертой управляющей шине по линиям на вторые входы k-ro и 1-го элементов И 59 (k, |ЈМ; HI,

5 m 1-М), разрешая прохождение тактовых сигналов ТИ (1), ТИ (2). Фактическая величина k, I определяется по номерам линий, по которым идет обмен с ОК.

В первую группу 72 трехвходовых эле0 ментов И сигналы поступают с управляющего входа коммутатора 9 по пятой управляющей шине, по третьей и шестой линиям на третьи входы элементов И 73, разрешая прохождение тактовых сигналов

5 ТИ (1) (в интервале от второй до третьей контрольных точек по сигналу разрешения, поступающему с узла 46 формирования сигналов разрешения) и тактовых сигналов ТИ (2) (в интервале от пятой до шестой конт0 рольных точек по сигналу разрешения, поступающему с узла 46).

В четвертую группу 61 элементов ИЛИ- И сигналы настройки поступают с управляющего входа коммутатора 9 по седьмой

5 управляющей шине, по шестой линии на второй вход элемента И 62, разрешая прохождение тактовых сигналов ТИ (2).

Во вторую группу 66 элементов И сигналы поступают с управляющего входа комму0 татора 9 по восьмой управляющей шине, по третьей линии на второй вход элемента И 67, разрешая прохождение тактовых сигналов ТИ (1).

В группу 64 элементов И сигналы посту5 пают с управляющего входа коммутатора 9 по второй управляющей шине на вторые входы элементов И 65, разрешая прохождение информационное слова параллельным кодом с объекта контроля, через коммутатор

0 9 - на вход блока 4 сдвига данных (в указанной ВДО не применяется),

В группу 55 элементов ИЛИ-И сигналы настройки поступают с управляющего входа коммутатора 9 по третьей управляющей ши5 не на вторые входы элементов И 56, разрешая прохождение тактовых сигналов, выполняющих запись параллельного кода (в данной ВДО не применяется).

В группу 74 элементов И сигналы поступают с управляющего входа коммутатора 9

по шестой управляющей шине (по второй, четвертой, седьмой, восьмой, десятой линиям) на третьи входы элементов И 75, разрешая прохождение сигналов опорной частоты в интервалах следующих контроль- ных точек а1-а2; а2-з1; а5-а7; а2-а8 (по сигналам разрешения поступающим с узла 46 формирования сигналов разрешения).

В группе 68 элементов И сигналы настройки поступают с управляющего входа коммутатора 9 по девятой управляющей шине (по второй, четвертой, седьмой, восьмой и десятой линиям) на вторые входы элементов И 69, разрешая прохождение сигналов опорной частоты.

Второй этап (запуск устройства).

Из управляющей ЭВМ 95 в регистр 96 блока 2 выполняется запись кода признака цикла, устанавливающая разрешение на зацикливание. На выходе регистра 96 форми- руется сигнал Цикл, который поступает на выход признака цикла блока 2 и далее по управляющей линии 165 на вход цикла блока 3 управления циклом контроля, первый вход элемента И 12, разрешая прохождение сигнала Сброс-Цикл, поступающего на вход пуска блока 3.

В регистр 98 записывается первое передаваемое на ОК по ВДО информационное слово, которое поступает по информацией- ной шине на четвертый информационный выход блока 2 и далее по группе информационных и управляющих линий 151 на информационный вход блока 4 сдвига данных,

первые входы 1....J1-го элементов ИЛИ 83

группы 82 элементов ИЛИ и 1....J1-й входы J-разрядного сдвигающего регистра 81.

В регистре 96, кроме кода признака цикла , выполняется запись кода сигнала Запись 1, стробирующего запись инфор- мационного слова в регистр 81 блока 4. С выхода регистра 96 сигнал Запись 1 поступает по управляющей линии на четвертый информационный выход блока 2 и далее по группе информационных и управляющих линий 151 на информационный вход блока 4, по управляющей линии - на первый вход элемента ИЛИ 84. С выхода элемента ИЛИ 84 сигнал поступает на первый управляющий вход регистра 81. переводя регистр 81 в состояние Запись параллельного кода. Этот сигнал также поступает на вход формирователя 86. с выхода которого он передается на вход элемента ИЛИ 85 и далее на второй управляющий вход регистра 81, стробируя параллельную запись информационного слова.

В регистр 100 записывается информационное слово уставки, по которому на 1+1 - М выходе регистра 100 формируется

одиночная команда Разрешение, которая поступает на второй информационный выход блока 2. Далее по группе информационных линий 137 она поступает на первый информационный вход коммутатора 7 тактов, второй информационный выход коммутатора 7, вход разрешения записи блока 5 счетчиков тактов, информационные входы счетчиков 80, разрешая их работу при поступлении сигналов на их стробирующие входы. Кроме того, сигнал Разрешение поступает на вход переноса блока 6 формирования маски, вход переноса первого узла 10 фиксации маски, а также на 1+1-ю линию информационной шины информационного выхода блока 6. Далее по информационной шине 134 сигнал поступает на первый информационный вход коммутатора 8 тестов и на И 1-й вход узла 46 формирования сигналов разрешения.

Второй этап заканчивается (для указанной ВДО) подачей команды Пуск, приходящей от управляющей ЭВМ 95 и запускающей работу устройства.

В регистр 100 записывается информационное слово уставки, по которому на первом выходе регистра 100 формируется сигнал Пуск (сигнал Разрешение продолжает выдаваться). Сигнал Пуск по первой линии информационной шины, подключенной к второму информационному выходу блока 2, поступает по группе информационных линий 137 на первый информационный вход коммутатора 7, а по первой линии информационной шины - на первый вход элемента И 16 первой группы 15 элементов. Далее через элемент ИЛИ 25 первой группы 15 элементов сигнал поступает по первой линии первой управляющей шины на первый информационный выход коммутатора 7. На втором входе элемента И 16 в это время присутствует сигнал настройки на ВДО (в дальнейшем упоминание о сигналах настройки будет опускаться).

Третий этап (управление).

Третий этап продолжается от момента выдачи на объект контроля сигнала ЭТИ до выдачи следующего ЭТИ и циклически повторяется с новыми информационными словами.

Сигнал Пуск с первого информационного выхода коммутатора 7 тактов по первой линии управляющей шины группы управляющих шин 130 поступает на вход управления режимом блока б формирования маски, вход управления режимом первого узла 10 фиксации маски и далее по первой линии входа управления режимом узла 10 на вторые входы элементов И 87 и 88. Поскольку на вход переноса первого узла 10 подан

разрешающий сигнал Разрешение, то сигнал Брак (нарушение очередности в прохождении контрольных точек) на выходе элемента И 88 не формируется, а сигнал Пуск поступает на выход элемента И 82, первый вход элемента ИЛИ 90, установочный вход триггера 92, фиксируя факт выполнения первой контрольной точки а1. С выхода триггера 92 сигнал первой контрольной точки S(a1) (фиг.20) поступает на выход переноса первого узла 10 и вход переноса второго узла 10, разрешая прохождение сигнала контрольной точки а2„ Кроме того, сигнал S(a1) поступает на первый информационный выход узла 10, первую линию информационной шины информационного выхода блока 6, первый информационный вход коммутатора 8. Далее по первой линии информационной шины сигнал поступает на вход первого формирователя 28 импульсов группы 27 формирователей, вход первого элемента И 39 группы 38 элементов И. С выхода этого элемента импульс ый сигнал S(a1) поступает (как сигнал ПНО).на первую линию первой управляющей шины четвертого информационного выхода коммутатора 8, а далее по группе информационных и управляющих шин и линий 145 - на выход устройства и вход объекта контроля. Сигнал S(a1) поступает также на первые входы первых элементов И 30, 33, 36 групп 29, 32, 35 элементов. Однако на их выходы сигнал S(a1) не проходит, так как на эти элементы сигналы настройки не подавались. Сигнал S(a1) поступает на первый вход узла 46 формирования сигналов разрешения, первый вход второго элемента И 50 группы 45 элементов управления вторым разрядом и далее через элемент ИЛИ 51 на второй выход узла 46, формируя сигнал разрешения F(2)1, который поступает на первый информационный выход коммутатора 8. Далее по группе линий 127 сигнал поступает на первый информационный вход коммутатора 9, второй вход второго элемента И 75 группы 74 элементов И, разрешая прохождение сигналов опорной частоты на второй вход второго элемента ИЛИ 71 группы 70 элементов ИЛИ и третий информационный выход коммутатора 9. И наконец по группе тактовых линий 148 сигнал поступает на тактовый вход блока 5 счетчиков тактов и синхронизирующий вход второго счетчика 80. Второй счетчик 80, выполнив подсчет серии импульсов опорной частоты с заданным коэффициентом пересчета К2, формирует на своем выходе сигнал Конецт (а2). , который поступает на вторую линию информационного выхода блока 5 счетчиков тактов, третий информационный вход коммутатора 7 тактов и первый вход элемента И 18 второй группы 15 элементов.

С выхода элемента И 13 сигнал поступает на вход элемента ИЛИ 25, первый информационный выход коммутатора 7, вход управления режимом блока 6 и вход управления режимом второго узла 10, Далее сигнал поступает на второй вход элемента И 87, с выхода которого сигнал Конец т ( а2 ) поступает на первый вход элемента ИЛИ 90

и установочный вход триггера 92, фиксируя факт выполнения второй контрольной точки а2.

С выхода триггера 92 сигнал S(a2) поступает на выход переноса второго узла 10 и

5 вход переноса третьего узла 10, разрешая прохождениесигнала о выполнении третьей контрольной точки аЗ. Кроме того, сигнал поступает на первый информационный выход второго узла 10, вторую линию инфор0 мационной шины информационного выхода блока 6 и первый информационный вход коммутатора 8. С выхода коммутатора 8 он поступает по второй линии информационной шины на вход второго формирователя

5 28 импульсов группы 27 формирователей и вход второго элемента И 39 группы 38 элементов, с выхода которого импульсный сигнал S(a2) поступает ( как сигнал ЭТИ) на вторую линию первой управляющей шины

0 четвертого информационного выхода коммутатора 8. Далее по группе управляющих и информационных шин и линий 145 сигнал поступает на выход устройства и вход объекта контроля. Кроме того, сигнал S(a2) с первого

5 информационного входа коммутатора 8 по второй линии информационной шины поступает на второй вход узла 46, вход инвертора ,48 группы 47 инверторов, с выхода которого он подается на второй вход второ0 го элемента И 50 группы 49 элементов управления вторым разрядом, запрещая выдачу сигнала разрешения F(2)1 и прекращая подачу опорной частоты на вход второго счетчика 80 блока 5. Кроме того, сигнал

5 S(a2) с второго входа узла 46 поступает на первые входы вторых элементов И 50 групп 49 элементов управления третьим, четвертым, восьмым и десятым разрядами, формируя сигналы разрешения F(3)2; F(4)2; F(8)2;

0 F(10)2.

Сигнал F(3)2 с выходов элемента ИЛИ 51 и группы 49 элементов управления третьим разрядом поступает на третий выход узла 46, первый выход третьего элемента И 45

5 -группы 44 элементов И, разрешая на интер- вале времени между второй а2 и третьей эЗ контрольными точками прохождение информации в последовательном коде на вход объекта контроля. Кроме того, сигнал F(3)2

поступает по третьей линии на первый информационный выход коммутатора 8, первый информационный вход коммутатора 9. второй вход третьего элемента И 73 группы 72 элементов И, разрешая прохождение тактовых сигналов ТИ (1), поступающих с объекта контроля по группе управляющих и информационных шин и линий 128 на второй информационный вход коммутатора 9. Далее по второй управляющей шине сигнал поступает на группу 58 элементов ИЛИ-И и первый вход третьего элемента И 73. Сигналы ТИ (1) с выхода третьего элемента И 73 поступают на первый вход третьего элемента ИЛИ 71, третий информационный выход коммутатора 9, тактовый вход блока 5, синхронизирующий вход третьего счетчика 80, где выполняется подсчет их числа. Сигнал ТИ (1) также поступают на первый вход третьего элемента И 67 и вход элемента ИЛИ 76, с выхода которого они передаются на второй информационный выход коммутатора 9, стробирующий вход коммутатора 8, второй вход третьего элемента И 45 группы 44 элементов И, к третьему входу которого также подключен выход J-ro разряда сдвигающего регистра 81. При этом третий разряд передаваемого информационного слова по первому сигналу ТИ (1) поступает с выхода третьего элемента И 45 на третью линию второй информационной шины, четвертый информационный выход коммутатора 8, выход устройства и объект контроля. Кроме того, сигналы ТИ (1)с выхода элемента ИЛИ 76 поступают на вход элемента 79 задержки, элемент ИЛИ 77, вход управления записью блока 4 и сдвигающий вход регистра 81, обеспечивая сдвиг информационного слова (передаваемого на ОК последовательным кодом) на один разряд влево (после того, как крайний левый J-й разряд информационного слова будет передан). Временная диаграмма обмена достигает третьей контрольной точки аЗ, когда третий счетчик 80, выполнив подсчет серии импульсов ТИ (1)с заданным коэффициентом пересчета Кз. сформирует на своем выходе сигнал Конец ТИ (1). Этот сигнал поступает на информационный выход блока 5, третий информационный вход коммутатора 7, первый вход элемента И 18 третьей группы 15 элементов, элемент ИЛИ 25 и вход управления режимом блока 6. Далее сигнал передается на вход управления режимом третьего узла 10 и второй вход элемента И 87, с выхода которого сигнал Конец ТИ(1) поступает на элемент ИЛИ 90 и установочный вход триггера 92, фиксируя факт выполнения третьей контрольной точки аЗ.

После выполнения второй контрольной точки а2 на выходах узла 46, кроме сигнала F(3)2, были сформированы сигналы F(4)2; F(8)2: F(10)2, которые поступают на первый информационный выход коммутатора 8. Далее по группе линий 127 сигналы поступают на первый информационный вход коммутатора 9 и вторые входы четвертого, восьмого и десятого элементов И 75 группы 74 элементов И. На первые входы этих элементов поступают со стробирующего входа коммутатора 9 сигналы опорной частоты, которые с выходов четвертого, восьмого и десятого элементов И 75 поступают на вторые входы

5 четвертого, восьмого и десятого элементов ИЛИ 71 группы 70 элементов ИЛИ и третий информационный выход коммутатора 9. Далее по группе тактовых линий 148 они передаются на тактовый вход блока 5 и

0 синхронизирующие входы четвертого, восьмого и десятого счетчиков 80, которые выполняют подсчет величин временных интервалов F(a4), г ( а8 ) , г (аЮ ). .

Сигнал о выполнении третьей контроль5 ной точки S(a3) с выхода триггера 92 третьего узла 10 поступает на выход переноса и вход переноса четвертого узла 10, разрешая прохождение сигнала о выполнении четвертой контрольной точки. Кроме того, сигнал

0 поступает на первый информационный выход третьего узла 10, третью линию информационной шины информационного выхода блока 6 и первый информационный вход коммутатора 8. С выхода коммутатора 8 сиг5 нал поступает на третий вход узла 46, вход третьего инвертора 48 группы 47 инверторов и второй вход второго элемента И 50 группы 49 элементов управления третьим разрядом, запрещая подачу разрешающего

0 сигнала.

Четвертый счетчик 80, выполнив подсчет серии импульсов опорной частоты с заданным коэффициентом пересчета К4, формирует на своем выходе сигнал Конец

5- г ( а4 ). , который поступает на четвертую линию информационного выхода блока 5 счетчиков тактов, третий информационный вход коммутатора 7, первый вход элемента И 18 четвертой группы 15 элементов. С вы0 хода этого элемента сигнал Конец г (а4 ). поступает на элемент ИЛИ 25, первый информационный выход коммутатора 7, вход управления режимом блока 6 и вход управления режимом четвертого узла 10, Далее

5 сигнал поступает на второй вход элемента И 87, с выхода которого сигнал Конец т ( а4 ) поступает на первый вход элемента ИЛИ 90 и установочный вход триггера 92, фиксируя факт выполнения четвертой контрольной точки а4. С выхода триггера 92 сигнал S(a4) поступает на выход переноса четвертого узла 10 и вход переноса пятого узла 10, разрешая прохождение сигнала о выполнении пятой контрольной точки а5. Кроме того, сигнал S(a4) поступает на первый информационный выход четвертого узла 10, четвертую линию информационной шины информационного выхода блока 6 и первый информационный вход коммутатора 8, Затем он поступает по четвертой линии информационной шины на четвертый вход узла 46, вход четвертого инвертора 48 группы 47 инверторов и второй вход второго элемента И 50 группы 49 элементов управления четвертым разрядом, запрещая подачу разрешающего сигнала F(4)2. Временная диаграмма обмена достигает пятой контрольной точки а5, когда с объекта контроля приходит одиночная команда признака перезаписи {ПРЗ), которая поступает на вход устройства. Далее по группе управления информационных шин линий 128 сигнал n :тупает на второй информационный вход коммутатора 9, первый информационный выход коммутатора 9, третий информационный вход коммутатора 7 и первый вход элемента И 17 пятой группы 15 элементов. Далее сигнал ПРЗ поступает на элемент ИЛИ 25, первый информационный выход коммутатора 7, вход управления режимом блока 6, вход управления режимом пятого узла 10. Затем он передается на второй вход элемента И 87, первый вход элемента ИЛИ 90 и установочный вход триггера 92, фиксируя факт выполнения пятой контрольной точки а5. С выхода триггера 92 сигнал S(a5) поступает на выход переноса пятого узла 10 и вход переноса шестого узла 10, разрешая прохождение сигнала S(a6). Кроме того, сигнал S(a5) поступает на первый информационный выход пятого узла 10, пятую линию информационной шины информационного выхода блока 6, первый информационный вход коммутатора 8, откуда он поступает по пятой линии информационной шины на пятый вход узла 46. Затем сигнал передается на первые входы пятых элементов И 50 группы 49 элементов управления шестым и седьмым разрядами, а на шестом и седьмом выходах узла 46 формируются сигналы разрешения F(6)5; F(7)5.

Сигнал F(6)5 с выхода элемента ИЛИ 51 и группы 49 элементов управления шестым разрядом поступает на шестой выход узла 46, первый информационный выход коммутатора 8, первый информационный вход коммутатора 9 и второй вход элемента И 73 группы 72 элементов, разрешая прохождение тактовых сигналов ТИ (2), поступающих

5

0

5

0

5

0

5

0

5

с объекта контроля, на вход устройства. Далее по группе управляющих и информационных шин и линий 128 сигнал поступает на второй информационный вход коммутатора 9 данных, группу 58 элементов ИЛИ-И и первый вход шестого элемента И 73. Сигналы ТИ (2) с выхода шестого элемента И 73 поступают на первый вход шестого элемента ИЛИ 71 группы 70 элементов ИЛИ, третий информационный выход коммутатора 9, тактовый вход блока 5 и синхронизирующий вход шестого счетчика 80, где выполняется подсчет их числа. Сигналы ТИ (2) также поступают на первый вход шестого элемента И 62 группы 61 элементов ИЛИ-И, вход элемента ИЛИ 77, вход управления записью блока 4 и сдвигающий вход регистра 81, обеспечивая сдвиг информационного слова перед приемом очередного разряда, передаваемого с ОК последовательным кодом. Кроме того, сигналы ТИ (2) с выхода элемента ИЛИ 63 группы 61 элементов поступают на элемент 78 задержки, четвертый информационный выход коммутатора 9, вход управления записью блока 4, второй вход элемента ИЛИ 85 и стробирующий вход J- разрядного регистра 81, стробируя запись последовательного кода принимаемого информационного слова. Этот код поступает с выхода объекта контроля на второй информационный вход коммутатора 9 и один из N элементов И 53 (в зависимости от того, по какой из N линий первой информационной шины с ОКожидается приход информационного слова) группы 52 элементов ИЛИ-И. С выхода элемента ИЛИ 54 информационные сигналы по первой информационной линии поступают на четвертый информационный выход коммутатора 9, вход управления записью блока 4 сдвига данных, первый информационный вход регистра 81 (вход последовательного приема информации).

Временная диаграмма обмена достигает шестой контрольной точки аб, когда шестой счетчик 80, выполнив подсчет серии импульсов ТИ (2) с заданным коэффициентом пересчета Кб, сформирует на своем выходе сигнал Конец JH (2), который по шестой линии поступает на информационный выход блока 5. Далее сигнал поступает на третий информационный вход коммутатора 7, первый вход элемента И 18 шестой группы 15 элементов, проходит через элемент ИЛИ 25, поступает на первый информационный выход коммутатора 7, вход управления режимом блока 6, вход управления режимом шестого узла 10 и второй вход элемента И 87, с выхода которого сигнал Конец ТИ (2) поступает на элемент ИЛИ 90

переноса седьмого узла 10 и вход переноса

и установочный вход триггера 92, фиксируя факт выполнения контрольной точки аб.

Сигнал о выполнении шестой контрольной точки 5(аб) с выхода триггера 92 поступает на выход переноса шестого узла 10 и вход переноса седьмого узла 10, разрешая прохождение сигнала о выполнении седьмой контрольной точки а7. Кроме того, сигнал З(аб) поступает на первый информационный выход шестого узла 10, шестую линию информационной шины информационного выхода блока 6, первый информационный вход коммутатора 8, шестой вход узла 46. Затем он поступает на вход шестого инвертора 48 группы 47 инверторов и второй вход пятого элемента И 50 группы 49 элементов управления шестым разрядом, запрещая подачу разрешающего сигнала F(6)5.

Счетчик 80, выполнив подсчет серии импульсов опорной частоты с заданным коэффициентом пересчета К, формирует на своем выходе сигнал Конец г ( а7). который поступает на седьмую линию информационного выхода блока 5 счетчиков тактов, третий информационный вход коммутатора 7 и первый вход элемента И 18 седьмой группы 15 элементов. С выхода этого элемента сигнал Конец т( а7 ) поступает на элемент ИЛИ 25, первый информационный выход коммутатора 7. вход управления режимом блока 6 и вход управления режимом седьмого узла 10. Далее сигнал поступает на второй вход элемента И 87, с выхода которого сигнал Конец г ( а7 ) поступает на первый вход элемента ИЛИ 90 и установочный вход триггера 92, фиксируя факт выполнения седьмой контрольной точки. С выхода триггера 92 сигнал S(a7) поступает на выход

восьмого узла 10, разрешая прохождение сигнала о выполнении восьмой контрольной точки а8. Кроме того, сигнал S(a7) поступает на первый информационный выход седьмого узла 10, седьмую линию информационной шины информационного выхода блока 6, первый информационный вход коммутатора 8, откуда он поступает по седьмой линии информационной шины на седьмой вход узла 46, вход седьмого инвертора 48 группы 47 инверторов и второй вход пятого элемента И 50 группы 49 элементов управления седьмым разрядом, запрещая подачу разрешающего сигнала F(7)5.

Временная диаграмма обмена достига- ет восьмой контрольной точки а8, когда восьмой счетчик 80, выполнив подсчет серии импульсов опорной частоты с заданным коэффициентом пересчета Кв. сформирует

0

5

0

5

0

,.

на своем выходе сигнал Конец г ( а8 ) . который поступает на восьмую линию информационного выхода блока 5 счетчиков тактов. Далее по группе информационных линий 139 сигнал поступает на третий управляющий вход коммутатора 7 и первый вход элемента И 18 восьмой группы 15 элементов, с выхода которого сигнал Конец г ( а8 ) поступает на элемент ИЛИ 25, первый информационный выход коммутатора 7, вход управления режимом блока 6 и вход управления режимом восьмого узла 10. Далее он передается на второй вход элемента И 87, с выхода которого сигнал Конец т( а8) поступает на первый вход элемента ИЛИ 89 и установочный вход триггера 92, фиксируя факт выполнения восьмой контрольной точки а8. С выхода триггера 92 сигнал S(a8) поступает на выход переноса восьмого узла 10 и вход переноса девятого узла 10, разрешая прохождение сигнала о выполнении девятой контрольной точки а9. Кроме того, сигнал S(a8) поступает на первый информационный выход восьмого узла 10, восьмую линию информационной шины информационного выхода блока 6, первый информационный вход коммутатора 8. С выхода коммутатора он поступает по восьмой линии информационной шины на восьмой вход узла 46, вход восьмою инвертора 48 группы 47 инвертеров и второй вход второго элемента И 50 группы 49 элементов управления восьмым разрядом, запрещая подачу разрешающего сигнала F(8)2.

Кроме того, сигнал S(a8) с первого информационного входа коммутатора 8 поступает на вход восьмого формирователя 28 .импульсов группы 27 формирователей, первый вход восьмого элемента V 30 группы 29 элементов ИЛИ-И, вход элемента ИЛИ 31, с выхода которого сигнал Запрос ЭВМ поступает на третий информационный выход коммутатора 8 и вход признака приема данных блока 2 задания тестов и анализа реакций и записывается в разряд Запрос ЭВМ регистра 96.

Управляющая ЭВМ 95 в соответствии с алгоритмом (фиг.21) периодически считывает согласно типовому циклу чтения (фиг.18) содержимое регистра 96 и определяет наличие информации в разрядах Запрос ЭВМ и Брак регистра 96. В случае появления сигнала Брак, управляющая ЭВМ 95 выполняет чтение содержимого 1,...I....J-ro разрядов блока 6 формирования маски. Чтение выполняется следующим образом. В разряд ЧТС 1 регистра 96 записывается сигнал, который с выхода регистра 96 поступает на второй вход элемента ИЛИ 112 и вход

записи регистра 97, Содержимое 1,.,,,...1-го разрядов блока 6 поступает на информационный выход блока 6, первый информационный вход блока 2, второй вход модуля ИЛИ 114 и вход приема параллельной информа- ции регистра 97. Управляющая ЭВМ 95 считывает содержимое регистра 97, анализирует и распечатывает его содержание.

В случае появления сигнала Запрос ЭВМ (при отсутствии сигнала Брак) управляющая ЭВМ 95 (в соответствии с реализуемой ВДО) выполняет чтение содержимого 1,...j,...J-ro разрядов блока 4 сдвига данных. Чтение выполняется следу- ющим образом. В разряд регистра 96 записывается сигнал ЧТС 2, который с выхода регистра 96 поступает на второй вход элемента ИЛИ 113 и вход записи регистра 98. Содержимое 1,...j,...J-ro разрядов блока 4 поступает на информационный выход блока 4, второй информационный вход блока 2 и второй вход модуля ИЛИ 115. Далее сигнал поступает на вход приема параллельной информации регистра 98. Управляющая ЭВМ 95 считывает содержимое регистра 98, анализирует его и в соответствии с ВДО выдает на блок 2 сигнал ДА, который записывается в девятый разряд регистра 100 (с выхода которого сигнал поступает на второй инфор- мационный выход блока 2, первый информационный вход коммутатора 7, первый вход элемента И 16 девятой группы 15 элементов ИЛИ-И, вход элемента ИЛИ 25, первый информационный выход коммутатора 7, вход управления режимом блока 6, вход управления режимом девятого узла 10). Далее сигнал ДА поступает на второй вход элемента И 87, с выхода которого (через элемент ИЛИ 90) он подается на установочный вход триггера 92, фиксируя факт выполнения девятой контрольной точки а9. С выхода триггера 92 сигнал S(a9) поступает на выход переноса девятого узла 10 и вход переноса десятого узла 10, разрешая прохождение сигнала о выполнении десятой контрольной точки аЮ. Кроме того, управляющая ЭВМ 95 выполняет запись в блок 4 сдвига данных нового информационного слова, которое будет передано на объект контроля на следу- ющем цикле обмена. Сигнал S(a9) поступает на первый информационный выход девятого узла 10, девятую линию информационной шины информационного выхода блока 6, первый информационный вход коммута- тора 8, вход девятого формирователя 28 импульсов группы 27 формирователей и вход девятого элемента И 39 группы 38 элементов И. С выхода этого элемента импульсный сигнал S(a9) поступает на девятую линию

первой управляющей шины четвертого информационного выхода коммутатора 8. выход устройства и вход объекта контроля.

Временная диаграмма обмена достигает, десятой контрольной точки аЮ, когда десятый счетчик 80, выполнив подсчет серии импульсов опорной частоты с заданным коэффициентом пересчета Кю, сформирует на своем выходе сигнал Конец т( а10 ) , который поступает на десятую линию информационного выхода блока 5 счетчиков тактов. Далее по группе информационных линий 139 сигнал поступает на третий информационный вход коммутатора 7, первый вход элемента И 18 десятой группы 15 элементов. С выхода этого элемента сигнал Конец т( аЮ ) поступает на элемент ИЛИ 35, первый информационный выход коммутатора 7, вход управления режимом блока 6 и вход управления режимом десятого узла 10. Далее сигнал поступает на второй вход элемента И 87, с выхода которого сигнал Конец т (аЮ) поступает на первый вход элемента ИЛИ 90 и установочный вход триггера 92, фиксируя факт выполнения десятой контрольной точки аЮ.

С выхода триггера 92 сигнал S(a10) поступает на первый информационный выход десятого узла 10, десятую линию информационной шины информационного выхода блока 6, первый информационный вход коммутатора 8, где он поступает по десятой линии информационной шины на десятый вход узла 46, вход десятого инвертора 48 группы 47 инверторов и второй вход второго элемента И 50 группы 49 элементов управления десятым разрядом, запрещая подачу разрешающего сигнала )2.

Кроме того, сигнал S(a10) поступает с первого информационного входа коммутатора 8 на вход десятого формирователя 28 импульсов группы 27 формирователей, вход десятого элемента И 33 группы 32 элементов ИЛИ-И, вход элемента ИЛ И 34, С выхода этого элемента сигнал Сброс-Цикл поступает на второй информационный выход коммутатора 8 и вход пуска блока 3 управления циклом контроля. В случае, если на входе элемента И 12 блока 3 присутствует сигнал Цикл, поступающий с выхода регистра 96 блока 2 и разрешающий циклическую работу устройства, сигнал Сброс - . Цикл поступает на выход элемента И 12. Далее он передается на формирователь 13 импульса, поступает (уже как сигнал ЦСб - циклический сброс) на выход блока 3, стро- бирующий вход коммутатора 7 и первые входы элементов И 24 второй - десятой групп 15 элементов. Далее по третьим лини

ям второй - десятой управляющих шин первого информационного выхода коммутатора 7 сигнал ЦСб поступает по группе управляющих шин 130 на вход управления режимом блока б, входы управления режимом второго - десятого узлов 10 фиксации маски, первые входы элементов ИЛИ 91 и сбросовые t ходы триггеров 92 второго - десятогоузлов 10, обеспечивая выборочный сброс содержимого блока 6 и подготавливая бго к выполнению очередного цикла обмена с ОК. Кроме того, с выхода формирователя 13 импульса блока 3 сигнал ЦСб поступает на элемент 14 задержки, где задерживается на время, достаточное для сброса триггеров 92 узлов 10 блока 6. С выхода элемента 14 задержки сигнал ЦПу (циклический пуск) поступает по первой линии на выход блока 3, стробирующий вход коммутатора 7, первый вход элемента И 19 второй группы 15 элементов ИЛИ-И. Далее он передается на элемент ИЛИ 25. с выхода которого сигнал ЦПу поступает по первой линии второй управляющей шины на первый информационный выход коммутатора 7, вход управле- ния режимом блока 6, вход управления режимом второго узла 10 и второй вход элемента И 87, с выхода которого он поступает на вход элемента ИЛИ 90 и установочный вход триггера 92, фиксируя факт выполнения второй контрольной точки.

Формула изобретения

1. Устройство для контроля цифровых блоков, содержащее генератор импульсов, блок задания тестов и анализа реакций, блок управления циклом контроля и блок сдвига данных, отличающееся тем, что, с целью расширения функциональных воз- можностей путем реализации универсальных диаграмм контроля, оно содержит блок счетчиков тактов, блок формирования маски, коммутатор тактов, коммутатор тестов и коммутатор данных, первый информацион- ный вход которого соединен с первьни информационным выходом коммутатора тестов, второй информационный вход коммутатора данных является входом устройства для подключения к выходу обьекта контроля, информационный вход, вход управления режимом, вход переноса, вход начальной установки, выход признака ошибки и информационный выход блока формирования маски подключены соответственно к первому информационным выходу блока задания тестов и анализа реакций, первому и второму информационному выходам коммутатора тактов, выходу начальной установки, входу признака ошибки и первому информационному входу блока задания тестов и анализа реакций, управляющий и стробирующий входы, первый, второй и третий информационные входы коммутатора тактов соединены соответственно с первым адресным выходом блока задания тестов и анализа реакций, выходом блока управления циклом контроля, вторым информационным выходом блока задания тестов и анализа реакций, первым информационным выходом коммутатора данных и информационным выходом блока счетчиков тактов, управляющий вход, первый и второй информационные входы, стробирующий вход, второй и третий информационные выходы коммутатора тестов подключены соответственно к второму адресному выходу блока задания тестов и анализа реакций, информационным выходам блока формирования маски и блока сдвига данных, второму информационному выходу коммутатора данных, входу пуска блока управления циклом контроля и входу признака приема дан- ных б/юка задания тестов и анализа реакций, четвертый информационный выход коммутатора тестов является выходом устройства для подключения к входу обьекта контроля, стробирующий и управляющий входы, третий и четвертый информационные выходы коммутатора данных соединены соответственно с выходом генератора импульсов, третьим адресным выходом блока задания тестов и анализа реакций, тактовым входам блока счетчиков тактов и входам управления записью блока сдвига данных, вход разрешения записи, вход сброса и информационный вход блока счетчиков тактов подключены соответственно к второму информационному выходу коммутатора тактов, выходу начальной установки и третьему информационному выходу блока задания тестов и анализа реакций, вход сброса, информационные вход и выход блока сдвига данных соединены соответственно с выходом начальной установки, четвертым информационным выходом и вторым информационным входом блока задания тестов и анализа реакций, выход признака цикла которого подключен к входу цикла блока управления циклом контроля.

2. Устройство поп.1,отличающее- с я тем, что блок формировлния маски содержит i узлов фиксации маски и элемент ИЛИ, выход переноса 1-го узла фиксации маски (1 l i-1) соединен с входом переноса (i+1)-ro узла фиксации маски, вход переноса первого узла фиксации маски соединен с входом переноса блока и подключен к старшему разряду информационного выхода блока, вход управления режимом, информационный вход, вход начальной установки, первый и второй информационные выходы 1-го узла фиксации маски соединены соответственно с входомуправлениярежимом, информационным входом и входом начальной установки блока, 1-м разрядом информа- ционного выхода блока и 1-м входом элемента ИЛИ, выход которого является выходом признака ошибки блока.

0

3. Устройство поп.1,отличающее- с я- тем, что блок управления циклом контроля содержит элемент И, формирователь импульсов и элемент задержки, вход которого соединен с выходом формирователя импульсов, первый и второй входы и выход элемента И подключены соответственно к входу пуска и входу цикла блока и входу формирователя импульсов, а выходы формирователя импульсов и элемента задержки образуют выход блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для контроля параметров | 1985 |

|

SU1255996A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Устройство для диагностирования цифровых блоков | 1988 |

|

SU1631546A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для диагностики неисправностей логических блоков | 1987 |

|

SU1520548A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля цифровых устройств, в системах управления технологическими процессами, в частности, в устройствах, осуществляющих обмен между ЭВМ и объектами контроля и управления. Целью изобретения является расширение функциональных возможностей за счет реализации универсальных диаграмм контроля. Устройство содержит генератор импульсов, блок задания тестов и анализа реакций, блок управления циклом контроля, блок сдвига данных, блок счетчиков тактов, блок формирования маски, коммутатор тактов, коммутатор тестов, коммутатор данных. 2 з.п. ф-лы, 21 ил.

Фа I

)-я линия

/37

1-я линия

т

735

Ш

1-я инф.

ШиНА

/30

-

инф.

НАША

J

Фиг.Ь

Г

Uf.

1-ЯУЧ.

ишна

т

Z /iwn шина.

tt-Jt УМ шинл2-я 0v ишна

1

r-i29

з;

Запрос ЭВН

Ь I.

зГ|

Сброс-цикл

Я0

4ir

j 38

Одиночны, команды но ОК

№

Фиг. 5

Паоал.

1-9 упр. шина;

инф.

fa цнфмфгф

-145

Фиг.В

; 1-я инф. шина

12В

2-я инф. шина

1-я упр. шина

,шина

1384

1-я gnu шина

Щ1

j-я цпр. шина

.шйно 9-ЯУлдщжа|

Ц

„ 1

&

1-я инф. линия .. N

И

53

/

6Ь

J-я инф шина

-

55

№

1-я упр. линия

2-я упо. лип.

Фиг.в

Г

rXza

Ш

CAOZ991

FU 10

u

m

,0 fcc

(О

u 1

г

Г5

Го

Ј

(О

э

cvi

€

M

Ј

s ё- ся э§ 1

« аао з§ 3.

г4

I

5 э,, о g3.g S «-

d -с ф к Б ь S

3 Ь а а

н« t

1 I

|||||

l|3a|«

iHlfe

Stxu &S%S33

. f9

Сигналы на Ьнутр. Сигналы Ьлоки у-вонц ок

Фиг, 20

| Авторское свидетельство СССР № 1161934, кл G 06 F 13/00,1985 | |||

| Устройство для обмена управляющей ЭВМ с объектами контроля | 1983 |

|

SU1128243A2 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1987-09-08—Подача