инверсные и вторые прямые выходы регистров являются соответственно первыми, вторыми и третьими выходами блока памяти.

4. Устройство ПОП.1, ОТЛИЧв

ю щ е е с я тем, что формирователь адреса записи содержит элементы И и элементы НЕ, выход каждого предьщущего элемента И соединен через соответствукнций элемент Нь с соответствунмцими первыми входами всех последуюйщх элементов. И, первый вход первого элемента И и вторые входы последующих элементов И объединены и являются первым входом формирователя адреса записи, второй вход первого элемента И и третьи входы последующих элементов И объединеныи являются вторым входом формирователя адреса записи, третий вход первого элемента И является третьим входом формирователя адреса записи, выходы элементов И являются выходами форми- рователя адреса записи.

5. Устройство по П.1, о т л и чающееся тем, что выходной блок содержит первый- и вторые элементы И, выход первого элемента И соединен с первыми входами вторых элементов И, вторые входы вторых элементов И и входы первого элемента И являются соответственно первыми и вторыми входами выходного блока, выходы вторых элементов И и выход первого элемента И являются соответственно первыми и вторым выходами выходного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1996 |

|

RU2107995C1 |

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1983 |

|

SU1142825A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Устройство для передачи дискретной информации в кольцевом канале связи | 1989 |

|

SU1795497A1 |

| Устройство для преобразования широтно-импульсных сигналов в кодоимпульсные сигналы | 1986 |

|

SU1381701A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

| СИСТЕМА СЕАНСНОЙ СВЯЗИ | 1992 |

|

RU2027312C1 |

| Устройство контроля интегральных схем | 1986 |

|

SU1370634A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1984 |

|

SU1156110A1 |

1. УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ, содержащее приемник, первый вход которого является входом устройства, выход приемника соединен с первым входом ре;гистра, первый выход которого соединен с первым входом формирователя адреса записи, блок памяти, первые выходы которого- соединены с соответствующими первыми входами выходного блока первые выходы выходного блока являются выходами устройства, хронизатор и блок управления, отличающееся тем, что, с целью повышения пропускной способности устройства, в него введен пороговый блок, первый и вторые выходы регистра соединены соответственно с первыми и вторыми .входами порогового блока и блока управления, выход блока управления соединен с третьим входом порогового блока, выход которого соединен с вторым входом формирователя адреса записи, выходы и .третьи входы формирователя адреса записи соединены соответственно с первыми входами и вторыми выходами блока памяти, третьи выходы блока памяти - с соответствующими вторыми входами выходного блока и четвертыми входами порогового блока, второй . выход выходного блока соединен с входом хронизатора, первые выходы хронизатора соединены соответственно с вторыми входами регистра и блока памяти, второй выход хронизатора соединен с вторым входом приемника и третьим входом блока управления, третий выход хронизатора соединен с третьим входом блока памяти. 2.Устройство ПОП.1, отличающееся тем, что,блок управления содержит злемент И и триггер, выход элемента И соединен с входом установки в О триггера, первый и вторые входы элемента И являются соответственно первым и вторыми входами блока управления, объединенные третий вход элемента И и вход уста- : ,новки в 1 триггера являются третьим входом блока управления, выход триггера является выходом блока управления.. 3,Устройство но П.1, отличающееся тем, что блок памяти содержит .группы элементов И и регистры, инверсный выход каждого регистра соединен с первыми входами элементов И соответствующей группы, выходы которых соединены с управляющими входами соответствукмцего регистра,, информационные входы регистров являются первыми входами блока памяти, вторые входы групп элементов И объединены соответственно и являются вторыми входами блока памяти, тактовые входы регистров объединены и являются третьим входом блока .памяти, первые .

Изобретение относится к области передачи данных и может быть использовано в устройствах, обеспечивающих прием цифровых данных из моноканала локальной вычислительной сети.

Известно устройство для приема информации, содержащее приемник, xjjoнизатор, коммутаторы, мультиплексоры, декадеры, регистры, счетчики, блоки памяти, блоки управления и генера тор l .

Наиболее близким к предлагаемому по технической сущности является устройство для приема дискретной информации, содержащее приемник, вход которого }Гвллется первым входом устройства, первый выход соединен с первым входом блока управления, второй выход - через блок выборки - с первьм входом регистра, а третий выход - с вторьш входом регистра, первый и второй выходы регистра соединены с первыми входаш соответственно блока памяти и формирователя адреса записи, первый и второй выходы формирователя адреса записи.- с первыми входами соответственно переключателя и блока анализа состояний памяти, первый и второй выходы блока анализа состояний памяти - соответственно с первым входом формирователя адреса считывания

и вторым входом формирователя адреса записи, первый и второй выходы формирбвателя адреса считывания - с вторичными входами соответственно блока анализа состояний памяти и переключателя, третий вход переключателя соединен с выходом блока управления, а вькод - с вторым входом блока памяти выход блока памяти соединен с первым входом выходного блока, выход которого является выходом устройства, вторые входы блока управления, формирователя адреса считывания и выходного блока объединены и являются вторым входом устройства 2.1.

Недостатком известных устройств является отсутствие возможности rpjTiпового декодирования сообщений и азативной настройки на поле адресов сообщений в зависимости от объема принятой информации, что снижает пропускную способность устройства.

Цель изобретения - повьшение пропускной способности устройства.

Указанная цель достигаетсятем, что в устройство для приема дискретной информации, содержащее приемник, первый вход которого является входом устройства, выход приемника соединен с первым входом регистра, первый выход которого соединен с первым входом формирователя адреса записи, блок памяти, первые выходы которого соединены с соответствующими первыми входами ВЙ1ХОДНОГО блока, первые вы- ходы выходного блока являются выхода ми устройства, хронизатор и блок управления, введен пороговый блок, первый и вторые выходы регистра соединены соответственно с первыми и вторыми входами порогового блока и блока управления, выход блока управления соединен с третьим входом порогового блока, выход которого соединен с вторым входом формирователя адреса записи, выходы и третьи входы формирователя адреса записи соединены соответственно с первыми входами и вторыми выходами блока памяти, третьи выходы блока памяти - с соответ- ствующими вторыми входами выходного блока и четвертыми входами порогового блока, второй выход выходного блока соединен с входом хронизатора, первые выходы хронизатора соединены соответственно с вторыми входами регистра и блока памяти, второй выход хронизатора соединен с вторым входом приемника и третьим входом блока управления , третий выход хронизатора соединен с третьим входом блока па-. мяти.

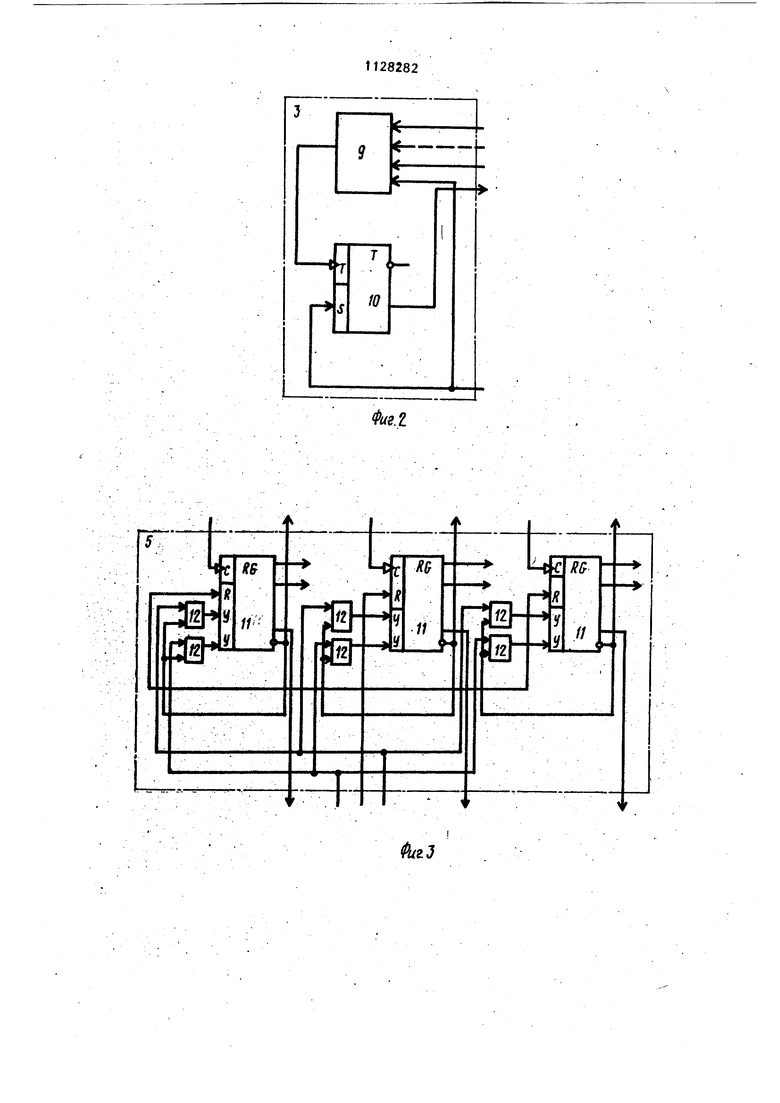

Кроме того, блок управления содержит элемент И и триггер, выход элемента И соединен с входом установки в О триггера, первый и вторые входы элемента И являются соответственно первым и вторыми входами блока управления, объединенные третий вход элемента И и вход установки в 1 триггера является третьим входом бло ка управления, выход триггера является выходом блока управления.

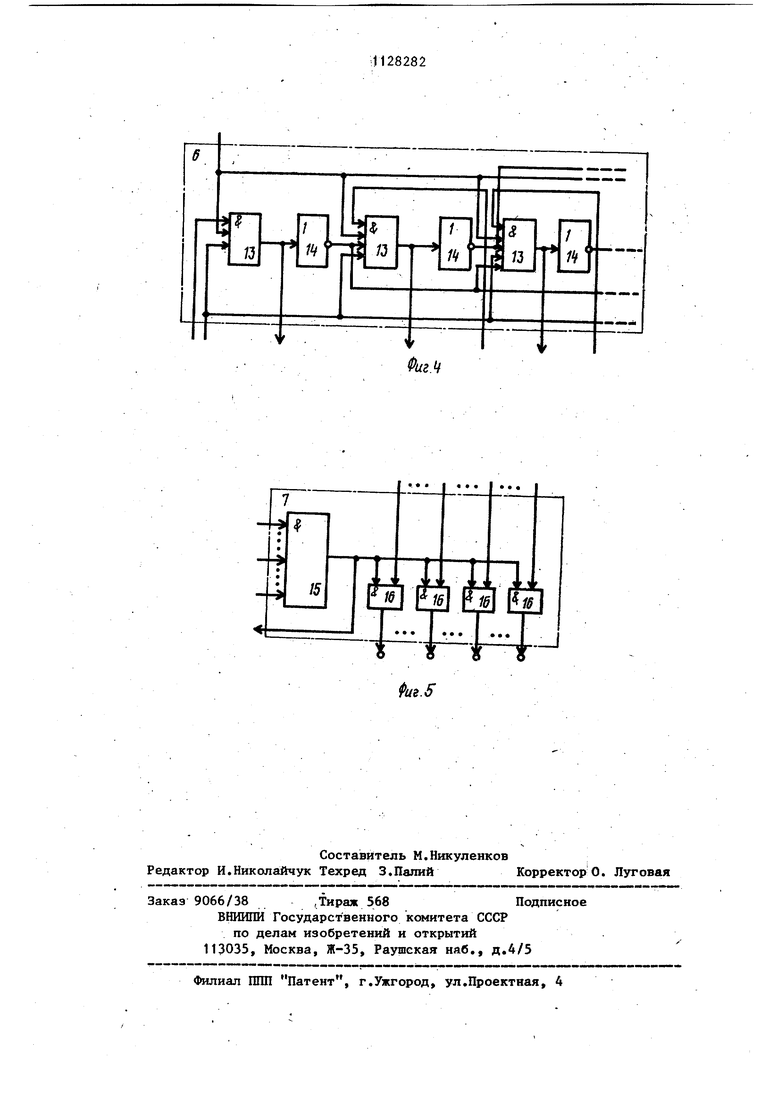

Блок памяти содержит группы элементов И и регистры, инверсный выход каждого регистра соединён с первыми входами элементов И соответствующей группы, выходы которых соединепы с . управляющими входами соответствующего регистра, информационные входы регистров являются первыми входами блока памяти, вторые входы rpynti элементов И объединены соответственно и являются вторыми входами блока памяти, тактовые входы регистров объёдит иены и являются третьим входом блока памяти, первые прямые, инверсные и вторые прямые выходы регистров яв пяются соответственно первыми, вторыми и третьими выходами блока памяти.

Формирователь адреса записи содерт жит элементы И и элементы НЕ, выход каждого предьщущего элемента И соединен через соответствующий .элемент НЕ с соответствующими первыми входами всех поЬледующих элементов И, первый вход первого элемента И и вторые входы последующих элементов И объединены и являются первым входом формирователя адреса записи, второй вход первого элемента И и третьи входы последующих элементов И объединены и являются вторым входом формирователя адреса записи, третий вход первого элемента И является третьим входом формирователя адреса записи, выходы элементов И являются выходами формирователя адреса записи.

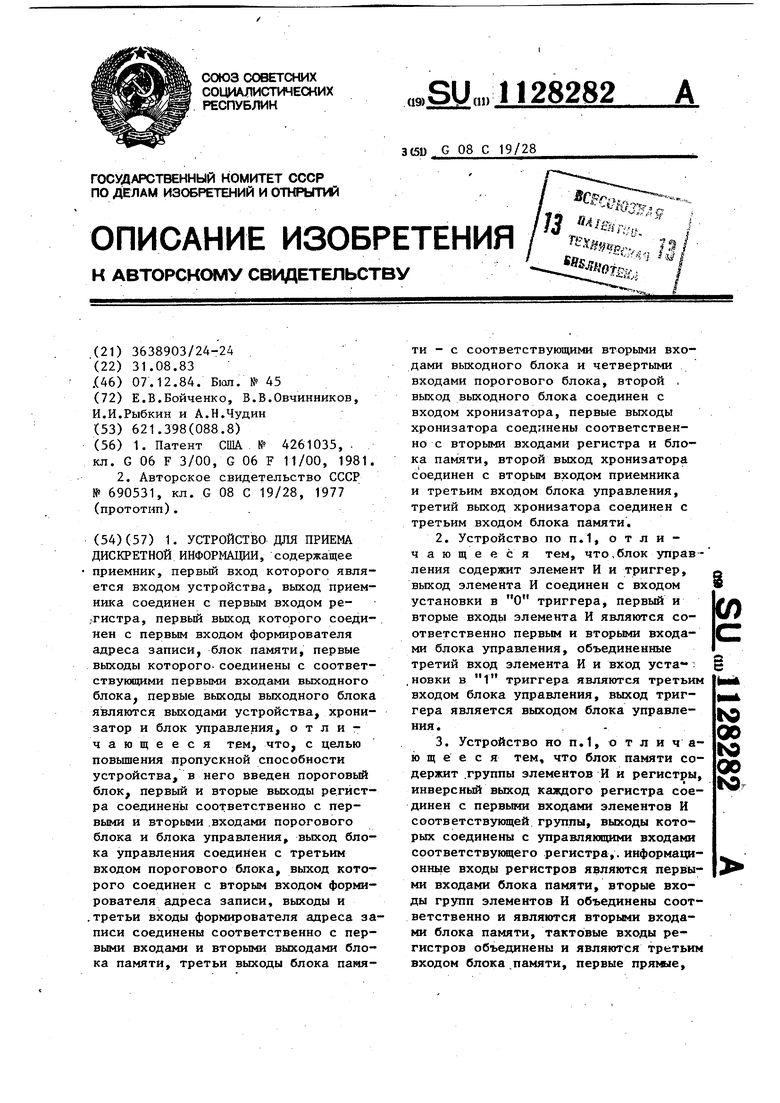

При этом выходной блок содержит первый и вторые элементы И, выход первого И соединен с первыми входами вторых элементов И, вторые входы вторых элементов И и входы первого элемента И являются соответственно первыми и вторыми входами выходного блока, выходы вторых элементов И и выход первого элемента И являются соответственно первыми и вторым выходами выходного блока.

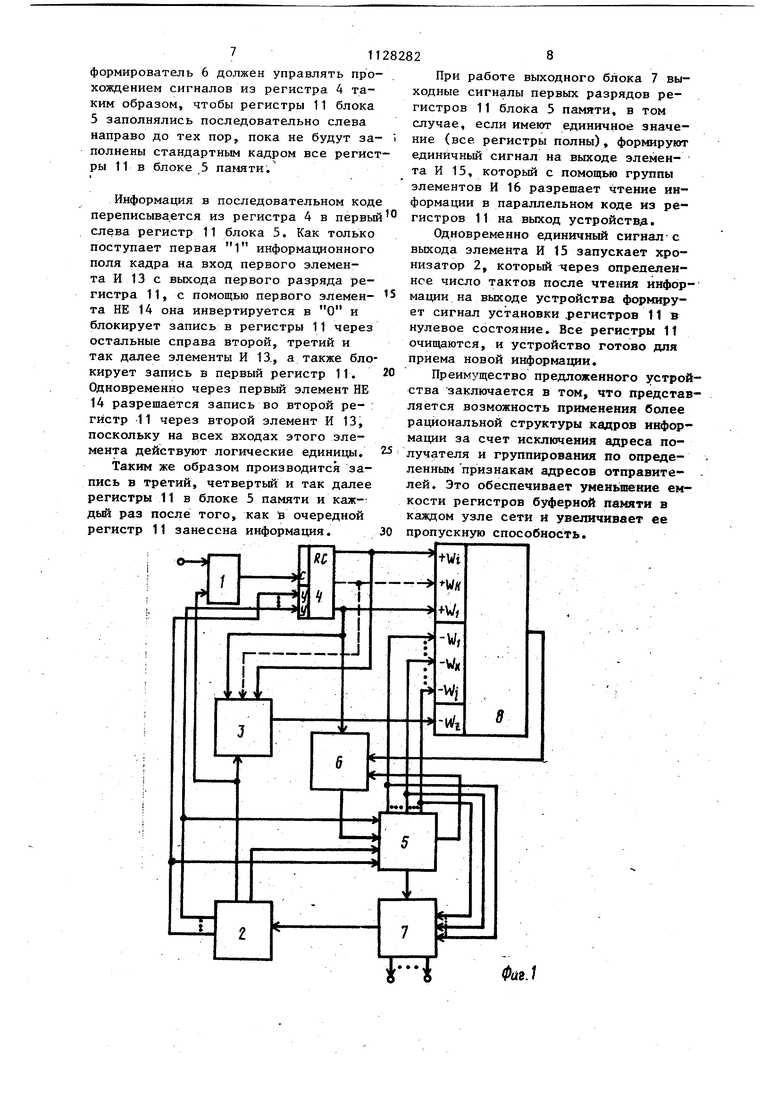

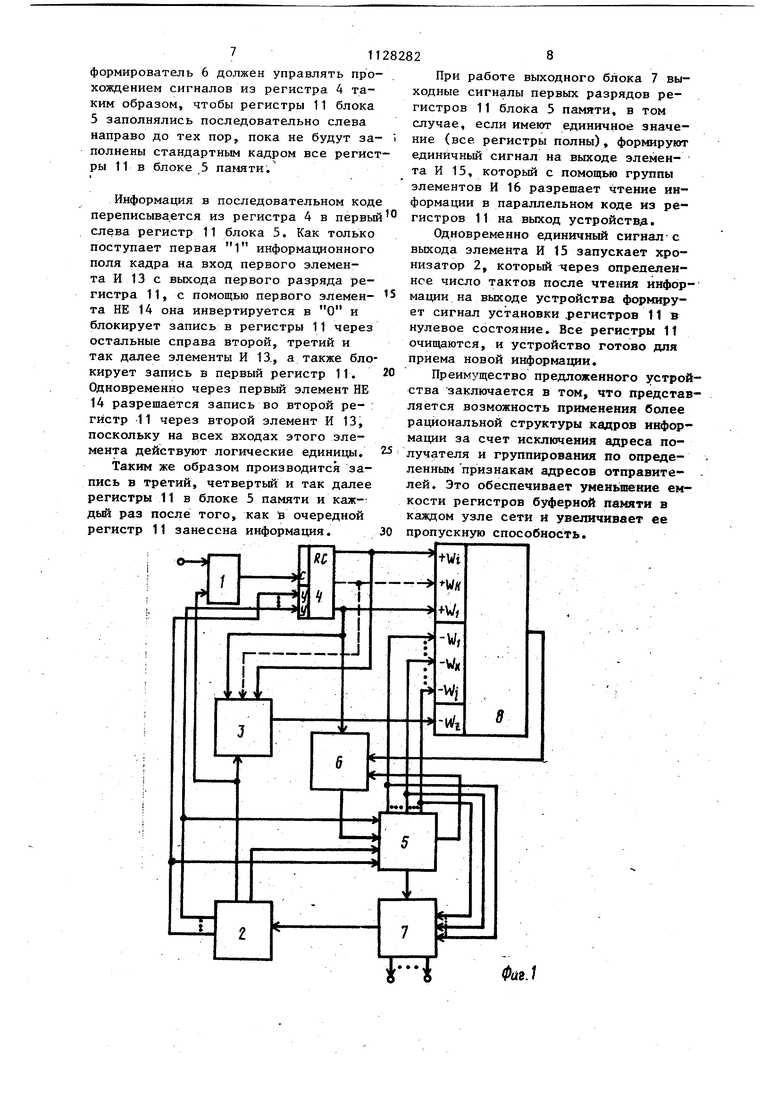

На фиг.1 показана структурная схема устройства для приема дискретной : информации: на фиг.2 - функциональная схема блока управления} на фиг.З - :; функциональная схема блока памяти на - функциональная схема формирователя адреса записи на фиг.З ункциональная схема выходного блока.

Устройство для приема дискретной нформации содержит приемник 1 (элеент И), хронизатор 2, блок 3 управения, регистр 4, блок 5 памяти, форирователь б адреса записи, выходкой лок 7 и пороговый блок 8.

. Бпок 3 управления содержит элемент И 9 и триггер 10, блок 5 памя--: ти-регистры 11 и элемент И 12, форми- 6 адреса записи - элементы И 13 и элементы НЕ 14, а выходной блок 7 - элементы И 15 и 16,

Устройство работает следующим образом.

На вход приемника 1 после разрешающего сигнала с выхода хронизатора 2 принимается последовательно бит за битом информация в форме кадра. Кадр в соответствии с международшш ставдартом HDliC включает в себя следующие поля двоичных комбинаций: открывающего флага (комбинация 01111110), адреса отправителя, информации отправителя, содержащей обязательно в первых трех разрядах избыточные три единицы, контрольной комбинации и заключающего флага.

Как только принят открывающий флаг, он записывается ю информацион-Ю

ному входу в регистр 4 сдвига, где сдвиг информации осуществляется под управлением вьщаваемых с тактирующих выходов хронизатора 2 сигналов сдвига. При появлении в регистре 4 комбинации флага срабатывает блок 3 управления. Комбинация флага в регистре 4 переключает злемент И 9 при условии действия разрещакщего сигнала с выхода хронизатора 2, одновременно устанавливакицего в исходное состояние 1 триггер 10. Импульс, сформированный элементом И 9, переключает триггер 10 в состояние О. Выход триггера 10 подключен к входу порогового блока 8 с максимальным отрицательным, весом - W« , таким, что при любых входных комбинациях блок 8 закрыт. При установке триггера 10 в состояние О производится переключение устроит ства в рабочее положение групповой выборки адресов. Работа блока 8 описьшается следующим алгоритмом: блок 8 переключается в состояние ,1 в том случае, если 2Wix; Tэ | A ilXj) блок 8 находится в состоянии О если EW;x; VS/ W,)xf, где W ,Wj - вес соответствующего 1 или } входа блока 8, причем Wj - положительные веса, а WJ -. отрицательные веса входов блока 81 Т, - целое значение фиксированного порога переключения блока 8. Как только в регистре 4 появляется комбинация адреса, она взвешивается с учетом суммарного веса положительных и отрицательных весов. Еели эта комбинация удовлетворяет первому уравнению, то блок 8 разрешает запись из регистра 4 в регистр 11 через .элемент И 13.

Таким образом, выполняется первая функция - декодирование не одного адреса, как в известном устройстве, а группы адресов отправителей в устройстве для приема дискретной информации.

При дальнейшей работе блока 5 паформация с отсеченными открывающим флагом и адресом, имеющая в первых трех разрядах 1,- через соответствующий злемент И 13 поступает на информационный вход С регистра 11 сдвига, управляемого с помощью тактирующих сигналов. Эта информация постепенно заполняет регистр 11 и после записи в него на выходе первого .размяти, продвигаясь по регистру 4, инряда появляется 1, а на инверсном выходе - О. Сигнал логического нуля с инверсного выхода регистра 11 подается на вход элемента И 13 формирователя 6 и блокирует дальнейшую запись информации в данный регистр 11. Одновременно этот сигнал блокирует с помощью элементов И 12 подачу с выходов хронизатора 2 тактирующю сигналов сдвига и тем самым фиксиру- ет информацию в данном регистре 11. Прямой выход первого разряда этого регистра 11 формирует единичный сигнал и передает его на соответствующий весовой вход порогового блока 8. Согласно первому уравнению величина порога увеличивается и блок 8 перестраивается на новое поле, комбинаций адресов с учетом того, что один регистр 11 заполнен. Если заполнен второй регистр 11, то происходит новая перестройка и т.д. Тем самым вьтолняется вторая функция, отсутствгующая в известном устройстве - адаптация с автоматической настройкой на поле адресов отправителей в зависимости от объема принятой информации. Как только очередной регистр 11 заполнен, на его прямом выходе перво- го разряда появляется сигнап лЬгич4ской единицы, который поступает на вход элемента И 15 в выходном блоке 7 устройства. Поясним работу формирователя 6 адреса записи. Предположим, что в исходном состоянии блок 5 памяти свободен, т.е. регистры 11 блока 5 свободны. При зтом формирователь 6 должен управлять прохождением сигналов из регистра 4 таким образом, чтобы регистры 11 блока 5 заполнялись последовательно слева направо до тех пор, пока не будут заполнены стандартным кадром все регист ры 11 в блоке 5 памяти. Информация в последовательном коде переписывается из регистра 4 в первый слева регистр 11 блока 5, Как только поступает первая 1 информационного поля кадра на вход первого элемента И 13 с выхода первого разряда регистра 11, с помощью первого элемента НЕ 14 она инвертируется в О и блокирует запись в регистры 11 через остальные справа второй, третий и так далее элементы И 13., а также блокирует запись в первый регистр 11. Одновременно через первый элемент НЕ 14 разрешается запись во второй регистр 11 через второй элемент И 13, поскольку на всех входах этого элемента действуют логические единицы. Таким же образом производится запись в третий, четвертый и так далее регистры 11 в блоке 5 памяти и каждый раз после того, как и очередной регистр 11 занесена информация. При работе выходного блока 7 выходные сигналы первых разрядов регистров 11 блока 5 памяти, в том случае, если имеют единичное значение (все регистры полны), формируют единичный сигнал на выходе элемента И 15, который с помощью группы элементов И 16 разрешает чтение информации в параллельном коде из регистров 11 на выход устройствд. Одновременно единичный сигнал-с выхода элемента И 15 запускает хронизатор 2, который через определеннее число тактов после чтения информации на выходе устройства формирует сигнал установки .регистров 11 в нулевое состояние. Все регистры 11 очищаются, и устройство готово для приема новой информации. Преимущество предложенного устройства заключается в том, что представляется возможность применения более рациональной структуры кадров информации за счет исключения адреса получателя и группирования по определенным признакам адресов отправителей. Это обеспечивает уменьшение емкости регистров буферной памяти в каждом узле сети и увеличивает ее пропускную способность.

KB

Чс

El

//

Ш

Т iO

--t

Rl

12

11

fl

12

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4261035, | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для приема кодовой информации | 1977 |

|

SU690531A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| . | |||

Авторы

Даты

1984-12-07—Публикация

1983-08-31—Подача