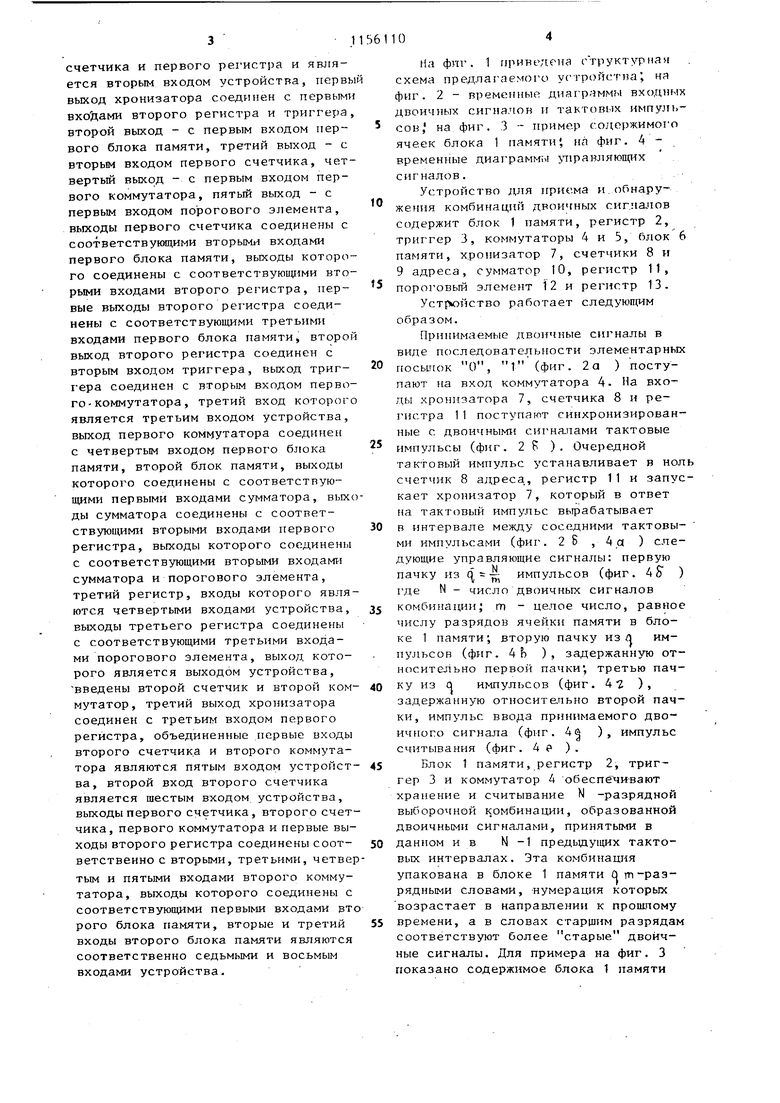

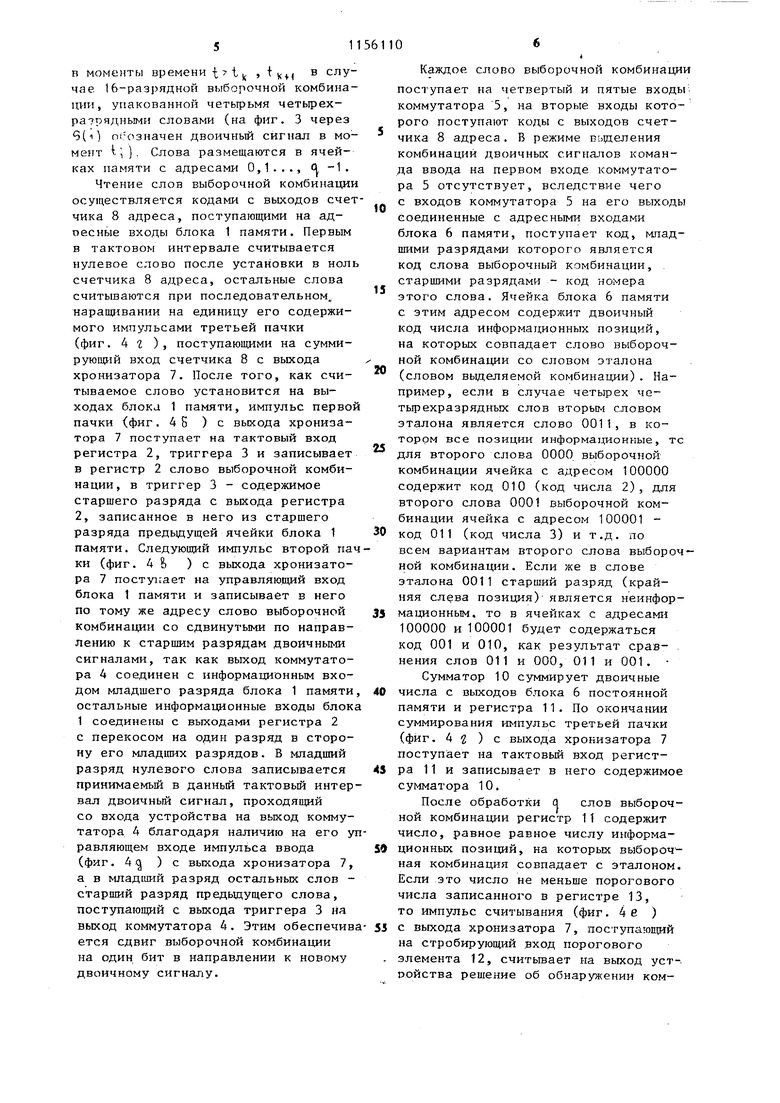

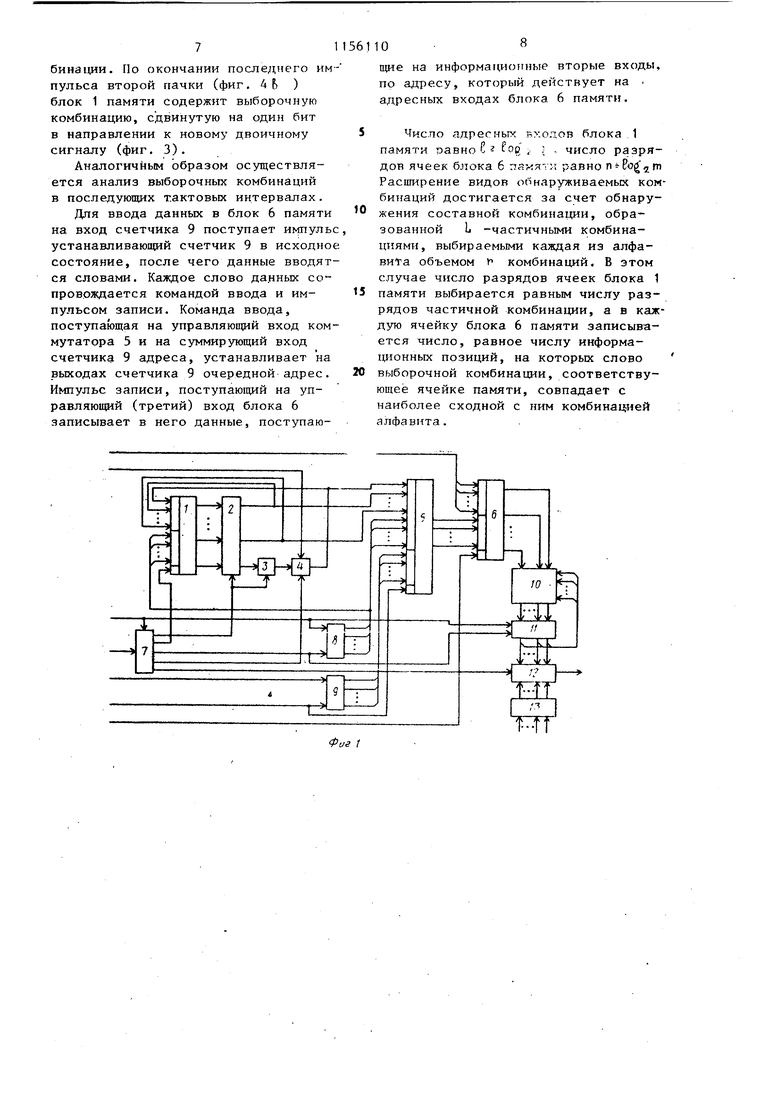

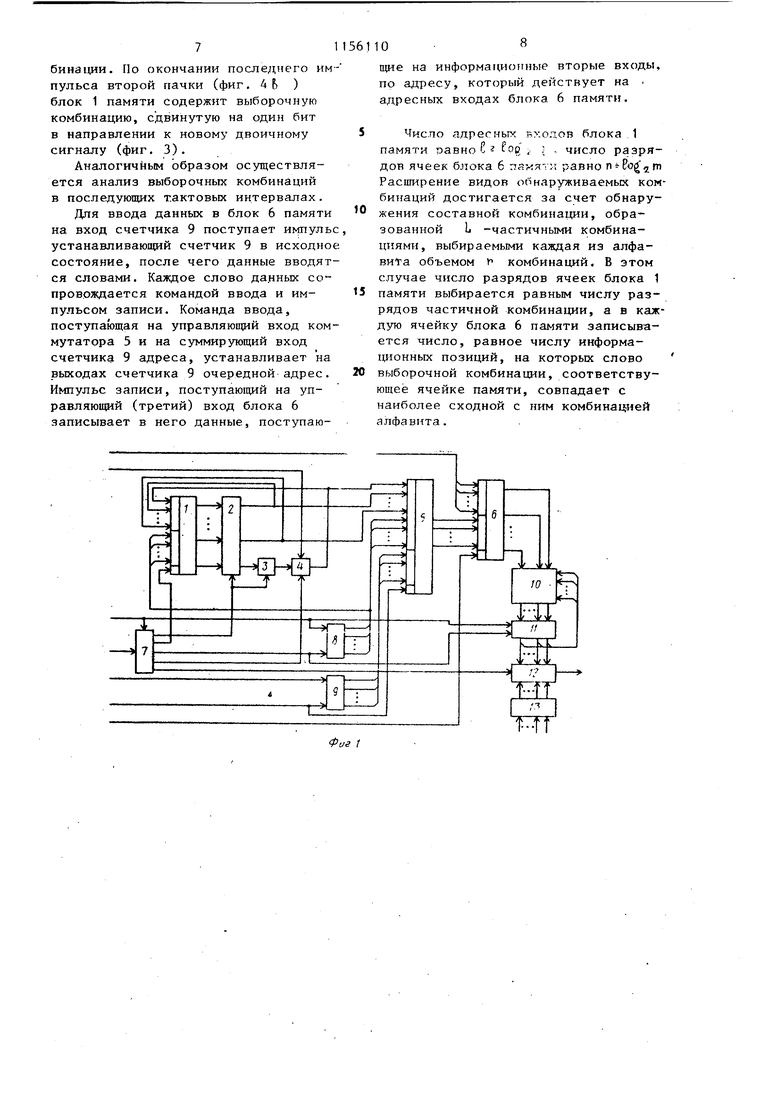

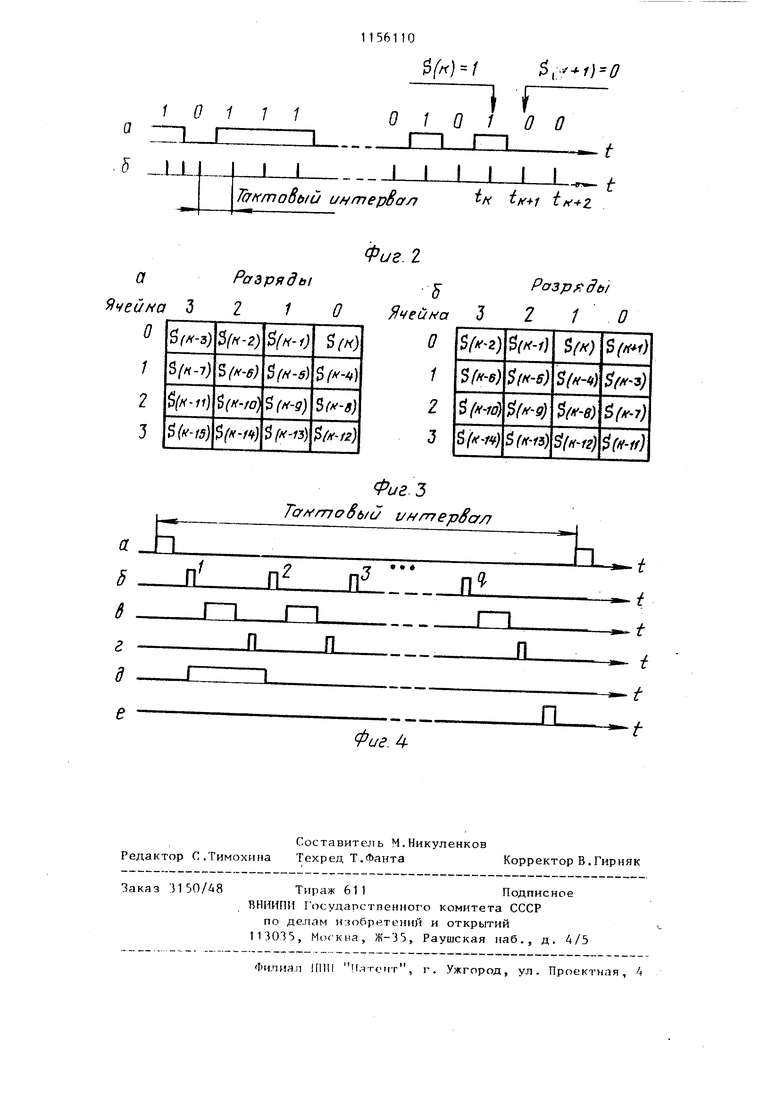

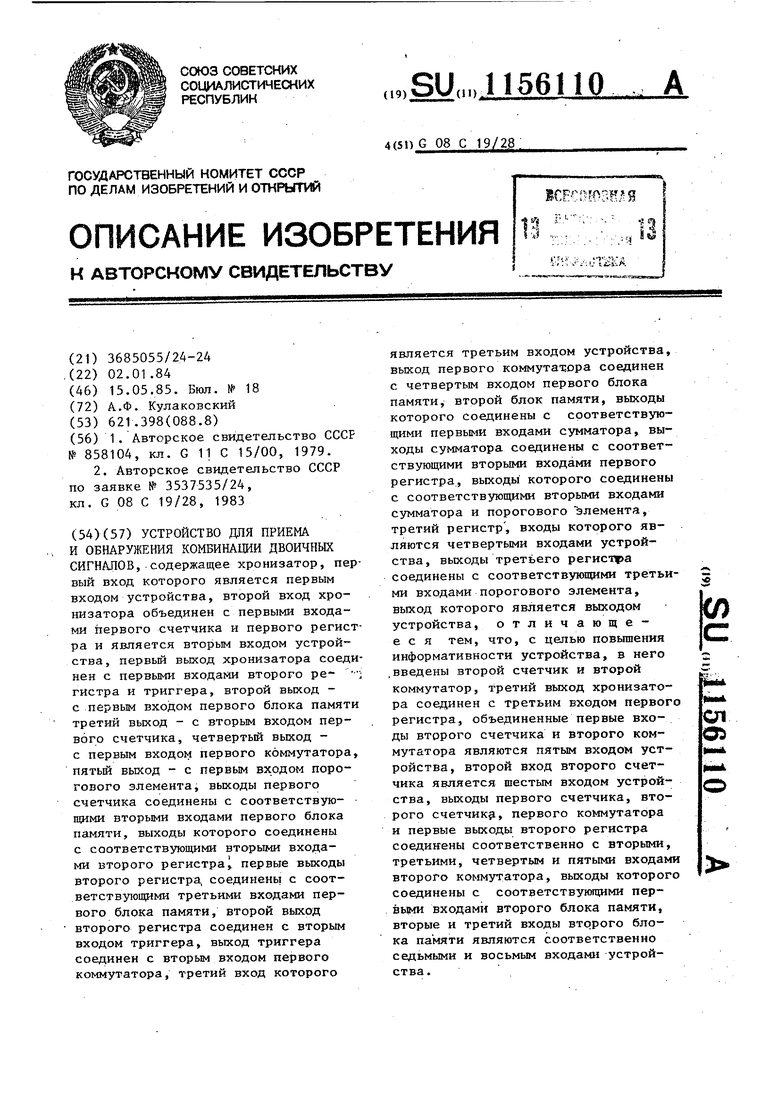

Изобретение относится к электрсг связи и может быть использовано в устройствах обработки дискретных сообш/.ний для обнаружения комбинани двоичных сигналов изиестного вида при неизвестном моменте ее приходя Известно устройство дня ириема и обнар,окония комбинации двоичных сигналов, содержащее г-енератор так товых имиульсов, формирователь импульсов, счетчики, )лементь И, эле менты ИЛИ, триггср, дешифраторы, элементы задержки, пороговый элемент, рег-истрь, хронизатор и блоки памяти lj , Недостатком изг естного уетроГтства яв,пяется низкое (1 1стродействие . Наиболее б;п1зким по ехническ.ой сущности к предлагаемому является устройство для приема н об {аружения комбинации двоичн,ых сигналов, содержащее хронизатор, первые вход которого являются первыми входа№1 устройства, второй вход хронизатора об1)е/и-1нен с первыми входами сче чика и первого регистра и является вторым ВХОДС5М устройства, первый вых(1д хронизатора есиллнен с вторы входом счетчика и первыми входами первого и второго элементов И, второй выход .хропизатора (соединен с первыми входами и второг-о регистра, трегиГ выхол. - с первьлм входом коммутатора, четвертый выход - с вторым входом первого регистра, пятый 11ыход - с первыми входами первого блока памяти, порогового элемента, третьего и четвертого элементов И, шестой выход, с вторыми входами nepiioro и третье го элементов И, седьмой выход с вторьми входами второго и четвер того элементов И, вьгходы счетП1ка соединены с соотт етствую11Ц1Ми первым входами первого, второго и третьего блоков памяти, вьгходы третьего и четвертого элементов И соединены G вторьпчи входами соответственно второго и третьего блоков памяти, в ходы первого блока памяти соединены с соответствующими вторыми входами Btoporo регистра, первьй выход кот рого соединен с вторым входом триг гера, выход триггера соединен с пер вым входом коммутатора, второй вход коммутатора является третьим входом устройства, вторые выходы регистра и В111ХОД коммутатора соединены соответственно с первыми входами блоков сра15нения и третьими входами иервого блока памяти, выходы второго блока памяти соединены с вторыми входами соответствую1гу1х блоков сравнения, вь;ходы которых соединены с первыми входами соответствующих пятых элементов И, выходы третьего блока памяти соединены с вторыми входами соответствующих пятьгх элементов И, вр,1ходы которых соединены через четвертый блок памяти с соответствующими первыми входами сумматора, выходы сумматора соединены с третьими входаьш первого регистра, вьгходы котоpoio соединены с соответству ощими вторыми входами сумматора и порогового элемента, выходы третьего регистра соединены с соответствующими третьими входами иорогового элемента, третьи входы второго, третьего блоков памяти и входы третьего регистра являются соответственно четвертыми, пятыми и шестыми входами устройства, выходы первого, второго элементов И.и порогового элемента являются соответственно первым, BTOpi.iM и третьим выходами устройства 2. Недостатком этого устройства является ограниченное число видов обнаруживаемых комбинаций. Обнаруживаемыми являются комбинации с детерминированной структурой. Но устройство не обнаруживает, например, составную комбинагщю, образованную L -частичными комбинациями, выбираемыми каждая из алфавита объемом f комбинахщй, так как данная составная кo бинaция имеет определенное количество реализаций, а устройство может быть настроено только на одну ее peaJПIзaцию, хранящуюся в блоках памяти эталона и маски, то остальные ее реализации процускаются. Ограниченное число видов обнаруживаемых комбинаций снижает информативность известного устройства. Целью изобретения является повы-. щение информативности устройства. Указанная цель достигается тем, что в устройство для приема и обнаруткения комбинации двоичных сигналов, содержащее хронизатор, первьй вход которого является первым входом устройства, второй вход хронизатора объединен с первыми входами первого счетчика и первого регистра и является вторым входом устройства, перв выход хронизатора соединен с первым входами второго регистра и триггера второй выход - с первым входом первого блока памяти, третий выход - с вторым входом первого счетчика, чет вертый выход - с первым входом первого коммутатора, пятый выход - с первым входом порогового элемента, выходы первого счетчика соединены с соответствующими вторыми входами первого блока памяти, выходы которо го соединены с соответствующими вто рыми входами второго регистра, первые выходы второго ретистра соединены с соответствующими третьими входами первого блока памяти, второ выход второго регистра соединен с вторым входом триггера, выход триггера соединен с вторым входом перво го-коммутатора, третий вход которог является третьим входом устройства, выход первого коммутатора соединен с четвертым входом первого блока памяти, второй блок памяти, выходы которого соединены с соответствующими первыми входами сумматора, вых ды сумматора соединены с соответствующими вторыми входами первого регистра, выходы которого соединены с соответствующими вторыми входами сумматора и порогового элемента, третий регистр, входы которого явля ются четвертыми входами устройства, выходы третьего регистра соединены с соответствующими третьими входами порогового элемента, выход которого является выходом устройства, введены второй счетчик и второй коммутатор, третий выход хронизатора соединен с третьим входом первого регистра, объединенные первые входы второго счетчика и второго коммутатора являются пятым входом устройства, второй вход второго счетчика является шестым входом устройства, выходы первого счетчика, второго счетчика, первого коммутатора и первые выходы второго регистра соединены соответственно с вторыми, третьими, четвер тым и пятыми входами второго коммутатора, выходы которого соединены с соответствующими пepвы ш входами вто рого блока памяти, вторые и третий входы второго блока памяти являются соответственно седьмыми и восьмым входами устройства. На фпг. 1 приведена структурнаи схема предла -аемого устройства; на фиг. 2 - временные диа1р чммы входных двоичных сигналов и тактовых импульсов, на фиг. 3 пример со1;ержимого ячеек блока 1 памяти; нп фиг. 4 временные диаграммы т1раш1яюпр х сигналов.. Устройство для приема и.оГжаружения комбинаций двоичных сиг.1алов содержит блок 1 памяти, регистр 2, триггер 3, коммутаторы 4 и 5, блок 6 памяти, хронизатор 7, счетчики 8 и 9 адреса, сумматор 10, регистр 11, пороговый элемент 12 и регистр 13. Устрюйство работает следующим образом. Принимаемые двоичные сигналы в виде последовательности элементарных посьшок О, 1 (фиг. 2а ) поступают на вход коммутатора 4. На входы хронизатора 7, счетчика 8 и регистра 11 поступают синхронизированные с двоичными сигналами тактовые импульсы (фиг. 2В ). Очередной тактовый импульс устанавливает в ноль счетчик 8 адреса., регистр 11 и запускает хронизатор 7, который в ответ на тактовый импульс вырабатывает в интервале между соседними тактовыми импульсами (фиг. 2 6 , 4а ) следующие управляющие сигналы: первую пачку из -- импульсов (фиг. 4 S ) где N - число двоичных сигналов комбинации; m - целое число, равное числу разрядов ячейки памяти в блоке 1 памяти; вторую пачку из л импульсов (фиг. 4Ь ), задержанную отнocитeJ ьнo первой пачки; третью пачку из Q импульсов (фиг. 4-2 ), задержанную относитепьно второй пачки, импульс ввода принимаемого двоичного сигнала (фиг. 4е ), импульс считывания (фиг. 4 е ) . Блок 1 памяти, регистр 2, триггер 3 и коммутатор 4 обеспечивают хранение и считывание N -разрядной выборочной комбинации, образованной двоичными сигналами, принятьп ш в ив N -1 предьщущих тактовых интервалах. Эта комбинация упакована в блоке 1 памяти От-разрядными словами, нумерация которых возрастает в направлении к прошлому времени, а в словах старшим разрядам соответствуют более старые двоичые сигналы. Для примера на фиг. 3 оказано содержимое блока 1 памяти п моменты времени t 11 , tj, в случае 16-разрядной выборочной комбинации, упакованной четырьмя четырехразрядными словами (на фиг. 3 через e(i) обозначен двоичньй сигнал в момент i). Слова размещаются в ячейках памяти с адресами 0,1.,., 0 -1. Чтение слов выборочной комбинации осуществляется кодами с выходов счет чика 8 адреса, поступающими на адоесные входы блока 1 памяти. Первым в тактовом интервале считывается нулевое слово после установки в нол счетчика 8 адреса, остальные слова считываются при последовательном, наращивании на единиду его содержимого импульсами третьей пачки (фиг. 4 2 ), поступающими на суммирующий вход счетчика 8 с выхода хронизатора 7. После того, как считываемое слово установится на выходах блока 1 памяти, импульс перво пачки (фиг ,48 ) с выхода хронизатора 7 поступает на тактовый вход регистра 2, триггера 3 и записывает в регистр 2 слово выборочной комбинации, в триггер 3 - содержимое старшего разряда с выхода регистра 2, записанное в него из старшего разряда предыдущей ячейки блока 1 памяти. Следуюш 1й импульс второй па ки (фиг. 4 Ь ) с выхода хронизатора 7 поступает на управляющий вход блока 1 памяти и записывает в него по тому же адресу слово выборочной комбинации со сдвинутыми по направлению к старшим разрядам двоичными сигналами, так как выход коммутатора 4 соединен с информационным входом младшего разряда блока 1 памяти остальные информационные входы блок 1 соединены с выходами регистра 2 с перекосом на один разряд в сторону его младших разрядов. В младший разряд нулевого слова записывается принимаемьй в данный тактовьй интер вал двоичный сигнал, проходящий со входа устройства на выход коммутатора 4 благодаря наличию на его у равляющем входе импульса ввода (фиг. 4 ) с выхода хронизатора 7, а в младший разряд остальных слов старший разряд предьщущего слова, постзгпающий с выхода триггера 3 на выход коммутатора 4. Этим обеспечив ется сдвиг выборочной комбинации на один бит в направлении к новому двоичному сигналу. Каждое слово выборочной комбинации поступает на четвертый и пятые входы коммутатора 5, на вторые входы которого поступают коды с выходов счетчика 8 адреса, В режиме выделения комбинаций двоичных сигналов команда ввода на первом входе коммутатора 5 отсутствует, вследствие чего с входов коммутатора 5 на его выходы соединенные с адресными входами блока 6 памяти, поступает код, младшими разрядами которого является код слова выборочный комбинации, старшими разрядами - код номера этого слова. Ячейка блока 6 памяти с этим адресом содержит двоичный код числа информационных позиций, на которых совпадает слово выборочной комбинации со словом эталона (словом вьщеляемой комбинации). Например, если в случае четырех четырехразрядных слов вторым словом эталона является слово 0011, в котором все позиции информаи;ионные, тс для второго слова 0000 выборочной комбинации ячейка с адресом 100000 содержит код 010 (код числа 2), для второго слова 0001 выборочной комбинации ячейка с адресом 100001 код 011 (код числа 3) и т.д. по всем вариантам второго слова выборочной комбинации. Если же в слове эталона 0011 старший разряд (крайняя слева позиция) является неинформационным, то в ячейках с адресами 100000 и 100001 будет содержаться код 001 и 010, как результат сравнения слов 011 и 000, 011 и 001. Сумматор 10 суммирует двоичные числа с выходов блока 6 постоянной памяти и регистра 11. По окончании суммирования импульс третьей пачки (фиг. 4 2 ) с выхода хронизатора 7 поступает на тактовый вход регистра 1 1 и записывает в него содержимое сумматора 10, После обработки Q слов выборочной комбинации регистр 11 содержит число, равное равное числу информационных позиций, на которых выборочная комбинация совпадает с эталоном. Если это число не меньше порогового числа записанного в регистре 13, то импульс считывания (фиг, 4 е ) с выхода хронизатора 7, поступающий на стробирующий вход порогового элемента 12, считьгоает на выход устоойства решение об обнаружении комбинации. По окончании последнего импульса второй пачки (фиг, А f ) блок 1 памяти содержит выборочную комбинацию, сдвинутую на один бит в направлении к новому двоичному сигналу (фиг. 3).

Аналогичным образом осуществляется анализ выборочных комбинаций в последующих тактовых интервалах.

Для ввода данных в блок 6 памяти на вход счетчика 9 поступает импульс устанавливающий счетчик 9 в исходное состояние, после чего данные вводятся словами. Каждое слово данных сопровождается командой ввода и импульсом записи. Команда ввода, поступающая на управляющий вход коммутатора 5 и на суммирующий вход счетчика 9 адреса, устанавливает на выходах счетчика 9 очередной адрес. Импульс записи, поступающий на управляющий (третий) вход блока 6 записывает в него данные, поступающие на информациортные вторые входы, по адресу, который действует на адресных входах блока 6 памяти.

Число адресных кходов блока 1 памяти равно С , I , число разрядов ячеек блока 6 равно Расширение видов обнаруживаемых комбинаций достигается за счет обнаружения составной комбинации, образованной L -частичными комбинациями, выбираемыми каждая из алфавита объемом t комбинаций, В этом случае число разрядов ячеек блока 1 памяти выбирается равным числу разрядов частичной комбинации, а в каждую ячейку блока 6 памяти записывается число, равное числу информащшнных позиций, на которых слово выборочной комбинации, соответствующее ячейке памяти, совпадает с наиболее сходной с ним комбинацией алфавита.

10111

a

,)ff

f) /

I r

0101 00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство приема двоичных сигналов | 1984 |

|

SU1197116A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Обнаружитель комбинации двоичных сигналов | 1985 |

|

SU1506463A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1140172A1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1078455A1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА И ОБНАРУЖЕНИЯ КОМБИНАЦИИ ДВОИЧНЫХ СИГНАЛОВ, содержащее хронизатор, первый вход которого является первым входом устройства, второй вход хронизатора объединен с первыми входами первого счетчика и первого регистра и является вторым входом устройства, первый выход хронизатора соединен с первыми входами второго ре- гистра и триггера, второй выход с первым входом первого блока памяти третий выход - с вторым входом первого счетчика, четвертый выход с первым входом первого коммутатора, пятьй выход - с первым входом порогового элемента, выходы первого счетчика соединены с соответствую- щими вторыми входами первого блока памяти, выходы которого соединены с соответствующими вторыми входами второго регистра первые выходы второго регистра, соединены с соответствующими третьими входами первого блока памяти, второй выход второго регистра соединен с вторым входом триггера, выход триггера соединен с вторым входом первого коммутатора, третий вход которого является третьим входом устройства, выход первого коммутатзора соединен с четвертым входом первого блока памяти, второй блок памяти, выходы которого соединены с соответствующими первыми входами сумматора выходы сумматора соединены с соответствующими вторыми входами первого регистра, выходы которого соединены с соответствующим вторыми входами сумматора и порогового элемента, третий регистр , входы которого являются четвертыми входами устройства, выходы третьего регистра соединены с соответствующими третьими входами порогового элемента, выход которого является выходом устройства, отличающееся тем, что, с целью повышения информативности устройства, в него .введены второй счетчик и второй коммутатор, третий выход хронизатора соединен с третьим входом первого ся регистра, объединенные первые вхоО5 ды второго счетчика и второго коммутатора являются пятым входом устройства, второй вход второго счетчика является шестым входом устройО ства, выходы первого счетчика, второго счетчикэ, первого коммутатора и первые выходы второго регистра соединены соответственно с вторыми, третьими, четвертым и пятыми входами второго коммутатора, выходы которого соединены с соответствующими первьвда входами второго блока памяти, вторые и третий входы второго блока памяти являются соответственно седьмыми и восьмым входаш устройства .

Разряды

о

г 1 TffffrrjoSb/c/ (УЛ

Фиг. 2

Разр/ ды

г 10

Фиг 5

Фиг. 4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3537535/24, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-05-15—Публикация

1984-01-02—Подача