ми соответственно первого и второго элементов равнозначности, вторые входы которых соединены с выходами -соответственно первого и третьего дополнительных элементов И, которые соединены с выходами соответственно шестого и седьмого дополнительных элементов И, первые входы которых соединены с выходом первого инвертора, который соединен с первыми входами второго и восьмого дополнительных элементов И, второй вход многофункционального логического элемента соединен с вторым входом третьего дополнительного элемента И и выходом восьмого дополнительного элемента И, второй вход которого соединен с первым-входом шестого дополнительнйго элемента И и выходом второго инвертора, вход которого соединен с выходом элемента И, первым входом пятого дополнительного элемента И и вторым входом второго дополнительного элемента И, третий вход многофункционального логического элемента соединен с выходом пятого и вторым входом шестого дополнительных элементов И, а четвертый вход многофункционального логического элемента соединен с выходом шестого и вторым входом седьмого дополнительных.элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Счетный триггер | 1983 |

|

SU1088103A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1274148A1 |

| Мультиплексор | 1990 |

|

SU1780185A1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| Кварцевый генератор | 1983 |

|

SU1109855A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1481742A1 |

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ на МОП-транзисторах, содержащий .два элемента равнозначности, элемент И, затвор первого МОП-транзистора каждого элемента равнозначности соединен с первым входом элемента равнозначности, истоком второго МОП-транзистора, а также затвором и стоком третьего МОПтранзистора, второй вход каждого элемента равнозначности соединен с затвором второго МОП-транзистора, истоком первого МОП-транзистора и затвором и стоком четвертого МОПтранзистора, стоки первого и второго МОП-транзисторов соединены с истоком пятого МОП-транзистора и выходом элемента равнозначности, затвор и сток пятого МОП-транзистора соединены с первой шиной питания, а истоки третьего и четвертого МОПтранзисторов соединены с второй шиной питания, выходы первого и второго элементов равнозначности соединены соответственно с первым и вторьм входами элемента И, которые соединены с затворами соответственно первого и второго вспомогательного МОП-транзистора этого элемента И, первая шина питания соединена со стоком первого вспсжогательного МОПтранзистора, исток которого соединен со стоком второго вспомогательного МОП-транзистора, исток которого соединен с выходом элемента И, а также стоком и затвором третьего вспомогательного МОП-транзистораi исток которого соединен с второй шиной питания, отличающий, ся тем, .что, с целью расширения функциональных возможностей путем реализации логических функций при передаче информации в прямом и обратном направлении, в него дополнительно ввеi дены восемь элементов И и два инвертора, каждый из которых содержит первый и второй дополнительные МОПтранзисторы, вход в каждом из инверторов соединен с затвором первого дЬполнительного МОП-транзистора, исток которого соединен с второй шииой питания, а сток соединен с выходом инвертора и истоком второго дополнительного МОП-транзистора, затвор и сток которого соединены с первой шию ной питания, первый вход многофунк ционального логического элемента соединен с вторыи входом первого дополнительного элемента И и выходом со второго дополнительного элемента И, первый вход первого дополнительного элемента И соединен с первым входом третьего дополнительного элемента И, вторыми входами четвертого и пятого дополнительных элементов И и входом первого инвертора, который соединен с первым управляющее входом многофункционального логического элемента, второй и третий управпякщ1 е входы которого соединены с первыми входа

Изобретение относится к микроэлектронике и вычислительной технике и предназначено для реализации всех логических функций двух переменных с получением результата посредством коммутации как на выходах, так и на входах элемента.

Известен многофункциональный логический элемент, содержащий логические элементы И, входы которых соединены с выходами элементов равнозначности LI 1.

Недостатком этого логического элемента является ограниченность его функциональных возможностей, посколь ку он не обеспечивает возможности двунаправленной обработки информации

Наиболее близким к предлагаемому является многофункциональный логический элемент на МОП-транзисторах, содержащий два элемента равнозначности элемент И, первый вход элемента равнозначности соединен с затвором первого МОП-транзистора, истоком второго МОП-транзистора, а также затвором и стоком третьего МОП-транзистора, второй вход каждого элемента равнозначности соединен с затвором второго МОП-транзистора, истоком первого МОП-транзистора и затвором и стоком четвертого МОП-транзистора, стоки первого и второго МОП-транзисторов соединены с истоком пятого МОПтранзистора и выходом элемента равнозначности, затвор и сток пятого

МОП-транзистора соединены с первой шиной питания, а истоки третьего и четвертого МОП-транзисторов соединены с- второй шиной питания, выходы первого и второго элементов равнозначности соединены соответственно с первым и вторым входами элемента И которые соединены с затворами соответственно первого и второго вспомогательного МОП-транзистора этого элемента И, первая шина питания соединена со стоком первого вспомогательного МОП-транзистора, исток которого соединен со стоком второго вспомогательного МОП-транзистора, исток которого соединен с выходом элемента И, а также стоком и затвором третьего вспомогательного МОПтранзистора, исток .которого соединен с второй шиной питания 2.

Недостатком известного многофункционального логического элемента является ограниченность функциональных возможностей, поскольку он не обеспечивает реализации логических функций при передаче информации в прямом и обратном направлении.

Цель изобретения - расширение функциональных возможностей путем реализации логических функций при передаче информации в прямом и обратном направлении.

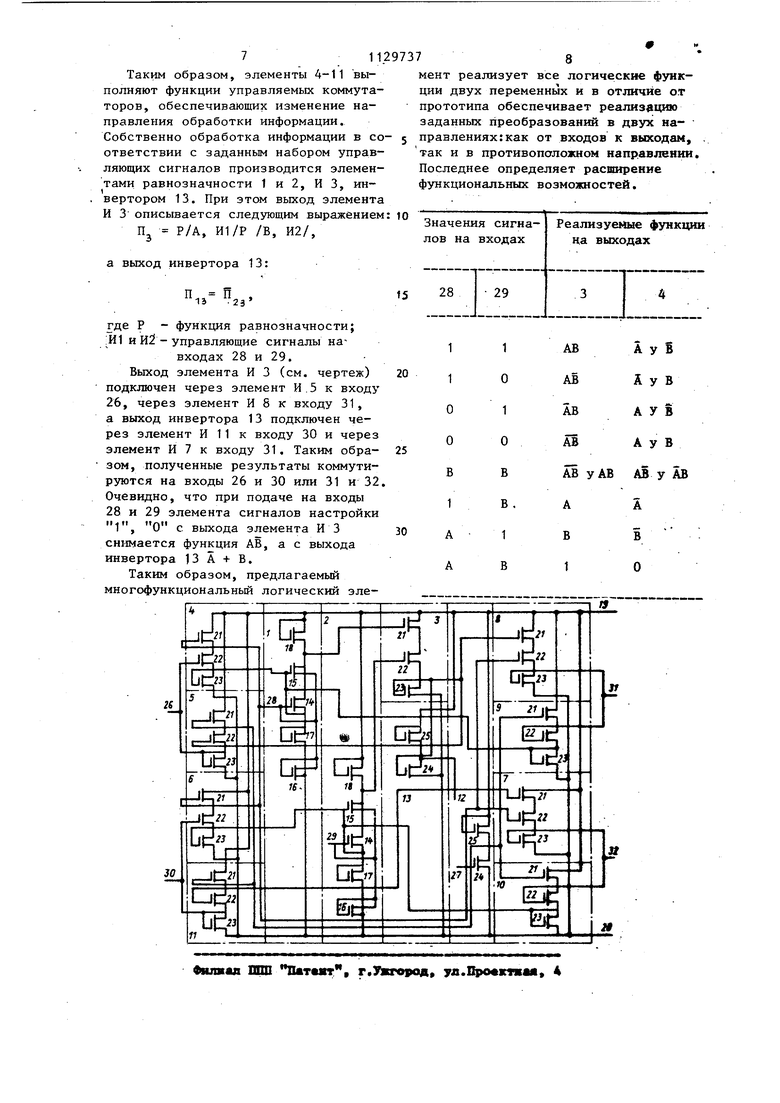

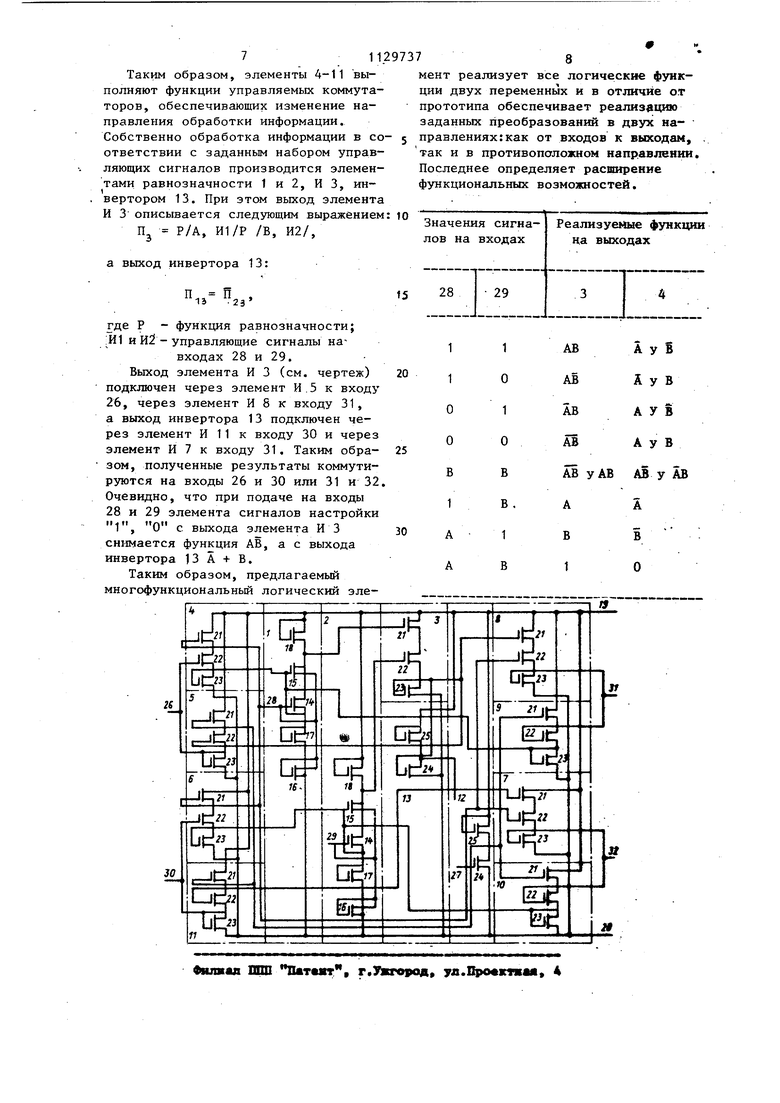

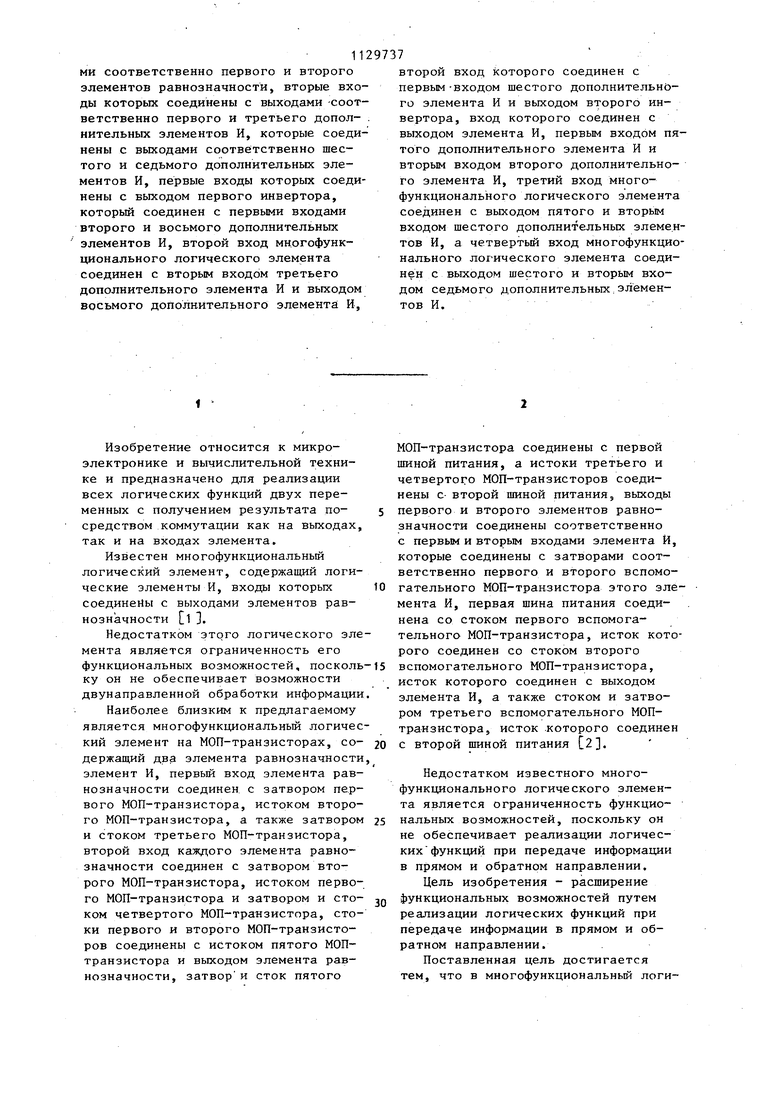

Поставленная цель достигается тем, что в многофункциональный логи3 112 ческий элемент на МОП-транзисторах, содержащий два элемента равнозначности, элемент И, затвор первого МОП-транзистора каждого элемента равнозначности соединен с первым «ходом элемента равнозначности, истоком второго МОП-транзистора, а также затвором и стоком третьего МОП-транзистора, второй вход каждого элемента равнозначности соединен с затвором второго МОП-транзистора, истоком первого МОП-транзистора и затвором и стоком четвертого .МОП-транзистора, стоки первого и вто рого МОП-транзисторов соединены с истоком пятого МОП-транзистора и выходом элемента равнозначности, затво и сток пятого МОП-транзистора соединены с первой шиной питания, а истоки третьего и четвертого МОП-транзис торов соединены с второй шиной питания, выходы первого и второго элементов равнозначности соединены соот ветственно с первым и вторым входами элемента И, которые соединены с затворами соответственно первого и второго вспомогательного МОП-транзистора этого элемента И, первая шина питания соединена со стоком перво го вспомогательного МОП-транзистора, исток которого соединен со сто- ком второго вспомогательного МОПтранзистора, исток которого соединен с выходом элемента И, а также стоком и.затвором третьего вспомогательного МОП-транзистора, исток которого соединен с второй шиной питания, дополнительно введены восемь элементов И и два инвертора, каждый из которых содержит первый и второй дополнительные МОП-транзисторы, вход в каждом из инверторов соединен с затвором первого дополнительного МОП-транзистора, исток которого соединен с второй шиной питания, а сток соединен с выходом инвертора и истоком второго дополнительного МОП-транзистора, затвор и сток которого соединены с первой шиной питания, первый вход многофункционально логического элемента соединен с вторым входом первого дополнительного элемента И и выходом второго дополни тельного элемента И, первый вход пе вого дополнительного элемента И соединен с первым входом третьего дополнительного элемента И, вторыми входами четвертого и пятого дополнительных элементов И и входом первого инвертора, который соединен с первым управляющим входом многофункционального логического элемента второй и третий управляющие входы которого соединены с первыми входами соответственно первого и второго элементов равнозначности, вторые входы которых соединены с выходами соответственно первого и третьего дополнительных элементов И, которые соединены с выходами соответственно шестого и седьмого дополнительных элементов И, первые входы которых соединены с выходом первого инвертора, который соединен с первыми входами второго и восьмого дополнительных элементов И, второй вход многофункционального логического элемента соединен с вторым входом третьего дополнительного элемента И и выходом восьмого дополнительного элемента И, второй вход которого соединен с первым входом шестого дополнительного элемента И и выходом второго инвертора, вход которого соединен с выходом элемента И, первым входом пятого дополнительного элемента И и вторым входом второго дополнительного элемента И, третий |вход многофункционального логического элемента соединен с выходом пятого и вторым входом шестого дополнительных элементов И, а четвертьй вход многофункционального логического элемента соединен с выходом шестого и BTopbiNf входом седьмого дополнительных элементов И. На чертеже показана структурная схема многофункционального логического элемента. Многофункциональный логический элемент на МОП-транзисторах содержит два элемента равнозначности 1 и 2, элемент И 3, восемь дополнительных элементов И 4-11 и два инвертора 12 и 13, первый вход каждого- элемента равнозначности соединен с затвором первого МОП-транзистора 14, истоком второго МОП-транзистора 15, а также затвором и стоком третьего МОП-транзистора 16, второй вход каждого элемента равнозначности соединен с затвором второго МОП-транзистора 15, истоком первого МОП-транзистора 14 и затвором и стоком четвертого МОПтранзистора 17, стоки первого 14 и второго 15 МОП-транзисторов соединены с истоком пятого МОП-транзистора 1 8 и выходом элемента равнознач11ности, затвор и сток пятого МОП- транзистора 18 соединены с первой шиной питания 19, а истоки третьего 16 и четвертого 17 МОП-транзисторов соединены с второй шиной питания 20 выходы первого 1 и второго 2 элементов равнозначности соединены соответ ств.енно с первым и вторым входами элемента ИЗ, которые соединены в элемента И и каждом дополнительном элементе И с затворами соответственно первого 21 и второго 22 вспомо гательного МОП-транзистора этого эле мента И, первая шина питания 19 соединена со стоком первого вспомогательного МОП-транзистора 215 исток которого соединен со стоком второго вспомогательного МОП-транзистора 22 исток которого соединен с выходом элемента И а также стоком и затвором третьего вспомогательного МОПтранзистора 23, исток которого соеди нен с второй шиной питания 20. Каждый инвертор содержит первый 24 и второй 25 дополнительные МОП-транзисторы, вход в каждом из инверторов соединен с затвором первого дополнительного МОП-транзистора 24, и ток которого соединен с второй шиной питания 20, а сток соединен с выходом инвертора и истоком второго дополнительного МОП-транзистора 25, затвор и сток которого соединены с первой шиной питания 19. Первый вход 26 многофункционального логического элемента соединен с вторым входом первого дополнительного элемента И 14 и выходом второго дополнительного элемента И 5, первый вход перво го дополнительного элемента И 4 соединен с лервым входом третьего допол нительного элемента И 6, вторьгми входами четвертого 7 и пятого 8 дополнительных элементов И и входом первого инвертора 12, который соединен с первым управляющим входом 27 многофункционального логического элемента, второй 28 и третий 29 управляющие входы которого соединены с первыми входами соответственно первого 1 и второго 2 элементов равнозначности, вторые входы которых соединены с выходами соответственно первого 4 и третьего 6.дополнительных элементов И, которые соединены с выходами соответственно шестого 9 и седьмого 10 дополнительных элементов И, первые входы которых соеди нены с выходом первого инвертора 12 6 который соединен с первыми входами второго. 5 и восьмого 11 дополнительных элементов И. Второй вход 30 многофункционального логического элемента соединен с вторым входом третьего 6 дополнительного элемента И и выходом восьмого 11 дополнительного элемента И, второй вход которого соединен с первым входом шестого 9 дополнительного элемента И и выходом второго инвертора 13, вход которого соединен с выходом элемента ИЗ, первым входом пятого дополнительного элемента И 8 и вторым входом второго дополнительного элемента И 5. Третий вход 31 многофункционального логического элемента соединен с выходом пятого 8 и вторым входом DiecToro 9 дополнительных элементов И, а четвертый вход 32 многофункционального логического элемента соединен с выходом шестого 9 и вторым входом седьмого 10 дополнительных элементов И. , Устройство функционирует следующим образом. На управляющий вход 27 подается сигнал, определяющий направление обработки информации. Если этот сигнал соответствует логической единице, элементы 4, 6, 8и7И открыты. Одно временно этот сигнал, инвертируясь, подается на элементы 5, 11, 9 и 10-И, которые при этом закрыты. В противном случае (на вход 27 подается сигнал, соответствующий логическому нулю) открыты элементы 9 и 10 И и закрыты 4. и 6. Если на вход 27 подается сигнал логической единицы, обработка информации осуществляется от входов 26 и 30 к входам 31 и 32. При этом на входы 26 и 30 элемента подаются входные переменные А и В, а на входы управления 28 и.29 настроечные сигналы, которые принимают значения констант О и 1 и входных переменных А и В. При этом с входов 31 и 32 снимаются значения прямой и. инверсной логических функций соответственно. Виды реализуемых функций для определенных значений управляющих сигналов представлены в таблице. При подаче на вход 27 логического нуля переменные А и В подаются на входы 31 и 32, а реализуемые функции снимаются с входов 26 и 30, так как в этом случае закрыты элементы И 4, 6, 8 и 7.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-12-15—Публикация

1983-01-28—Подача