Ј

оо 1

4

to

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1986 |

|

SU1405109A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

| Схема сквозного переноса на КМОП-транзисторах | 1988 |

|

SU1529440A1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Мультиплексор | 1990 |

|

SU1780185A1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 1996 |

|

RU2164036C2 |

| СХЕМА ФОРМИРОВАТЕЛЯ УПРАВЛЯЮЩИХ СИГНАЛОВ | 2017 |

|

RU2664014C1 |

| Блок формирования переноса сумматора | 1989 |

|

SU1718214A1 |

| СХЕМА ФОРМИРОВАТЕЛЯ УПРАВЛЯЮЩИХ СИГНАЛОВ | 2020 |

|

RU2749178C1 |

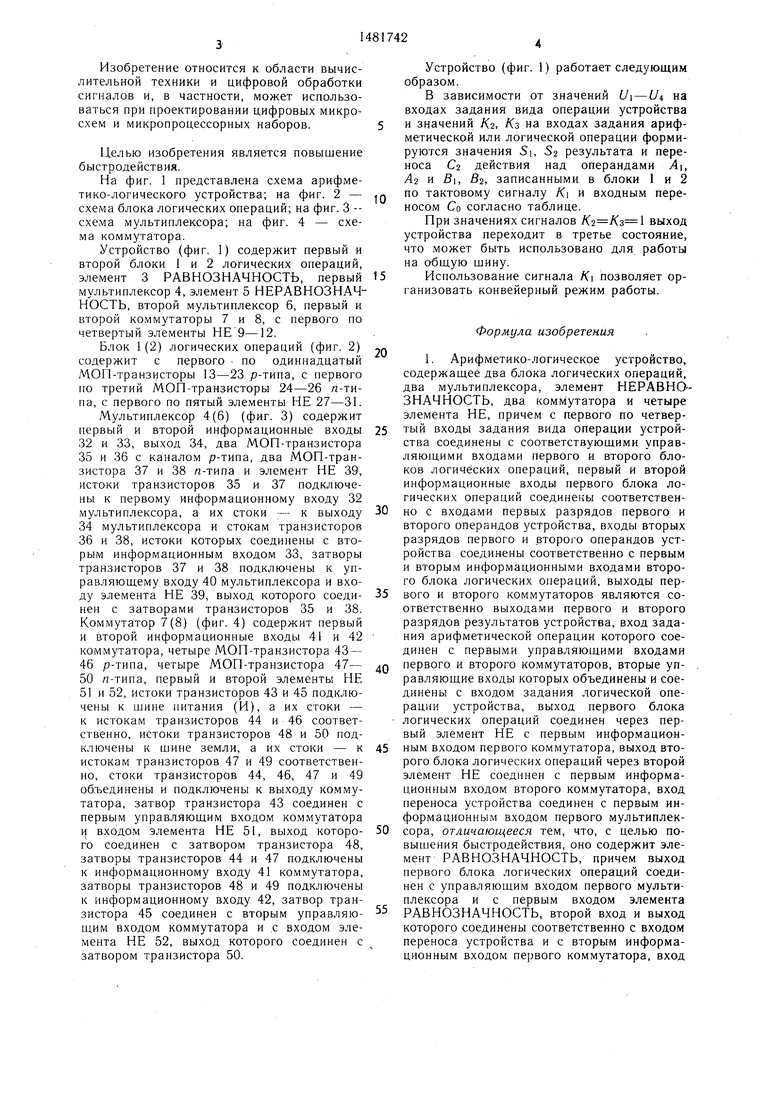

Изобретение относится к цифровой обработке сигналов и позволяет повысить быстродействие арифметико-логического устройства. Устройство содержит блок 1,2 логических операций, элемент 3 РАЗНОЗНАЧНОСТЬ, мультиплексоры 4,6, элемент 5 НЕРАВНОЗНАЧНОСТЬ, коммутаторы 7,8 и элементы НЕ 9-12 с соответствующими связями. Межразрядный перенос формируется мультиплексорами, результаты операций - коммутаторами с тремя устойчивыми состояниями. Использование тактирующих сигналов позволяет организовать режим обработки данных, что повышает быстродействие устройства. 1 з.п. ф-лы, 4 ил., 1 табл.

Фие.1

з

Изобретение относится к области вычислительной техники и цифровой обработки сигналов и, в частности, может использоваться при проектировании цифровых микросхем и микропроцессорных наборов.

Целью изобретения является повышение быстродействия.

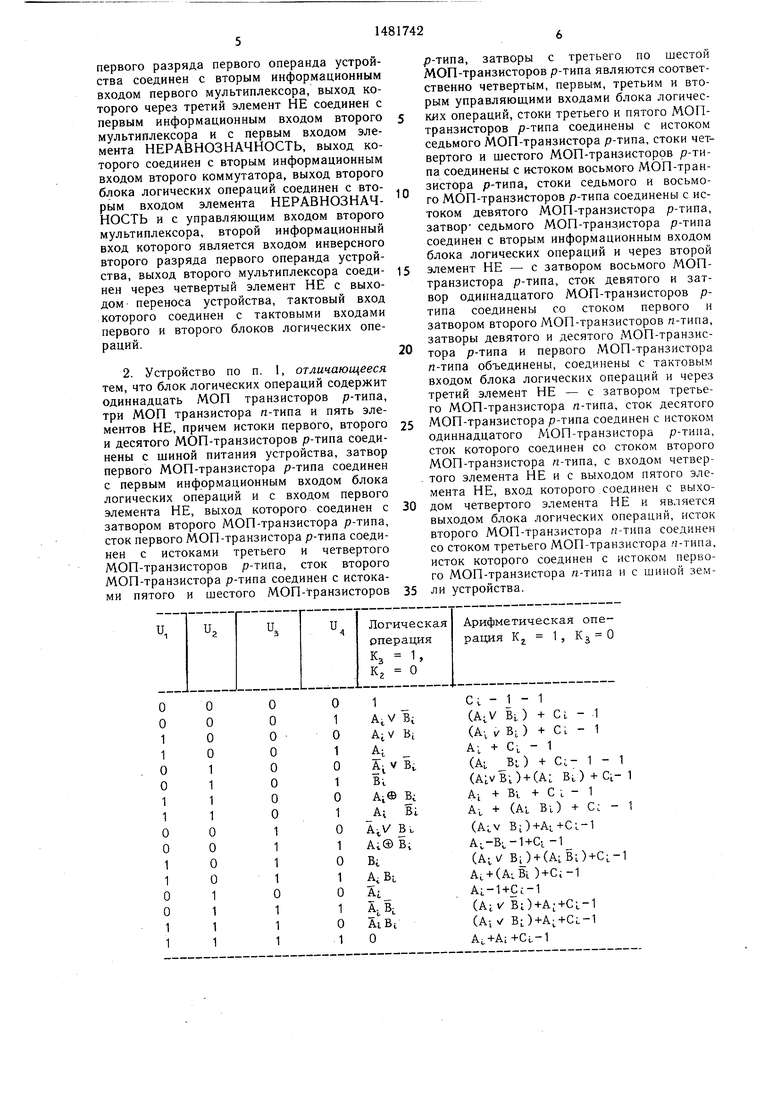

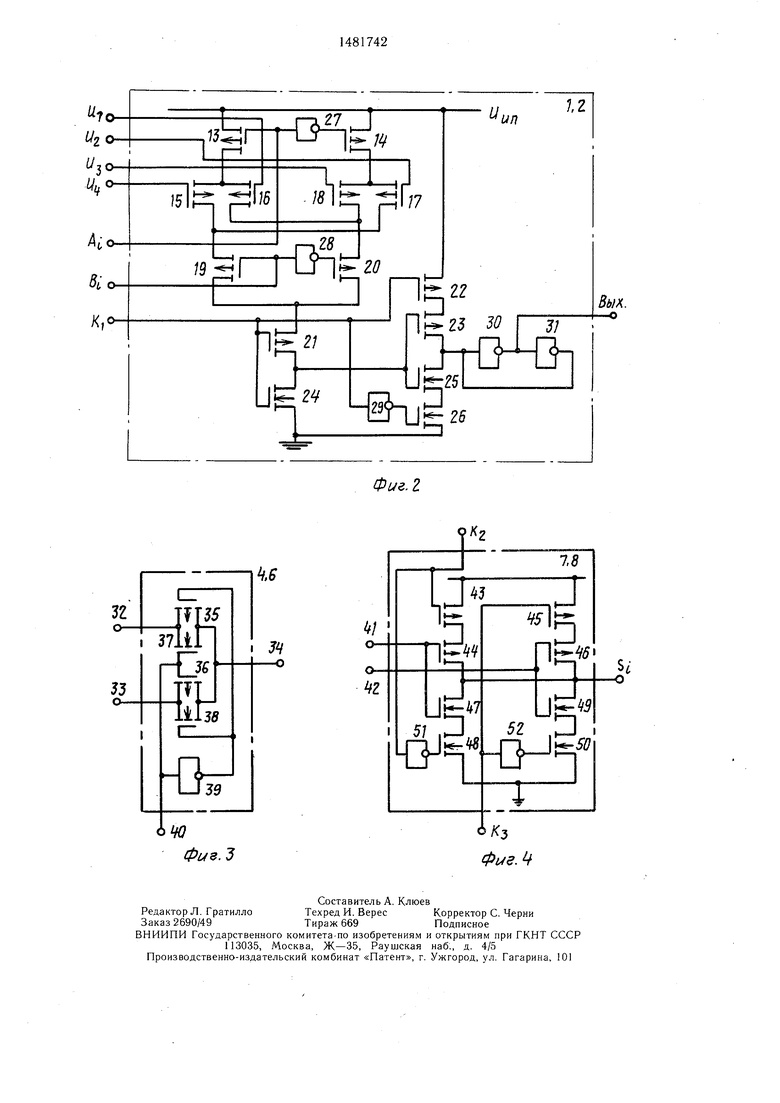

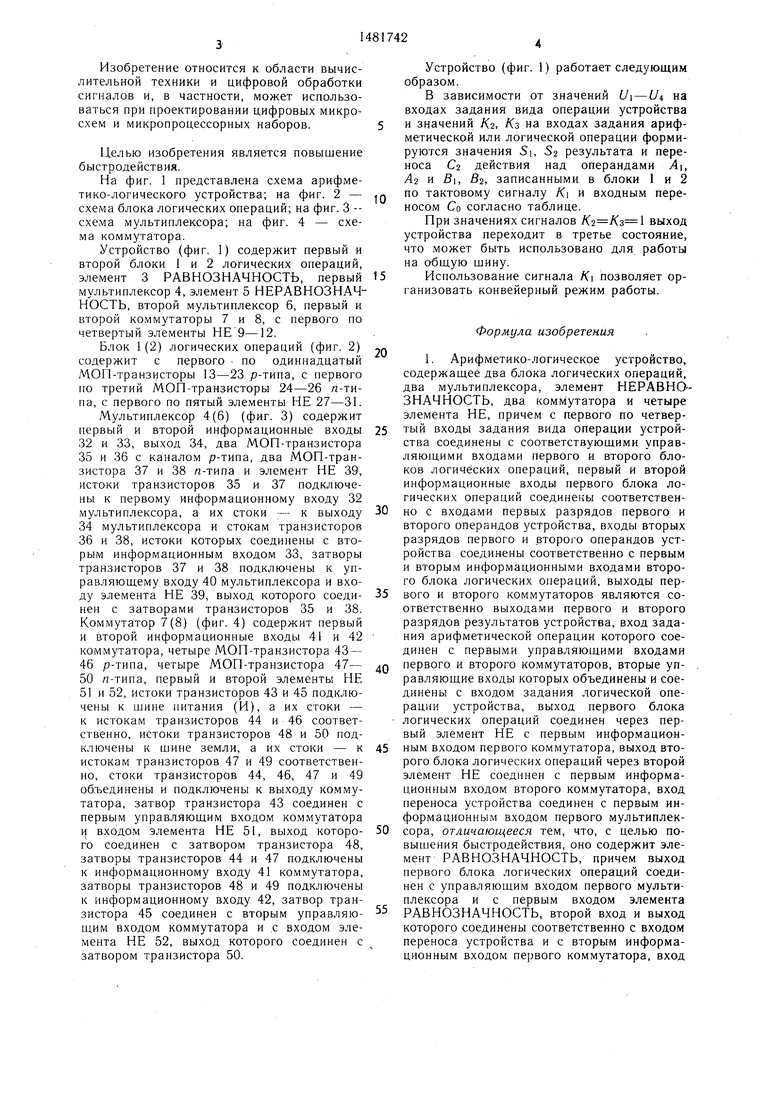

На фиг. 1 представлена схема арифметико-логического устройства; на фиг. 2 - схема блока логических операций; на фиг. 3 -- схема мультиплексора; на фиг. 4 - схема коммутатора.

Устройство (фиг. 1) содержит первый и второй блоки 1 и 2 логических операций, элемент 3 РАВНОЗНАЧНОСТЬ, первый мультиплексор 4, элемент 5 НЕРАВНОЗНАЧНОСТЬ, второй мультиплексор 6, первый и второй коммутаторы 7 и 8, с первого по четвертый элементы НЕ 9-12.

Блок 1 (2) логических операций (фиг. 2) содержит с первого по одиннадцатый МОП-транзисторы 13-23 р-типа, с первого по третий МОП-транзисторы 24-26 л-ти- па, с первого по пятый элементы НЕ 27-31.

Мультиплексор 4(6) (фиг. 3) содержит первый и второй информационные входы 32 и 33, выход 34, два МОП-транзистора

35и 36 с каналом /о-типа, два МОП-транзистора 37 и 38 n-типа и элемент НЕ 39, истоки транзисторов 35 и 37 подключены к первому информационному входу 32 мультиплексора, а их стоки - к выходу 34 мультиплексора и стокам транзисторов

36и 38, истоки которых соединены с вторым информационным входом 33, затворы транзисторов 37 и 38 подключены к управляющему входу 40 мультиплексора и входу элемента НЕ 39, выход которого соеди- нен с затворами транзисторов 35 и 38. Коммутатор 7(8) (фиг. 4) содержит первый

и второй информационные входы 41 и 42 коммутатора, четыре МОП-транзистора 43- 46 р-типа, четыре МОП-транзистора 47-

50п-типа, первый и второй элементы НЕ

51и 52, истоки транзисторов 43 и 45 подключены к шине питания (И), а их стоки - к истокам транзисторов 44 и 46 соответственно, истоки транзисторов 48 и 50 подключены к шине земли, а их стоки - к истокам транзисторов 47 и 49 соответственно, стоки транзисторов 44, 46, 47 и 49 объединены и подключены к выходу коммутатора, затвор транзистора 43 соединен с первым управляющим входом коммутатора

и входом элемента НЕ 51, выход которо- го соединен с затвором транзистора 48, затворы транзисторов 44 и 47 подключены к информационному входу 41 коммутатора, затворы транзисторов 48 и 49 подключены к информационному входу 42, затвор транзистора 45 соединен с вторым управляю- щим входом коммутатора и с входом элемента НЕ 52, выход которого соединен с затвором транзистора 50.

Устройство (фиг. 1) работает следующим образом.

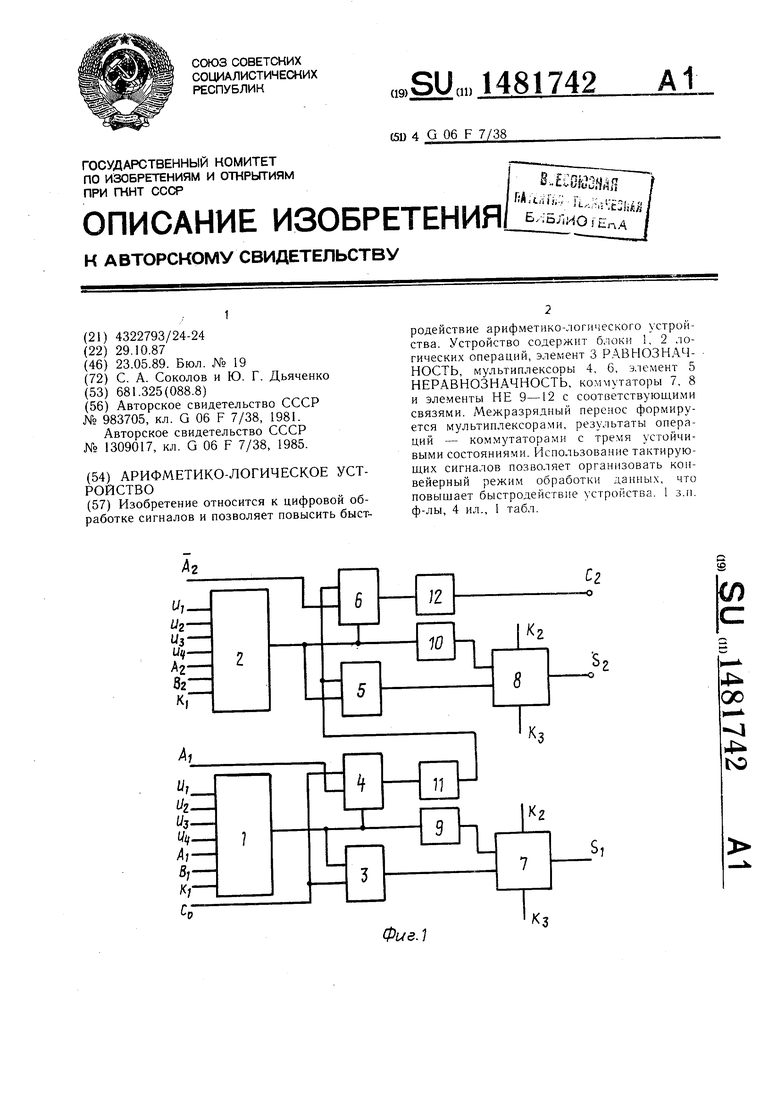

В зависимости от значений U - U на входах задания вида операции устройства и значений К.2, /Сз на входах задания арифметической или логической операции формируются значения Si, 82 результата и переноса Cz действия над операндами А, Ач и В, В, записанными в блоки 1 и 2 по тактовому сигналу К. и входным переносом Со согласно таблице.

При значениях сигналов ( выход устройства переходит в третье состояние, что может быть использовано для работы на общую шину.

Использование сигнала К. позволяет организовать конвейерный режим работы.

Формула изобретения

первого разряда первого операнда устройства соединен с вторым информационным входом первого мультиплексора, выход которого через третий элемент НЕ соединен с первым информационным входом второго мультиплексора и с первым входом элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с вторым информационным входом второго коммутатора, выход второго блока логических операций соединен с вто- рым входом элемента НЕРАВНОЗНАЧНОСТЬ и с управляющим входом второго мультиплексора, второй информационный вход которого является входом инверсного второго разряда первого операнда устройства, выход второго мультиплексора соеди- нен через четвертый элемент НЕ с выходом переноса устройства, тактовый вход которого соединен с тактовыми входами первого и второго блоков логических операций.

О О О О О О О О 1 1 1 1 О 1 1 1

р-типа, затворы с третьего по шестой МОП-транзисторов р-типа являются соответственно четвертым, первым, третьим и вторым управляющими входами блока логических операций, стоки третьего и пятого МОП- транзисторов р-типа соединены с истоком седьмого МОП-транзистора р-типа, стоки четвертого и шестого МОП-транзисторов р-типа соединены с истоком восьмого МОП-транзистора р-типа, стоки седьмого и восьмого МОП-транзисторов р-типа соединены с истоком девятого МОП-транзистора р-типа, затвор- седьмого МОП-транзистора р-типа соединен с вторым информационным входом блока логических операций и через второй элемент НЕ - с затвором восьмого МОП- транзистора р-типа, сток девятого и затвор одиннадцатого МОП-транзисторов р- типа соединены со стоком первого и затвором второго МОП-транзисторов п-типа, затворы девятого и десятого МОП-транзистора р-типа и первого МОП-транзистора n-типа объединены, соединены с тактовым входом блока логических операций и через третий элемент НЕ - с затвором третьего МОП-транзистора n-типа, сток десятого МОП-транзистора р-типа соединен с истоком одиннадцатого МОП-транзистора р-тииа, сток которого соединен со стоком второго МОП-транзистора n-типа, с входом четвертого элемента НЕ и с выходом пятого элемента НЕ, вход которого соединен с выходом четвертого элемента НЕ и является выходом блока логических операций, исток второго МОП-транзистора «-типа соединен со стоком третьего МОП-транзистора i-типа, исток которого соединен с истоком первого МОП-транзистора n-типа и с шиной земли устройства.

Ci - 1 - 1

(AtV BL) + Сi - 1

(Av v BL) + СI - 1

AL + C-t - 1

(At BL) + Ci- 1 -

(ALVB;) + (AL в,) + c-t-

A-t + Bi + С i - 1 A-t + (At Bi) + C; - (AiV BL)+A.,+C ,-1 A.-B. -1+d-1 (Atv/ Bj) + (A;.Bi)+C A, + ( )+C;-1 Ai-1+Ct-1 (AiV Bi)+A-+CL-1 (A v Bi)+Ai+Cb-1 AL+A;+Cj,-1

Ш 111

X

Я -о

53 оJTTJ

lil

-В

Фие.2

| Устройство для арифметической и логической обработки двоичных чисел | 1981 |

|

SU983705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Управляемый арифметический модуль | 1985 |

|

SU1309017A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-29—Подача