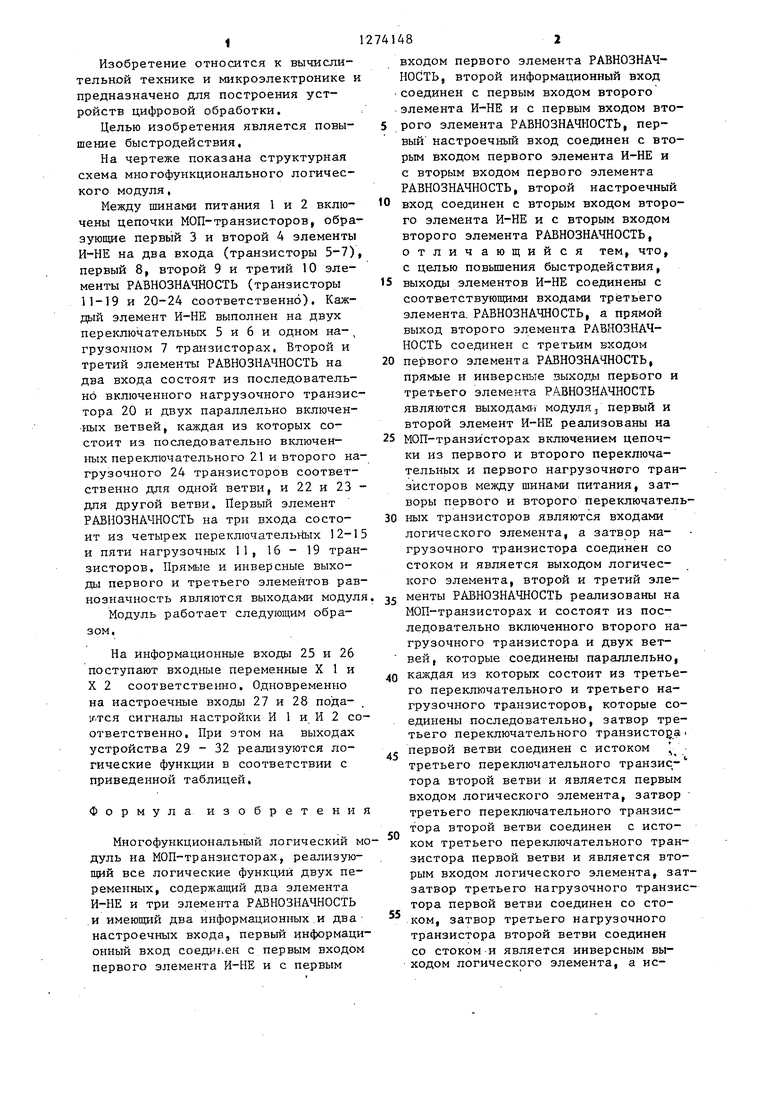

Изобретение относится к вычислительной технике и микроэлектронике предназначено для построения устройств цифровой обработки. Целью изобретения является повышение быстродействия, На чертеже показана структурная схема многофункционального логического модуля, Между шинами питания 1 и 2 включены цепочки МОП-транзисторов, обра зующие первый 3 и второй 4 элементы И-НЕ на два входа (транзисторы 5-7) первый 8, второй 9 и третий 10 элементы РАВНОЗНАЧНОСТЬ (транзисторы 11-19 и 20-24 соответственно). Каждый элемент И-НЕ выполнен на двух переключательных 5 и 6 и одном на-, грузоином 7 трш-1зисторах. Второй и третий элементы РАВНОЗНАЧНОСТЬ на два входа состоят из последовательно включенного нагрузочного транзис тора 20 и двух параллельно включенных ветвей, каждая из которых состоит из последовательно включенных переключательного 21 и второго на грузочного 24 транзисторов соответственно для одной ветви, и 22 и 23 дпя другой ветви. Первый элемент РАВНОЗНАЧНОСТЬ на три входа состоит из четырех переключательных 12-1 и пяти нагрузочных 11, 16 - 19 тран зисторов. Прямые и инверсные выходы первого и третьего элементов рав нозначность являются выходами модул Модуль работает следующим образом. На информационные входы 25 и 26 поступают входные переменные X 1 и X 2 соответственно. Одновременно на настроечные входы 27 и 28 подается сигналы настройки И 1 и И 2 со ответственно. При этом на выходах устройства 29 - 32 реализуются логические функции в соответствии с приведенной таблицей. Формула изобретени Многофункциональный логический м дуль на МОП-транзисторах, реализующий все логические функций двух переменных, содержшдий два элемента И-НЕ и три элемента РАВНОЗНАЧНОСТЬ ,и имеющий два информационных.и два настроечных входа, первый информаци онный вход .ен с первым входом первого элемента И-НЕ и с первым входом первого элемента РАВНОЗНАЧНОСТЬ, второй информационный вход соединен с первым входом второго элемента И-НЕ и с первым входом второго элемента РАВНОЗНАЧНОСТЬ, первый настроечный вход соединен с вторым входом первого элемента И-НЕ и с вторым входом первого элемента РАВНОЗНАЧНОСТЬ, второй настроечный вход соединен с вторым входом второго элемента И-НЕ и с вторым входом второго элемента РАВНОЗНАЧНОСТЬ, отличающийся тем, что, с целью повышения быстродействия, выходы элементов И-НЕ соединены с соответствующими входами третьего элемента. РАВНОЗНАЧНОСТЬ, а прямой выход второго элемента РАВНОЗНАЧНОСТЬ соединен с третьим входом первого элемента РАВНОЗНАЧНОСТЬ, прямые и инверсные зыходд первого и третьего элемента РАВНОЗНАЧНОСТЬ являются выходами модуля, первый и второй элемент И-НЕ реализованы на МОП-транзисторах включением цепочки из первого и второго переключательных и первого нагрузочного транзисторов между шинами питания, затворы первого и второго переключательных транзисторов являются входами логического элемента, а затвор нагрузочного транзистора соединен со стоком и является выходом логического элемента, второй и третий элементы РАВНОЗНАЧНОСТЬ реализованы на МОП-транзисторах и состоят из последовательно включенного второго нагрузочного транзистора и двух ветвей, которые соединены параллельно, каждая из которых состоит из третьего переключательного и третьего нагрузочного транзисторов, которые соединены последовательно, затвор третьего переключательного транзистора первой ветви соединен с истоком третьего переключательного транзис,тора второй ветви и является первым входом логического элемента, затвор третьего переключательного транзистора второй ветви соединен с истоком третьего переключательного транзистора первой ветви и является вторым входом логического элемента, затзатвор третьего нагрузочного транзистора первой ветви соединен со стоком, затвор третьего нагрузочного транзистора второй ветви соединен со стоком и является инверсным выходом логического элемента, а исток второго нагрузочного транзистора является прямым выходом логического элемента, а первый элемент РАВНОЗНАЧНОСТЬ на три входа реализован на МОП-транзисторах, образован путем последовательного включения между шинами питания четвертого нагрузочного транзистора и четырех ветвей, которые включены параллельно, каждая состоит из четвертого переключательного и пятого нагрузочного транзисторов, которые соединены последовательно, затвор четвертого переключательного транзистора первой ветви соединен с истоком четвертого переключательного транзистора второй ветви и является первым входом логи-ческого элемента, затвор переключательного

741484

транзистора второй ветви соединен с затвором четвертого переключательного транзистора четвертой ветви и с истоками четвертых переключа5 тельных транзисторов первой и третьей ветви и является вторым входом логического элемента, затвор четвертого переключательного транзистора третьей ветви соединен с ис10 током четвертого переключательного транзистора четвертой ветви и является третьим входом логического элемента, затворы четвертого и пятых нагрузочных транзисторов сое15 динены с их стоками, исток четвертого нагрузочного транзистора является прямым, а сток пятого нагрузочного транзистора первой ветви инверсным выходами логическогоэлемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный модуль | 1980 |

|

SU890557A1 |

| Многофункциональный логический элемент | 1980 |

|

SU898618A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

| Многофункциональный логический элемент | 1983 |

|

SU1129737A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064470A1 |

| Универсальный логический модуль | 1984 |

|

SU1213537A1 |

Изобретение относится к вычислительной, технике и микроэлектронике и предназначено для построения устройств цифровой обработки. Цель изобретения - повышение быстродействия. Устройство содержит элементы И-НЕ 3 и 4, транзисторы 5-7, элементы 8-10 РАВНОЗНАЧНОСТЬ. Реализация элементов И-НЕ 3 и 4 и элементов 8-10 РАВНОЗНАЧНОСТЬ на МОП-транзисторах позволяет увеличить быстродействие модуля в 1,5 раза. I табл., 1 ил.

О 1

О О 1 1

О 1

ОХ1Х2X1VX2

Х2J X1VX2

XIХ1Х2X1VX2

Х1-ОХ2Х1Х25Г1УХ2

Х20Х2

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Универсальный логический модуль | 1984 |

|

SU1213537A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-11-30—Публикация

1985-03-12—Подача