(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения закона распределения | 1987 |

|

SU1520545A1 |

| Устройство для определения закона распределения случайной величины | 1987 |

|

SU1425715A1 |

| Статистический анализатор | 1986 |

|

SU1401482A1 |

| Статистический анализатор | 1986 |

|

SU1354211A1 |

| Статистический анализатор | 1987 |

|

SU1425716A1 |

| Статистический анализатор | 1989 |

|

SU1695328A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство генерации равномерно распределенных псевдослучайных чисел | 2024 |

|

RU2840424C1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1387173A1 |

Изобретение относится к области статистической обработки случайных величин и может ислользоваться для олределения закона распределения при малом числе наблюдений. Целью изобретения является повышение точности определения закона распределения. Работа устройства включает три этапа. На первом этапе определяются два параметра распределения. Для этого

оо ас

00

со

в блоке определения 11ар 1метров распределения 24 организуется процесс решения системы уравнений с двумя неизвестными методом двумерной дихотомии, основанным на известной процедуре уточнения корней методом деления отрезка пополам. Метод деления отрезка пополам, реатшзуемый блоком определения параметров распределения, представляет собой итеративную процедуру вычисления значений уравнений при целенаправленном изменении параметра, причем на каждом шаге об

1

Изобретение относится к технике статистической обработки случайных величин и может быть использовано для определения закона распределения случайной вeличин l при малом числе измерений.

Цель изобретения - повьшение точности определения закона распределения при малом-числе наблюдений.

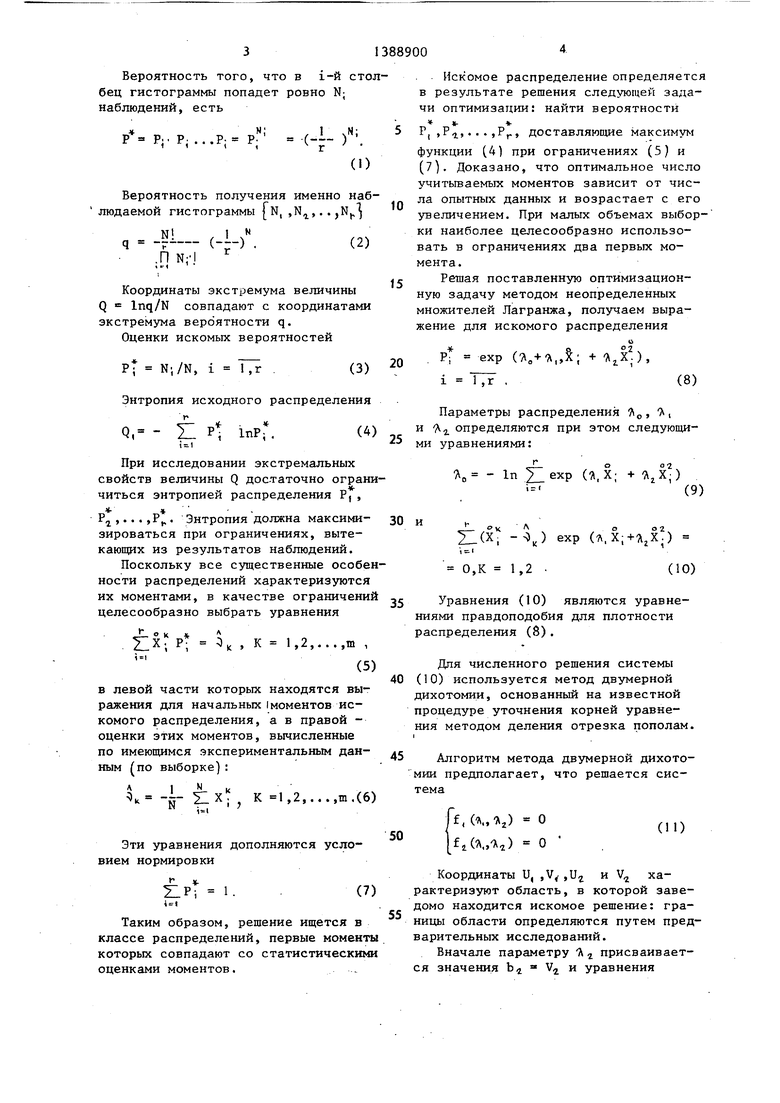

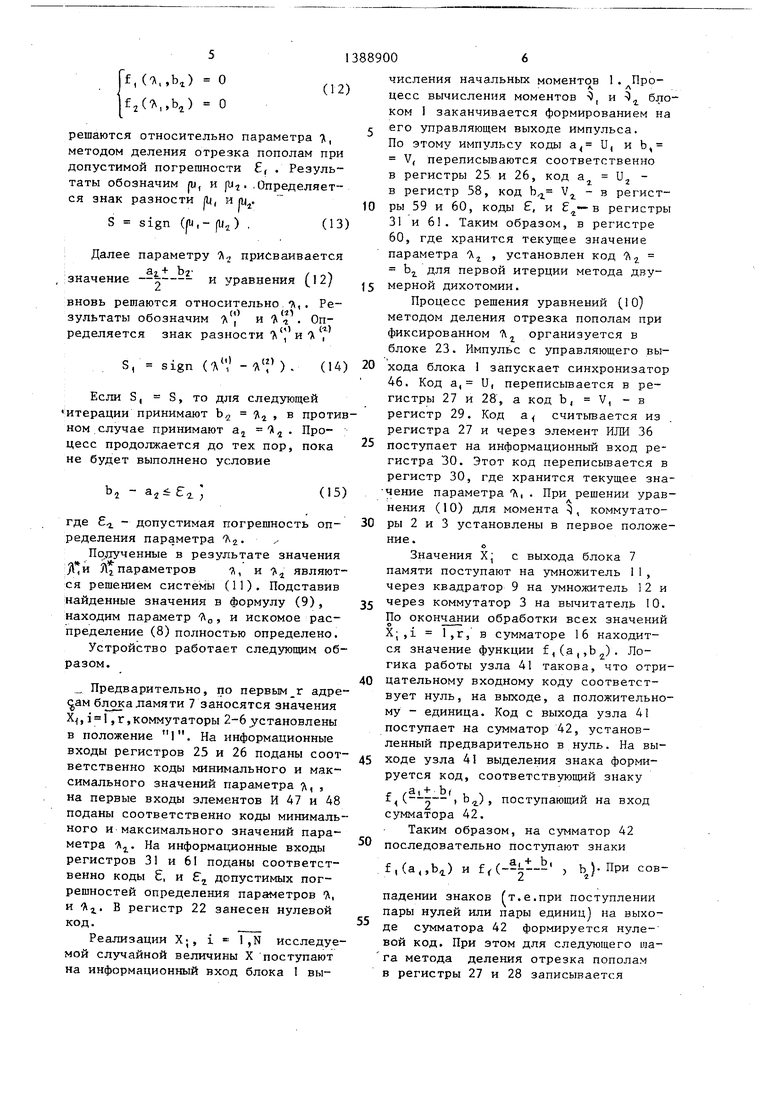

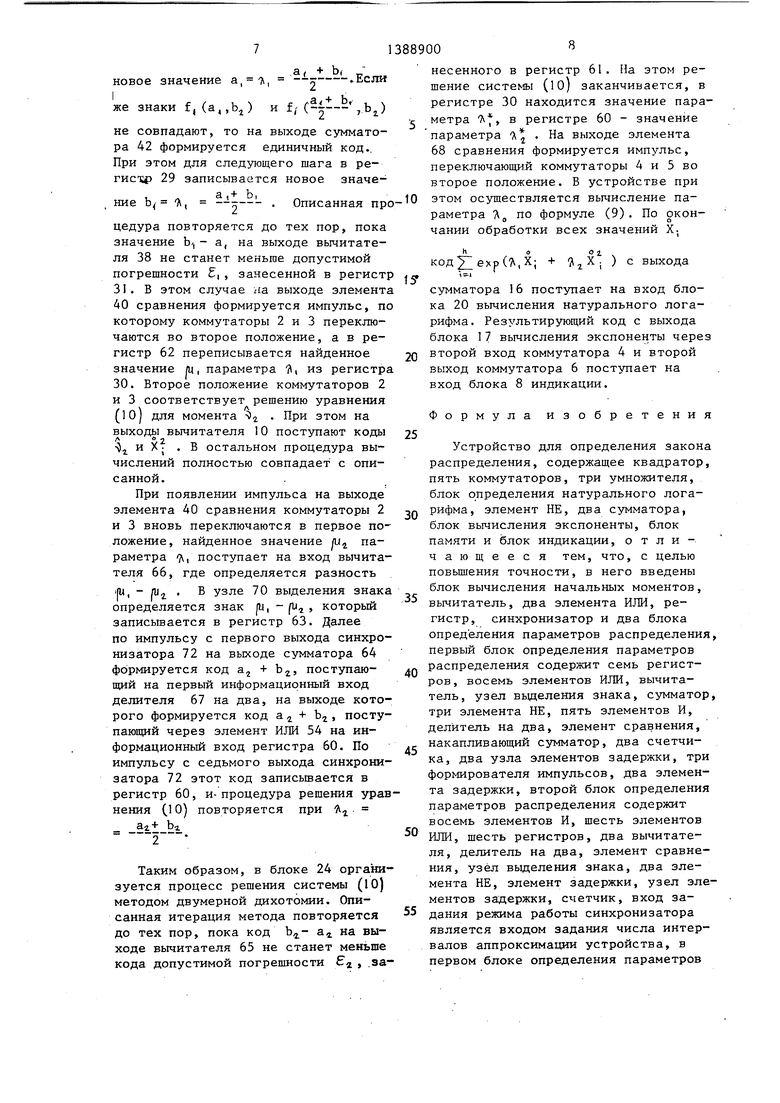

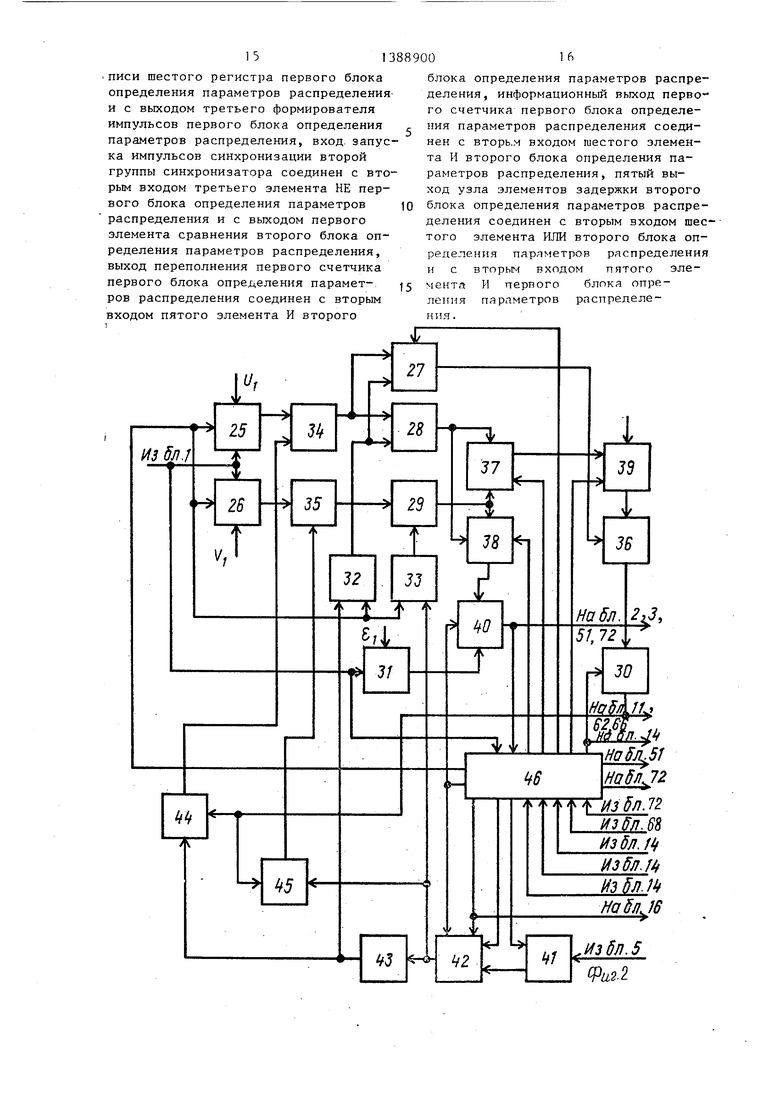

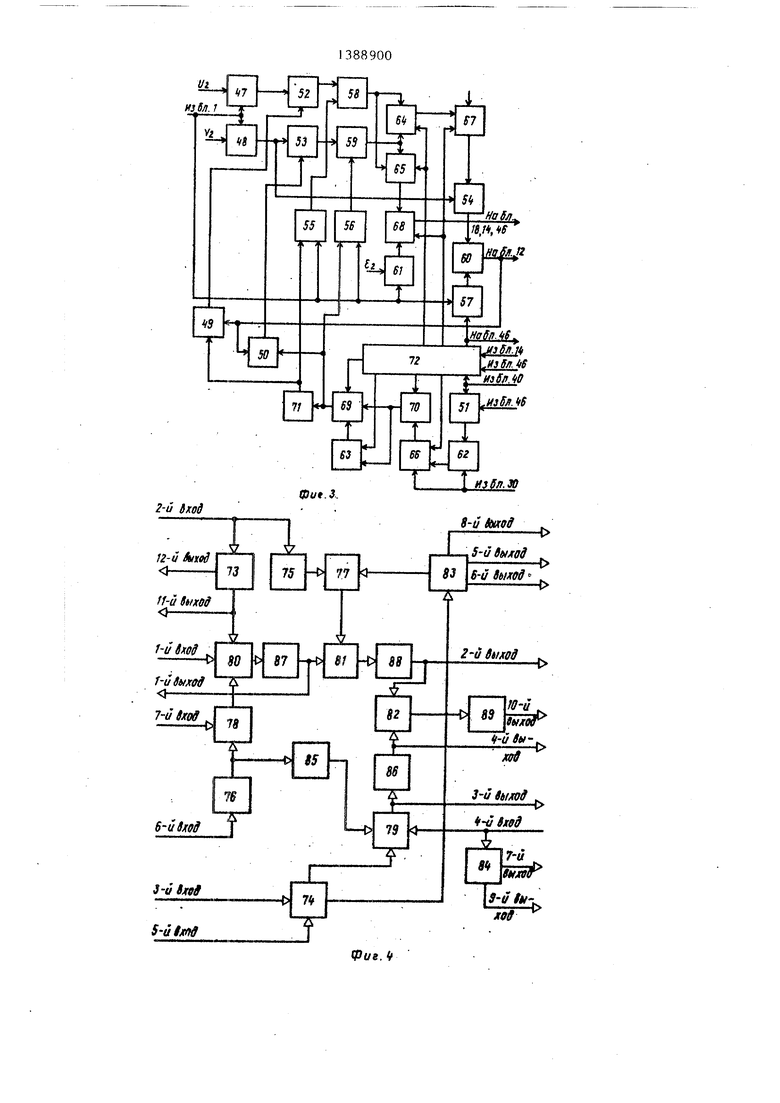

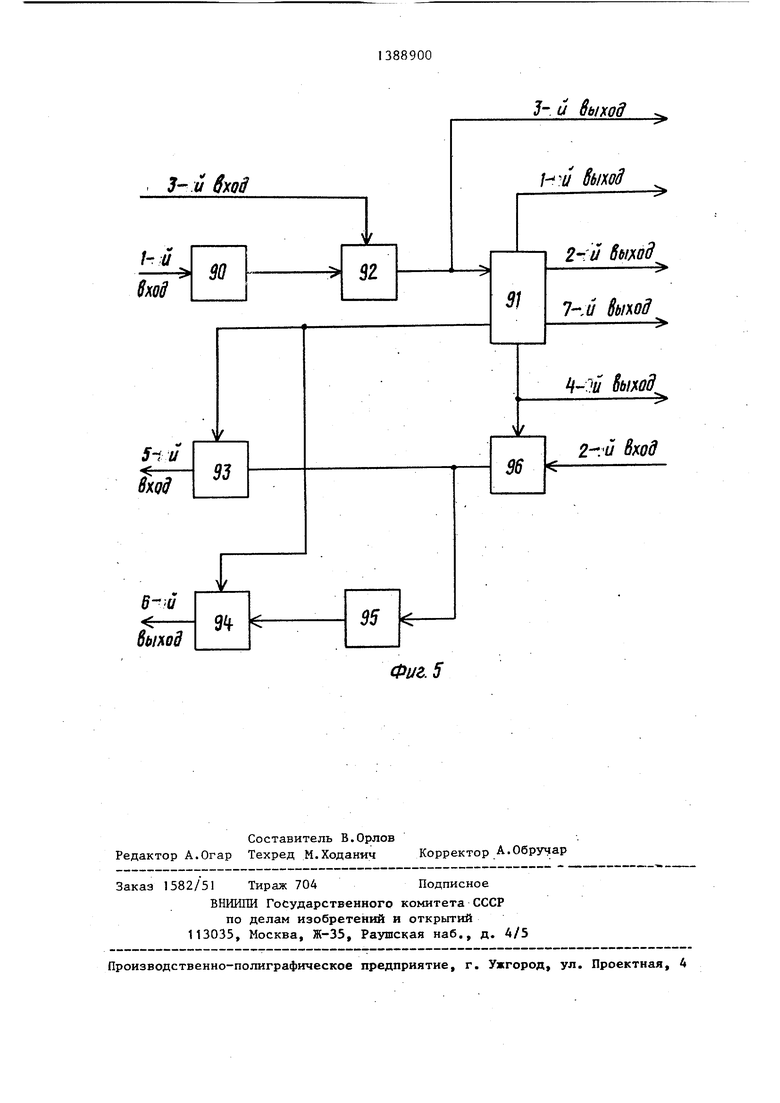

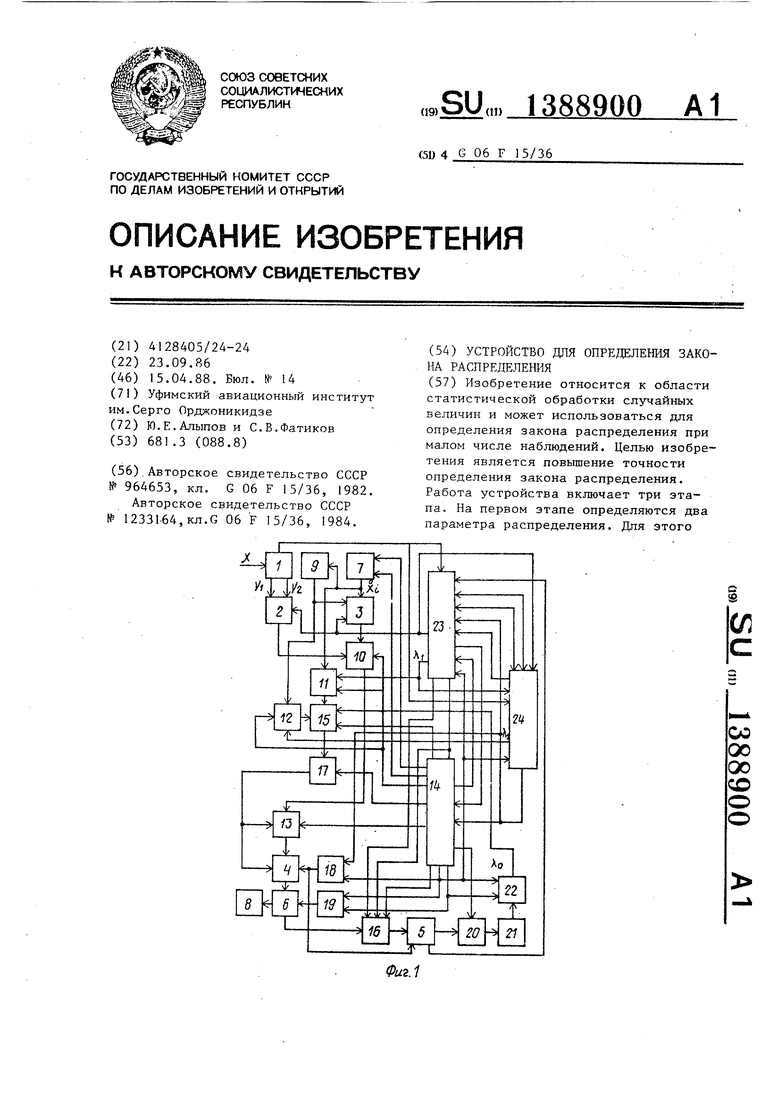

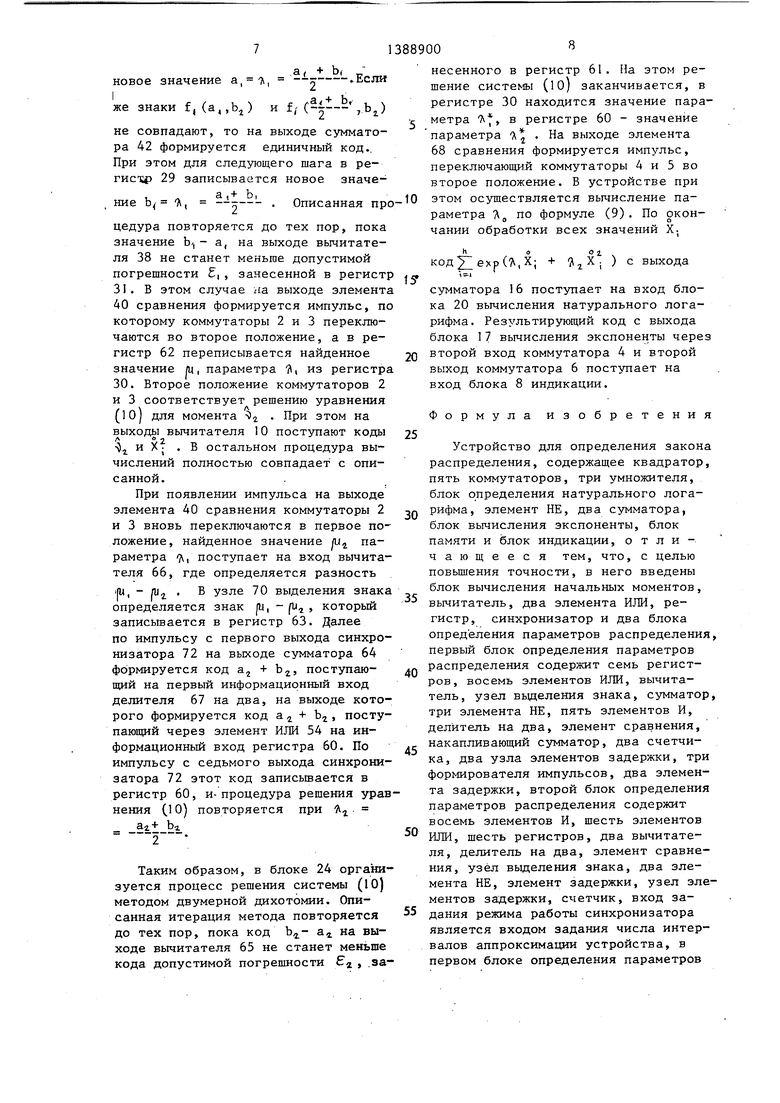

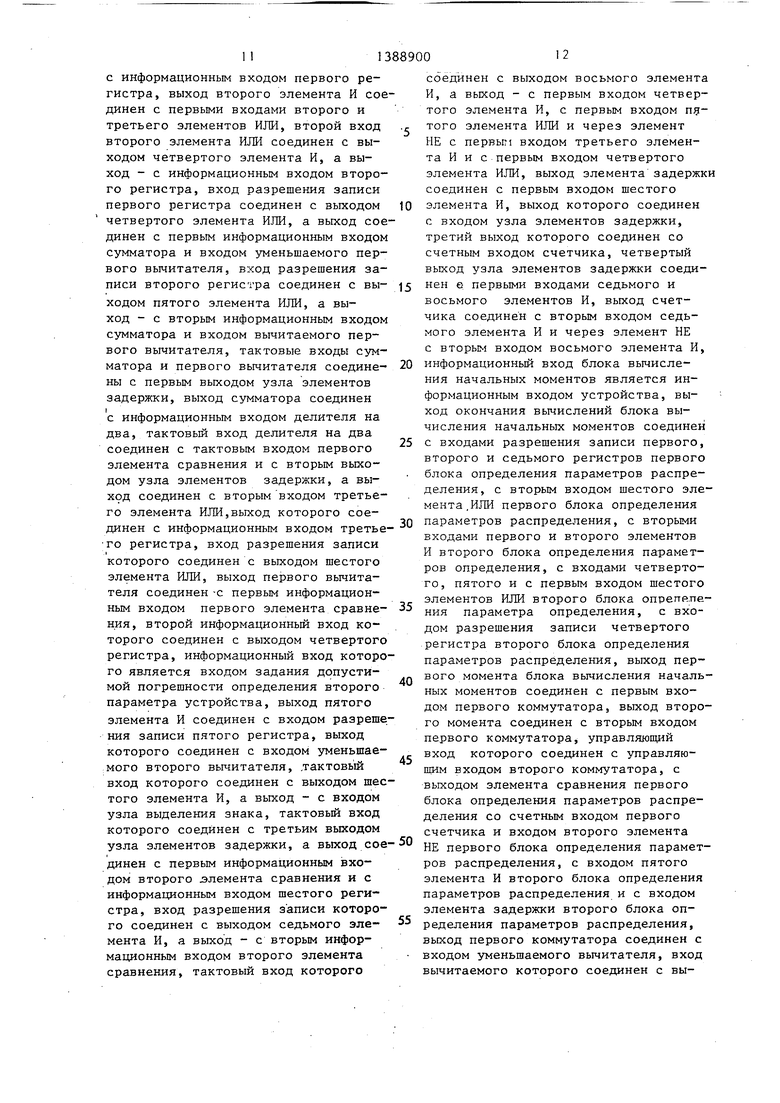

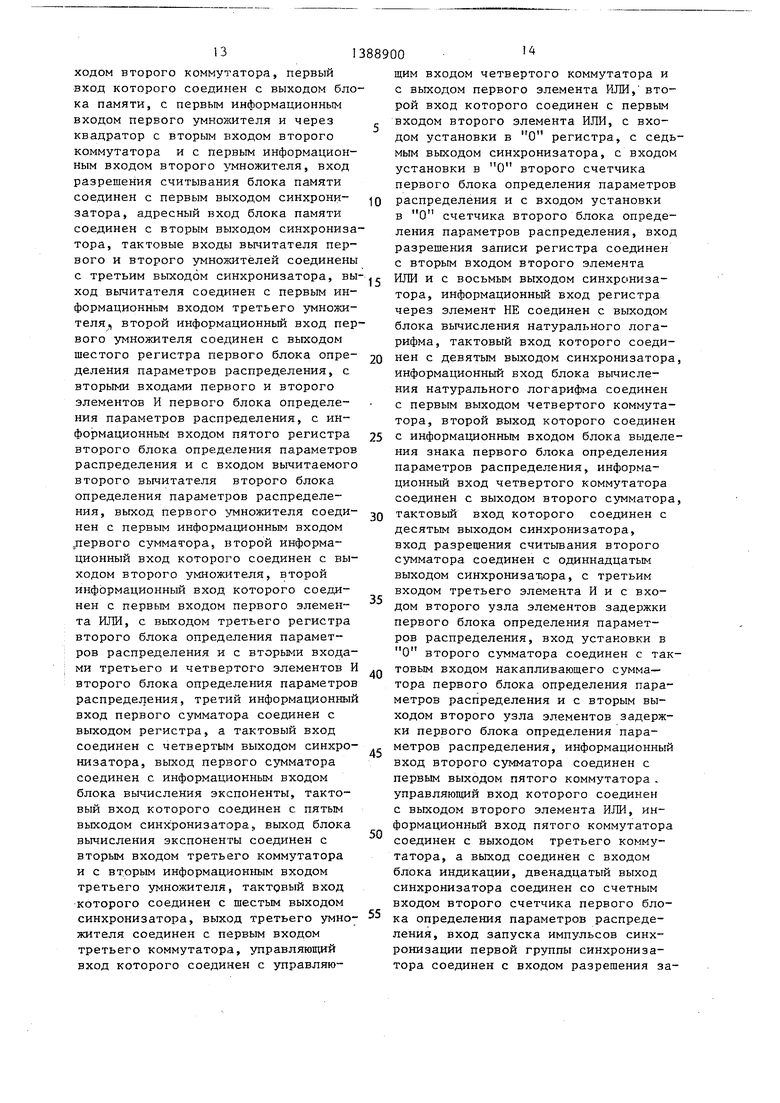

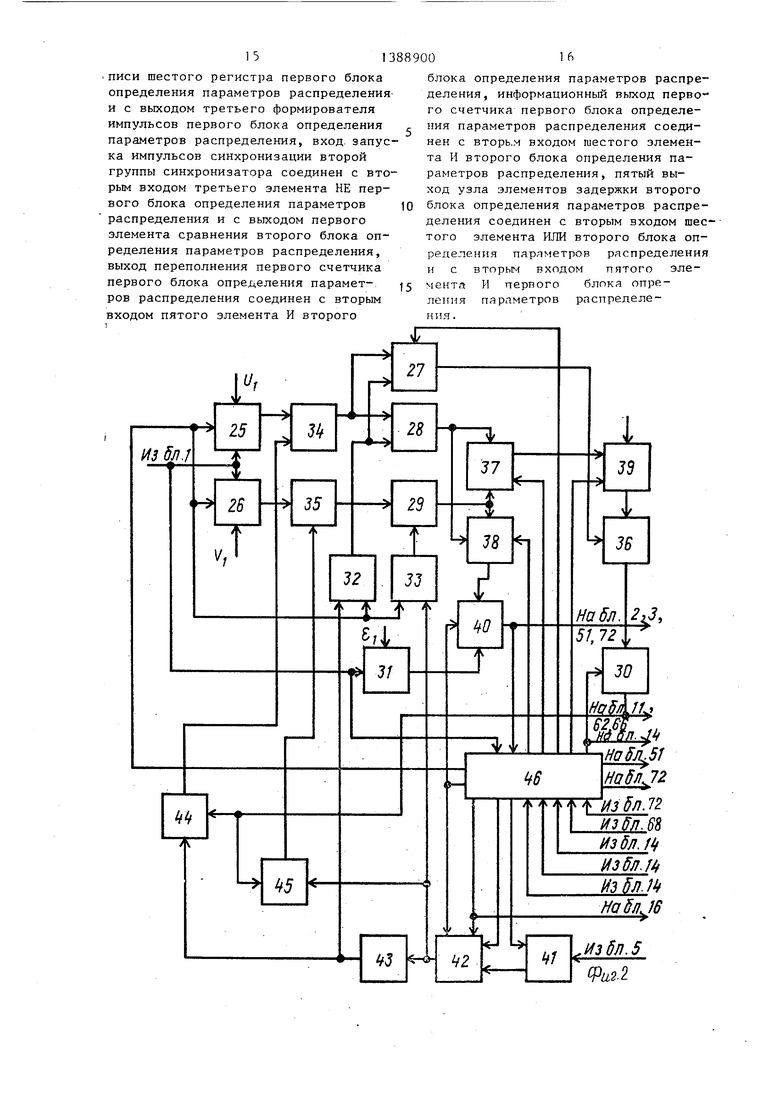

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема первого блока определения параметров распределения на фиг.З - функционахгьная схема вто- рого блока определения параметров распределения; на фиг.4 - функциональная схема синхронизатора первого блока определения параметров распределения; на фиг.З - функциональная схема синхронизатора второго блока определения параметров распределения.

Устройство (фиг.1) содержит блок 1 вычисления начальных моментов, коммутаторы 2-6, блок 7 памяти, блок 8 индикации, квадратор 9, вычитатель 10, умножители 11 - 13, синхронизатор 14, сумматоры 15 и 16 блок 17 вычисления экспоненты, элементы ИЛИ 18 и 19, блок 20 вычисления натурального Логарифма элемент НЕ 21 , регистр 22, блоки определения параметров распределения 23 и и 24.

Блок 23 (фиг.2) образуют регистры 25-31, элементы ИЛИ 32-36, сумматор

ласть неопределенности для искомого параметра сужается. Устройство содержит блок 1 вычисления начальных моментов, коммутаторы 2-6, блок 7 памяти, блок 8 индикации, квадратор 9, вычитатель 10, умножители 11-13, синхронизатор 14, сумматоры 15,16, блок 17 вычисления экспоненты, элементы ИЛИ 18,19, блок 20 вычисления натурального логарифма, элемент НЕ 21, регистр 22, блоки 23,24 определения параметров распределения. 5 ил.

37, вычитатель 38, делитель 39 на два, элемент 40 сравнения, узел 41 выделения знака, накапливающий сумматор 42, элемент НЕ 43, элементы И 44 и 45, синхронизатор 46.

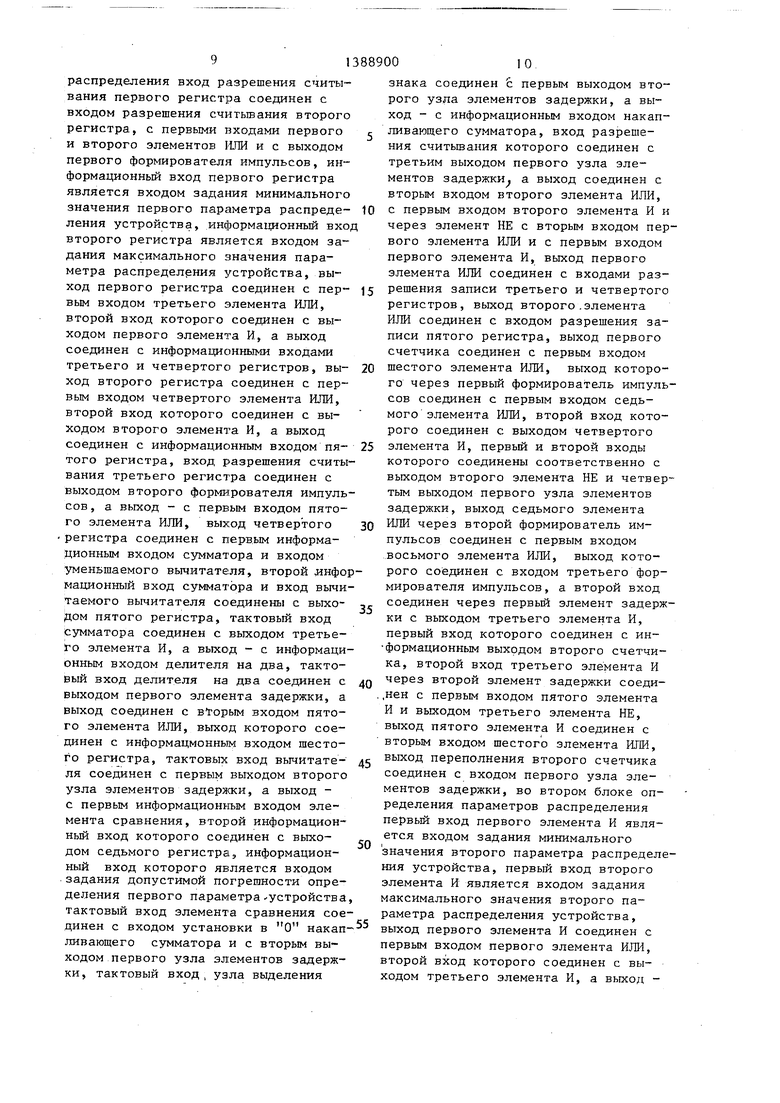

Решающий блок 24 (фиг.З) содержит элементы И 47-51, элементы ИЛИ 52-57, регистры 58-63, сумматор 64, вычитатели .65 и 66, делитель 67 на два, элементы 68 и 69 сравнения, узел 70 выделения знака, элемент НЕ 71 и синхронизатор 72.

Синхронизатор 46 (фиг.4) блока 23 включают счетчики 73 и 74, элементы НЕ 75 и 76, элементы И 77- 79, элементы ИЛИ 80-82, узлы 83 и 84 элементов задержки, элементы 85 и 86 задержки и формирователи 87-89 импульсов.

Синхронизатор 72 (фиг.5) блока 24 содержит элемент 90 задержки, узел 91 элементов задержки, элементы И 92-94, элемент НЕ 95 и счетчик 96.

В основу работы устройства положено использование информационного метода определения закона распределения случайной величины. Метод наиболее эффективен при малом числе наблюдений и отсутствии априорных данных о том, к какому типу принадлежит искомый закон распределения.

Пусть имеется случайная выборка объема N : Х,Х,,...,Х. Пусть статические данные представлены в виде гистограммы с частотами N., N,, . . . ,N,,

31388900

Вероятность того, что в i-й столбец гистограммы попадет ровно N;

в чи

наблюдений, есть

N;

Р Р,. Р;...Р; Р;

(-i- )

Вероятность получения именно наб- людаемой гистограммы N,,N,..jN

Ml I к j. ( ч

.П N;-.l

(-Г-)

Координаты экстремума величины Q Inq/N совпадают с координатами экстремума вероятности q.

Оценки искомых вероятностей

Р| NI/N, i Т . (3) Энтропия исходного распределения

Q, - И

Pi

InP;

При исследовании экстремальных свойств величины Q достаточно ограничиться энтропией распределения Р,,

Р,...,Р. Энтропия должна максимизироваться при ограничениях, вытекающих из результатов наблюдений.

Поскольку все существенные особенности распределений характеризуются их моментами, в качестве ограничений целесообразно выбрать уравнения

J- К ЦХ; Р;

к

К - 1,2,... ,тп 1 (5)

в левой части которых находятся выражения для начальных(моментов искомого распределения, а в правой - оценки этих моментов, вычисленные по имеющимся экспериментальным данным (по выборке :

1

к -й- ,

к 1,2т.(6)

Эти уравнения дополняются условием нормировки

г

ZlPi 1.(7)

Таким образом, решение ищется в классе распределений, первые моменты которых совпадают со статистическими оценками моментов.

10

15

Искомое распределение определяется в результате решения следующей задачи оптимизации: найти вероятности

«-

Р, ,P,...,Рр, доставляющие максимум

функции (4) при ограничениях (5) и (7). Доказано, что оптимальное число учитываемых моментов зависит от числа опытных данных и возрастает с его увеличением. При малых объемах выбор- ки наиболее целесообразно использовать в ограничениях два первых момента.

Ретая поставленнзпо оптимизационную задачу методом неопределенных множителей Лагранжа, получаем выражение для искомого распределения

20

Р ехр ( Д„+ Л,Д; + ),

i 1,г

(В)

25

Параметры распределения о, Л, и определяются при этом следующими уравнениями:

г

02

„ - 1п Цехр (,Х; + ,Х;)

(9)

30

,4

(X, ехр (,.)

О,К 1,2

(10)

35

Уравнения (10) являются уравнениями правдоподобия для плотности распределения (8).

Дпя численного решения системы (10) используется метод двумерной дихотомии, основанный на известной процедуре уточнения корней уравнения методом деления отрезка пополам.

I

Алгоритм метода двумерной дихотомии предполагает, что решается система

f, (-А.,-Аг) fi(,)

О

О

(11)

Координаты и, ,V,иг и V характеризуют область, в которой заведомо находится искомое решение: границы области определяются путем предварительных исследований.

Вначале параметру А присваивается значения Ь V и уравнения

.b О (г,,) О

(12)

решаются относительно параметра , методом деления отрезка пополам при допустимой погрешности , . Результаты обозначим nj, и U . .Определяется знак разности Ш, н гц.

S sign (р,- fU,,) , (13)

Далее параметру ,, присваивается

а + Ьг /, г,л

и уравнения (2/

значение

Ревновь решаются относительно Л, зультаты обозначим и А . Определяется знак разности

S, sign Сл, ). (14) 20

Если S, S, то для следующей итерации принимают Ь,;, , в противПроном случае принимают а A,j

цесс продолжается до тех пор, пока

не будет выполнено условие

25

13889006

числения начальных моментов 1. ПроА, Л,

цесс вычисления моментов г ° ком 1 заканчивается формированием на г его управляющем выходе импульса. По этому импульсу коды а и, и Ь, V( переписываются соответственно в регистры 25 и 26, код а U - в регистр 58, код Ь V - в регист10 ры 59 и 60, коды , и регистры 31 и 61. Таким образом, в регистре 60, где хранится текущее значение параметра Х , установлен код Й Ь,, для первой итерции метода двуJ5 мерной дихотомии.

Процесс решения уравнений (10) методом деления отрезка пополам при

фиксированном Л организуется в блоке 23. Импульс с управляющего выхода блока 1 запускает синхронизатор 46. Код а, и, переписывается в регистры 27 и 28, а код Ъ, V, - в регистр 29. Код а считывается из регистра 27 и через элемент ИЛИ 36 поступает на информационный вход регистра 30. Этот код переписывается в регистр 30, где хранится текущее зна чение параметра Ту, . При решении урав нения (10) для момента , коммутаторы 2 и 3 установлены в первое положе ние.

Ь, а Е

2- ;

(15)

где 6 - допустимая погрешность определения параметра -Полученные в результате значения )и Л параметров ,, и являются решением системы (11). Подставив найденные значения в формулу (9), находим параметр Ло , и искомое распределение (8) полностью определено.

Устройство работает следующим образом.

Предварительно, по первьм г адре- ам бтюкаламяти 7 заносятся значения X,i l,г,коммутаторы 2-6установлены в положение 1. На информационные

Значения X; с выхода блока 7 памяти поступают на умножитель 11, через квадратор 9 на умножитель 12 и 35 через коммутатор 3 на вычитатель Ю. По окончании обработки всех значений X;,i 1,г, в сумматоре 16 находится значение функции f(a,). Логика работы узла 41 такова, что отри цательному входному коду соответствует нуль, на выходе, а положительно му - единица. Код с выхода узла 41 поступает на сумматор 42, установленный предварительно в нуль. На вы50

входы регистров 25 и 26 поданы соот- дд оде узла 41 выделения знака форми- ветственно коды минимального и максимального значений параметра т, , на первые входы элементов И 47 и 48 поданы соответственно коды минималь ного и максимального значений параметра . На информационные входы регистров 31 и 61 поданы соответственно коды , и Sj допустимых погпадении знаков fт.е.при поступлении пары нулей или пары единиц на выходе сумматора 42 формируется нулевой код. При этом для следующего шаруется код, соответствующий знаку

f,(--г- , Ь), поступающий на вход сумматора 42.

Таким образом, на сумматор 42 последовательно поступают знаки

f,(a,,b) и f -V-- bJ.HpH соврешностей определения параметров Л, и . В регистр 22 занесен нулевой

код.

Реализации X;, i 1,N исследуемой случайной величины X поступают на информационный вход блока I вы55

га метода деления отрезка пополам в регистры 27 и 28 записывается

фиксированном Л организуется в блоке 23. Импульс с управляющего выхода блока 1 запускает синхронизатор 46. Код а, и, переписывается в регистры 27 и 28, а код Ъ, V, - в регистр 29. Код а считывается из регистра 27 и через элемент ИЛИ 36 поступает на информационный вход регистра 30. Этот код переписывается в регистр 30, где хранится текущее зна- чение параметра Ту, . При решении уравнения (10) для момента , коммутаторы 2 и 3 установлены в первое положение.

Значения X; с выхода блока 7 памяти поступают на умножитель 11, через квадратор 9 на умножитель 12 и через коммутатор 3 на вычитатель Ю. По окончании обработки всех значений X;,i 1,г, в сумматоре 16 находится значение функции f(a,). Логика работы узла 41 такова, что отрицательному входному коду соответствует нуль, на выходе, а положительному - единица. Код с выхода узла 41 поступает на сумматор 42, установленный предварительно в нуль. На узла 41 выделения знака форми-

оде узла 41 выделения знака форми-

руется код, соответствующий знаку

f,(--г- , Ь), поступающий на вход сумматора 42.

Таким образом, на сумматор 42 последовательно поступают знаки

f,(a,,b) и f -V-- bJ.HpH совга метода деления отрезка пополам в регистры 27 и 28 записывается

новое значение а, 7,,

Ьг

.Если

же знаки f, (а,,Ь,) и f/ (--- , Ь)

не совпадают, то на выходе сумматора 42 формируется единичный код.. При этом для следующего шага в регистр 29 записывается новое значение Ь| А,

а,+ Ь,

цедура повторяется до тех пор, пока

1388900

несенного в регистр 61. На этом решение системы (Ю) заканчивается, в регистре 30 находится значение пара- с метра , в регистре 60 - значение параметра Х . На выходе элемента 68 сравнения формируется импульс, переключающий коммутаторы 4 и 5 во второе положение. В устройстве при Описанная про- этом осуществляется вычисление параметра А по формуле (9) . По окончании обработки всех значений X;

значение Ь/, - а, на выходе вьгчитателя 38 не станет меньгае допустимой код 1 ехр (7, Х; + Х ) с выхода

погрешности , , занесенной в регистр л

сумматора 16 поступает на вход блока 20 вычисления натурального логарифма. Результирующий код с выхода блока 17 вычисления экспоненты через второй вход коммутатора 4 и второй

При появлении импульса на выходе элемента 40 сравнения коммутаторы 2 и 3 вновь переключаются в первое положение, найденное значение (U параметра поступает на вход вычитателя 66, где определяется разность ifU, - /Uj . В узле 70 выделения знака определяется знак |И, - fU , который записывается в регистр 63. Далее по импульсу с первого выхода синхронизатора 72 на выходе сумматора 64 формируется код а + Ъ, поступающий на первый информационный вход делителя 67 на два, на выходе которого формируется код а + bj, поступающий через элемент ИЛИ 54 на информационный вход регистра 60. По импульсу с седьмого выхода синхронизатора 72 этот код записьшается в регистр 60, и-процедура решения уравнения (10) повторяется при

2

Таким образом, в блоке 24 организуется процесс решения системы (10) методом двумерной дихотомии. Описанная итерация метода повторяется до тех пор, пока код а,, на выходе вычитателя 65 не станет меньше кода допустимой погрешности Е , .за20

25

30

35

40

45

50

55

выход коммутатора 6 поступает на вход блока 8 индикации.

Формула изобретения

Устройство для определения закона распределения, содержащее квадратор, пять коммутаторов, три умножителя, блок определения натурального логарифма, элемент НЕ, два сумматора, блок вычисления экспоненты, блок памяти и блок индикации, отличающееся тем, что, с целью повьшгения точности, в него введены блок вычисления начальных моментов, вычитатель, два элемента ИЛИ, регистр, синхронизатор и два блока определения параметров распределения, первый блок определения параметров распределения содержит семь регистров, восемь элементов ИЛИ, вычитатель, узел вьщеления знака, сумматор, три элемента НЕ, пять элементов И, делитель на два, элемент сравнения, накапливающий сумматор, два счетчика, два узла элементов задержки, три формирователя импульсов, два элемента задержки, второй блок определения параметров распределения содержит восемь элементов И, шесть элементов ИЛИ, шесть регистров, два вычитателя, делитель на два, элемент сравнения, узел выделения знака, два элемента НЕ, элемент задержки, узел элементов задержки, счетчик, вход задания режима работы синхронизатора является входом задания числа интервалов аппроксимации устройства, в первом блоке определения параметров

.Если

я про

Х

сумматора 16 поступает на вход блока 20 вычисления натурального логарифма. Результирующий код с выхода блока 17 вычисления экспоненты через второй вход коммутатора 4 и второй

0

5

0

5

0

5

0

5

выход коммутатора 6 поступает на вход блока 8 индикации.

Формула изобретения

Устройство для определения закона распределения, содержащее квадратор, пять коммутаторов, три умножителя, блок определения натурального логарифма, элемент НЕ, два сумматора, блок вычисления экспоненты, блок памяти и блок индикации, отличающееся тем, что, с целью повьшгения точности, в него введены блок вычисления начальных моментов, вычитатель, два элемента ИЛИ, регистр, синхронизатор и два блока определения параметров распределения, первый блок определения параметров распределения содержит семь регистров, восемь элементов ИЛИ, вычитатель, узел вьщеления знака, сумматор, три элемента НЕ, пять элементов И, делитель на два, элемент сравнения, накапливающий сумматор, два счетчика, два узла элементов задержки, три формирователя импульсов, два элемента задержки, второй блок определения параметров распределения содержит восемь элементов И, шесть элементов ИЛИ, шесть регистров, два вычитателя, делитель на два, элемент сравнения, узел выделения знака, два элемента НЕ, элемент задержки, узел элементов задержки, счетчик, вход задания режима работы синхронизатора является входом задания числа интервалов аппроксимации устройства, в первом блоке определения параметров

распределения вход разрешения считывания первого регистра соединен с входом разрешения считьшания второго регистра, с первыми входами первого и второго элементов 1ШИ и с выходом первого формироват€шя импульсов, информационный вход первого регистра является входом задания минимального значения первого параметра распреде- 10 ления устройства, информационный вход второго регистра является входом за Дания максимального значения параметра распределения устройства, выход первого регистра соединен с пер- 15 вым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а выход соединен с информационными входами третьего и четвертого регистров, вы- 20 ход второго регистра соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход соединен с информационным входом пя- 25 того регистра, вход, разрешения считывания третьего регистра соединен с выходом второго форми:рователя импульсов , а выход - с первым входом пятого элемента ИЛИ, выход четвертого 30 регистра соединен с первым информационным входом сумматора и входом уменьшаемого вычитателя, второй информационный вход сумматора и вход вычитаемого вычитателя соединены с выходом пятого регистра, тактовый вход сумматора соединен с выходом третьего элемента И, а выход - с информационным входом делителя на два, тактовый вход делителя на два соединен с выходом первого элемента задержки, а выход соединен с в горым входом пятого элемента ИЛИ, выход которого соединен с информацмонным входом шестого регистра, тактовых вход вычитате- дз ля соединен с первым выходом второго узла элементов задерлжи, а выход - с первым информационным входом элемента сравнения, второй информационный вход которого соединен с выходом седьмого регистра, информационный вход которого является входом .задания допустимой погрешности определения первого параметра Устройства, тактовый вход элемента сравнения сое35

40

50

знака соединен с первым выходом в рого узла элементов задержки, а в ход - с информационным входом нак ливающего сумматора, вход разреше ния считьшания которого соединен третьим выходом первого узла элементов задержки, а выход соединен вторым входом второго элемента ИЛ с первым входом второго элемента через элемент НЕ с вторым входом вого элемента ИЛИ и с первым вход первого элемента И, выход первого элемента ИЛИ соединен с входами р решения записи третьего и четверт регистров, выход второго .элемента ИЛИ соединен с входом разрешения писи пятого регистра, выход перво счетчика соединен с первым входом шестого элемента ИЛИ, выход кото го через первый формирователь имп сов соединен с первым входом седь мого элемента ИЛИ, второй вход ко рого соединен с выходом четвертог элемента И, первый и второй входы которого соединены соответственно выходом второго элемента НЕ и чет тым выходом первого узла элементо задержки, выход седьмого элемента ИЛИ через второй формирователь им пульсов соединен с первым входом восьмого элемента ИЛИ, выход кот рого соединен с входом третьего ф мирователя импульсов, а второй вх соединен через первый элемент зад ки с выходом третьего элемента И, первый вход которого соединен с и формационным выходом второго счет ка, второй вход третьего элемента через второй элемент задержки сое ,нен с первым входом пятого элемен И и выходом третьего элемента НЕ, выход пятого элемента И соединен вторым входом шестого элемента ИЛ выход переполнения второго счетчи соединен с входом первого узла эл ментов задержки, во втором блоке ределения параметров распределени первый вход первого элемента И яв ется входом задания минимального значения второго параметра распред ния устройства, первый вход второ элемента И является входом задани максимального значения второго па раметра распределения устройства.

динен с входом установки в О накап- выход первого элемента И соединен

ливающего сумматора и с вторым выходом первого узла элементов задержки, тактовый вход , узла вьщеления

0 5 0 з

5

0

0

знака соединен с первым выходом второго узла элементов задержки, а выход - с информационным входом накапливающего сумматора, вход разрешения считьшания которого соединен с третьим выходом первого узла элементов задержки, а выход соединен с вторым входом второго элемента ИЛИ, с первым входом второго элемента И и через элемент НЕ с вторым входом первого элемента ИЛИ и с первым входом первого элемента И, выход первого элемента ИЛИ соединен с входами разрешения записи третьего и четвертого регистров, выход второго .элемента ИЛИ соединен с входом разрешения записи пятого регистра, выход первого счетчика соединен с первым входом шестого элемента ИЛИ, выход которого через первый формирователь импульсов соединен с первым входом седьмого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первый и второй входы которого соединены соответственно с выходом второго элемента НЕ и четвертым выходом первого узла элементов задержки, выход седьмого элемента ИЛИ через второй формирователь импульсов соединен с первым входом восьмого элемента ИЛИ, выход которого соединен с входом третьего формирователя импульсов, а второй вход соединен через первый элемент задержки с выходом третьего элемента И, первый вход которого соединен с ин- формационным выходом второго счетчика, второй вход третьего элемента И через второй элемент задержки соеди- ,нен с первым входом пятого элемента И и выходом третьего элемента НЕ, выход пятого элемента И соединен с вторым входом шестого элемента ИЛИ, выход переполнения второго счетчика соединен с входом первого узла элементов задержки, во втором блоке определения параметров распределения первый вход первого элемента И является входом задания минимального значения второго параметра распределения устройства, первый вход второго элемента И является входом задания максимального значения второго параметра распределения устройства.

выход первого элемента И соединен

первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, а выход

1 11

с информационным входом первого регистра, выход второго элемента И соединен с первыми входами второго и третьего элементов ИЛИ, второй вход второго элемента ИЛИ соединен с выходом четвертого элемента И, а выход - с информационным входом второго регистра, вход разрешения записи первого регистра соединен с выходом четвертого элемента ИЛИ, а выход соединен с первым информационным входом сумматора и входом уменьшаемого первого вычитателя, вход разрешения записи второго регистра соединен с выходом пятого элемента ИЛИ, а выход - с вторым информационным входом сумматора и входом вычитаемого первого вычитателя, тактовые входы сумматора и первого вычитателя соединены с первым выходом узла элементов задержки, выход сумматора соединен

с информационньпу входом делителя на два, тактовый вход делителя на два соединен с тактовым входом первого элемента сравнения и с вторым вько- дом узла элементов задержки, а выход соединен с вторым входом третье

соединен с выходом восьмо И, а вькод - с первым вхо того элемента И, с первым того элемента ИЛИ и через НЕ с первыг входом третье та И и с первым входом че элемента ИЛИ, выход элеме соединен с первым входом элемента И, выход которог с входом узла элементов з третий выход которого сое счетным входом счетчика, выход узла элементов заде нен е первыми входами сед восьмого элементов И, вы чика соединен с вторым вх мого элемента И и через э с вторым входом восьмого информационный вход блока ния начальных моментов яв формационным входом устро ход окончания вьмислений числения начальных момент с входами разрешения запи второго и седьмого регист блока определения парамет деления, с вторым входом мента,ИЛИ первого блока о

входами первого и второго И второго блока определен

го элемента ИЛИ,выход которого сое,30 параметров распределения,

динен с информационным входом третье- - i- г i ,

го регистра, вход разрешения записи которого соединен с выходом шестого элемента ИЛИ, выход первого вычитателя соединен -с первым информационным входом первого элемента сравне- 35

ров определения, с входам го, пятого и с первым вхо элементов ИЛИ второго бло ния параметра определен дом разрешения записи ч регистра второго блока оп параметров распределения, вого момента блока вычисл ных моментов соединен с п дом первого коммутатора, го момента соединен с вто первого коммутатора, упра вход которого соединен с щим входом второго коммут выходом элемента сравнени блока определения парамет деления со счетным входом счетчика и входом второго НЕ первого блока определе ров распределения, с входо элемента И второго блока параметров распределения и элемента задержки второго ределения параметров распр выход первого коммутатора входом уменьшаемого вычита вычитаемого которого соеди

ния, второй информационньш вход которого соединен с выходом четвертого регистра, информационный вход которого является входом задания допустимой погрешности определения второго параметра устройства, выход пятого элемента И соединен с входом разрешения записи пятого регистра, выход которого соединен с входом зтеньшае- мого второго вычитателя, .тактовый вход которого соединен с выходом шестого элемента И, а выход - с входом узла выделения знака, тактовый вход которого соединен с третьим выходом узла элементов задержки, а выход сое динен с первым информационным входом второго элемента сравнения и с информационным входом шестого регистра, вход разрешения записи которого соединен с выходом седьмого элемента И, а выход - с вторым информационным входом второго элемента сравнения, тактовый вход которого

12

соединен с выходом восьмого элемента И, а вькод - с первым входом четвертого элемента И, с первым входом пятого элемента ИЛИ и через элемент НЕ с первыг входом третьего элемента И и с первым входом четвертого элемента ИЛИ, выход элемента задержки соединен с первым входом шестого элемента И, выход которого соединен с входом узла элементов задержки, третий выход которого соединен со счетным входом счетчика, четвертый выход узла элементов задержки соединен е первыми входами седьмого и восьмого элементов И, выход счетчика соединен с вторым входом седьмого элемента И и через элемент НЕ с вторым входом восьмого элемента И, информационный вход блока вычисления начальных моментов является информационным входом устройства, выход окончания вьмислений блока вычисления начальных моментов соединен с входами разрешения записи первого, второго и седьмого регистров первого блока определения параметров распределения, с вторым входом шестого элемента,ИЛИ первого блока определения

с вторыми

входами первого и второго элементов И второго блока определения параметпараметров распределения,

i- г i ,

5

0

5

0

5

ров определения, с входами четвертого, пятого и с первым входом шестого элементов ИЛИ второго блока опрепр.ле- ния параметра определения, с входом разрешения записи четвертого регистра второго блока определения параметров распределения, выход первого момента блока вычисления начальных моментов соединен с первым входом первого коммутатора, выход второго момента соединен с вторьм входом первого коммутатора, управляющий вход которого соединен с управляющим входом второго коммутатора, с выходом элемента сравнения первого блока определения параметров распределения со счетным входом первого счетчика и входом второго элемента НЕ первого блока определения параметров распределения, с входом пятого элемента И второго блока определения параметров распределения и с входом элемента задержки второго блока определения параметров распределения, выход первого коммутатора соединен с входом уменьшаемого вычитателя, вход вычитаемого которого соединен с вы

13

ходом второго коммутатора, первый вход которого соединен с выходом блка памяти, с первым информационным входом первого умнойсителя и через квадратор с вторым входом второго коммутатора и с первым информационным входом второго умножителя, вход разрешения считывания блока памяти соединен с первым выходом синхронизатора, адресный вход блока памяти соединен с вторым выходом синхронизтора, тактовые входы вычитателя первого и второго умнолсителей соединен с третьим выходом синхронизатора, в ход вычитателя соединен с первым информационным входом третьего умнояси теля, второй информационный вход певого умножителя соединен с выходом шестого регистра первого блока определения параметров распределения, с вторьп-м входами первого и второго элементов И первого блока определ€;- ния параметров распределения, с информационным входом пятого регистра второго блока определения параметро распределения и с входом вычитаемог второго вычитателя второго блока определения параметров распределения, выход первого лмножителя соединен с первым информационным входом первого сумматора, второй информационный вход которого соединен с выходом второго умножителя, второй информационный вход которого соединен с первым входом первого элемента ИЛИ, с выходом третьего регистра второго блока определения параметров распределения и с вторыми входами третьего и четвертого элементов второго блока определения параметро распределения, третий информационгш вход первого сумматора соединен с выходом регистра, а тактовый вход соединен с четвертым выходом синхронизатора, выход первого сумматора соединен с информационным входом блока вычисления экспоненты, тактовый вход которого соединен с пятым выходом синхронизатора, выход блока вычисления экспоненты соединен с вторым входом третьего коммутатора и с вторым информационным входом третьего умножителя, тактовый вход которого соединен с шестым выходом синхронизатора, выход третьего умножителя соединен с первым входом третьего коммутатора, управляющий вход которого соединен с управляю

14

0

5

0

5

0

5

0

5

щим входом четвертого коммутатора и с выходом первого элемента ИЛИ, второй вход которого соединен с первым входом второго элемента ИЛИ, с входом установки в О регистра, с седьмым выходом синхронизатора, с входом установки в О второго счетчика первого блока определения параметров распределения и с входом установки в О счетчика второго блока определения параметров распределения, вход разрешения записи регистра соединен с вторым входом второго элемента ИЛИ и с восьмым выходом синхронизатора, информационный вход регистра через элемент НЕ соединен с выходом блока вычисления натурального логарифма, тактовый вход которого соединен с девятым выходом синхронизатора, информационный вход блока вычисления натурального логарифма соединен с первым выходом четвертого коммутатора, второй выход которого соединен с информационным входом блока выделения знака первого блока определения параметров распределения, информационный вход четвертого коммутатора соединен с выходом второго сумматора, тактовый вход которого соединен с десятым выходом синхронизатора, вход разрешения считьтания второго сумматора соединен с одиннадцатым выходом синхронизатоора, с третьим входом третьего элемента И и с входом второго узла элементов задержки первого блока определения параметров распределения, вход установки в О второго сумматора соединен с тактовым входом накапливающего сумматора первого блока определения параметров распределения и с вторым выходом второго узла элементов задержки первого блока определения параметров распределения, информационный вход второго сумматора соединен с первым выходом пятого коммутатора , управляющий вход которого соединен с выходом второго элемента ИЛИ, информационный вход пятого коммутатора соединен с выходом третьего коммутатора, а выход соединён с входом блока индикации, двенадцатый выход синхронизатора соединен со счетным входом второго счетчика первого блока определения параметров распределения, вход запуска импульсов синхронизации первой группы синхронизатора соединен с входом разрешения заJS

зв

На 5л.

51,72,,

2,

МАШ

Шл

.72

MlMJ H36njif

H36fl.Jff

J3MJ Наблюю

Избп.5

(Ра2.2

Фиг.З.

2-й бход

HjSn.X

8-и iMoff

яв9

(риг. ff

Фиг. 5

| Статистический анализатор | 1980 |

|

SU964653A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО ДЛЯ ВЫТАЛКИВАНИЯ САХАРНЫХ ГОЛОВ И СУХОЙ ОБРЕЗКИ | 1928 |

|

SU12331A1 |

Авторы

Даты

1988-04-15—Публикация

1986-09-23—Подача