сл

Физ.1

тор 15, коммутатор 16, регистр 17 частичных сумм, блок 18 определения номера старшего значащего разряда, дешифратор 19, регистр 20 номера разряда, регистр 21 сдвига номера

разряда, преобразователь 22 прямого кода в дополнительный, второй сумматор 23, регистр 24 начального значения, группу элементов И 25, блок 26 управления. 2 з.п., 8 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

Изобретение относится к вычислительной технике и предназначено для построения устройств для решения задач математической физики, описываемых дифференциальными уравнениями в частных производных. Цель изобретения - повышение быстродействия. Узел содержит регистры 1-4 коэффициентов, регистр 5 правой части, коммутаторы 6-9, преобразователи 10-14 прямого кода в дополнительный, первый сумматор 15, коммутатор 16, регистр 17 частичных сумм, блок 18 определения номера старшего значащего разряда, дешифратор 19, регистр 20 номера разряда, регистр 21 сдвига номера разряда, преобразователь 22 прямого кода в дополнительный, второй сумматор 23, регистр 24 начального значения, группу элементов И 25, блок 26 управления. 2 з.п. ф-лы, 8 ил.

Изобретение относится к вычислительной технике и предназначено для построения устройств для решения задач математической физики, описываемых дифференциальными уравнениями в частных производных.

Цель изобретения - повьш1ение бьТст- родействия.

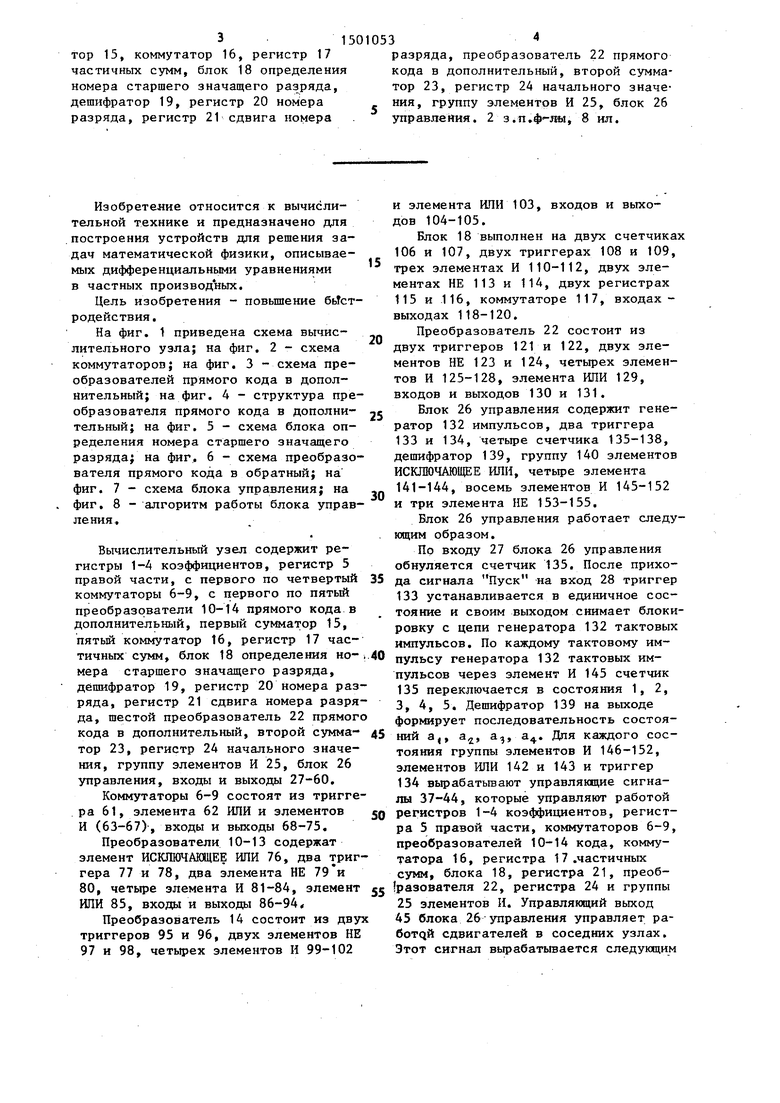

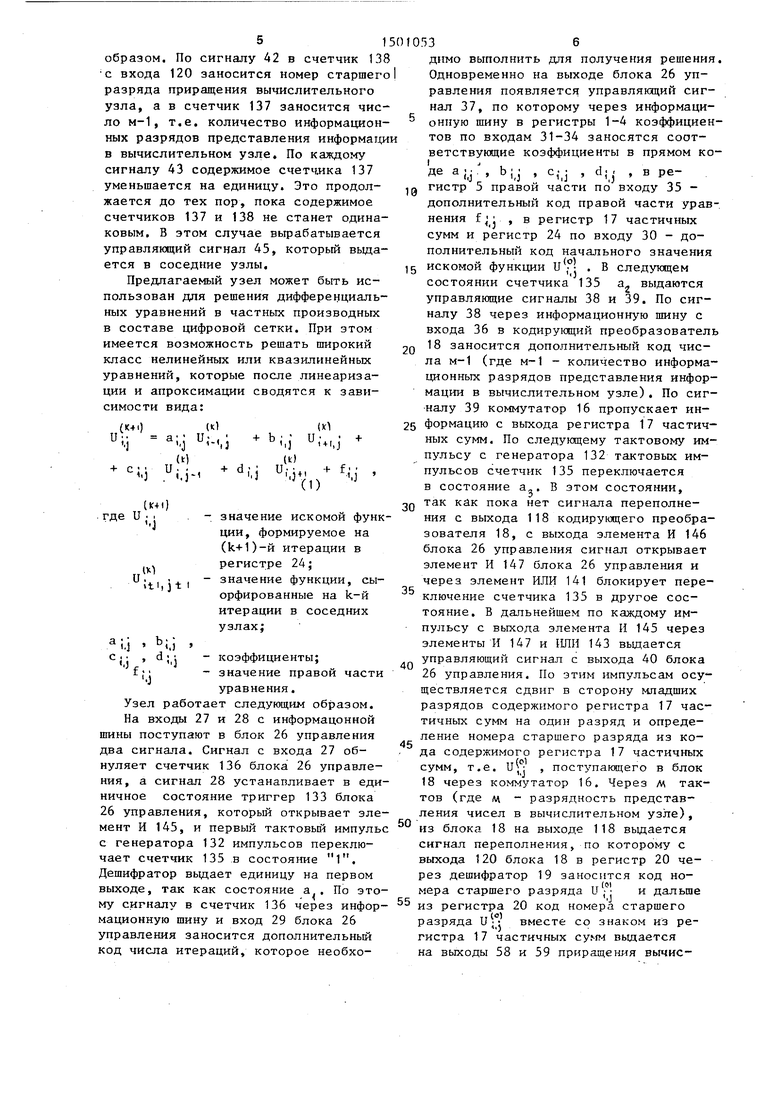

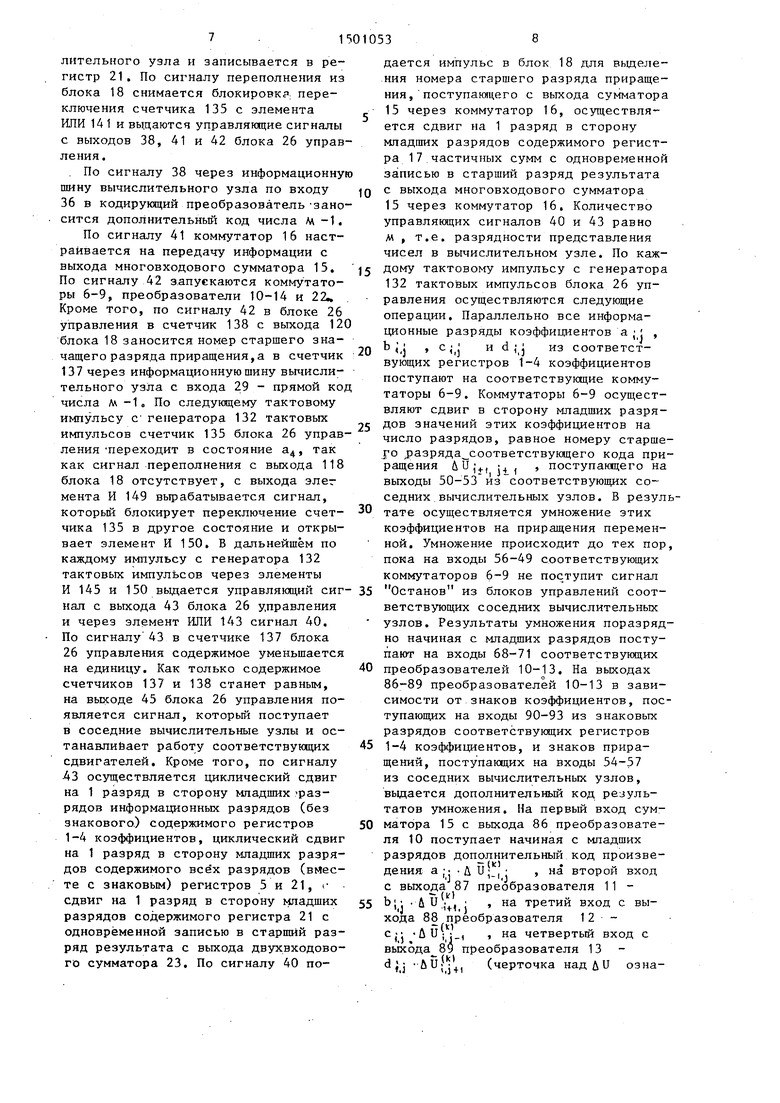

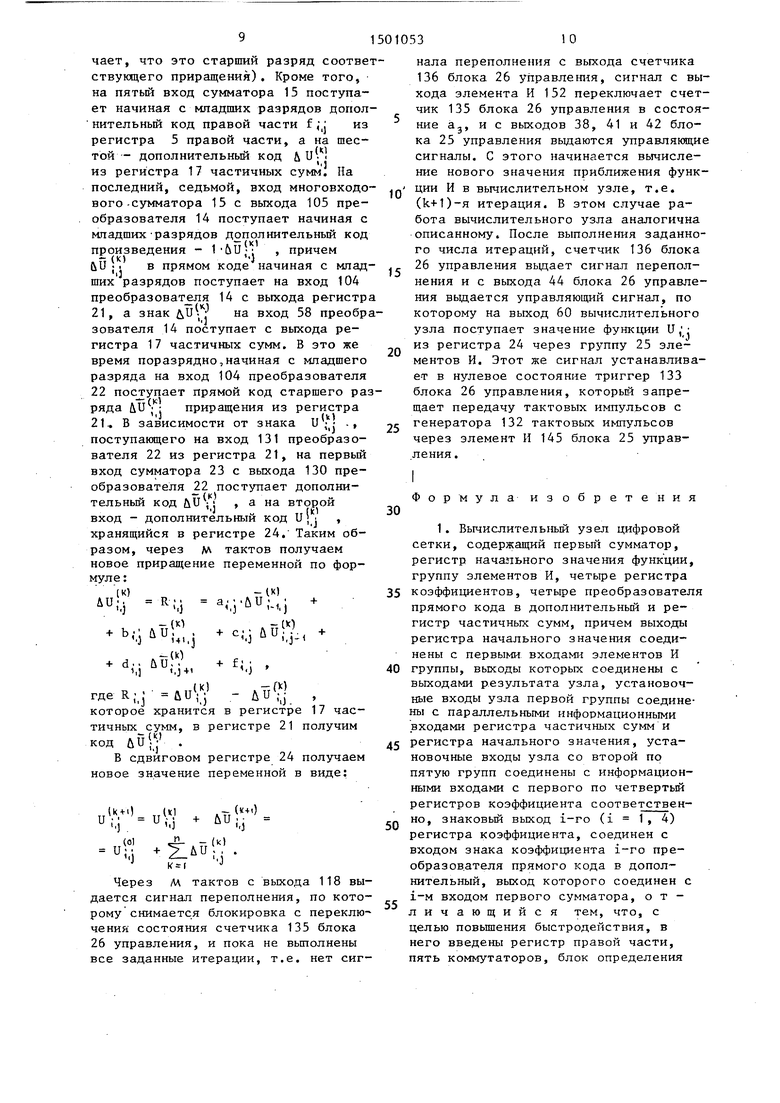

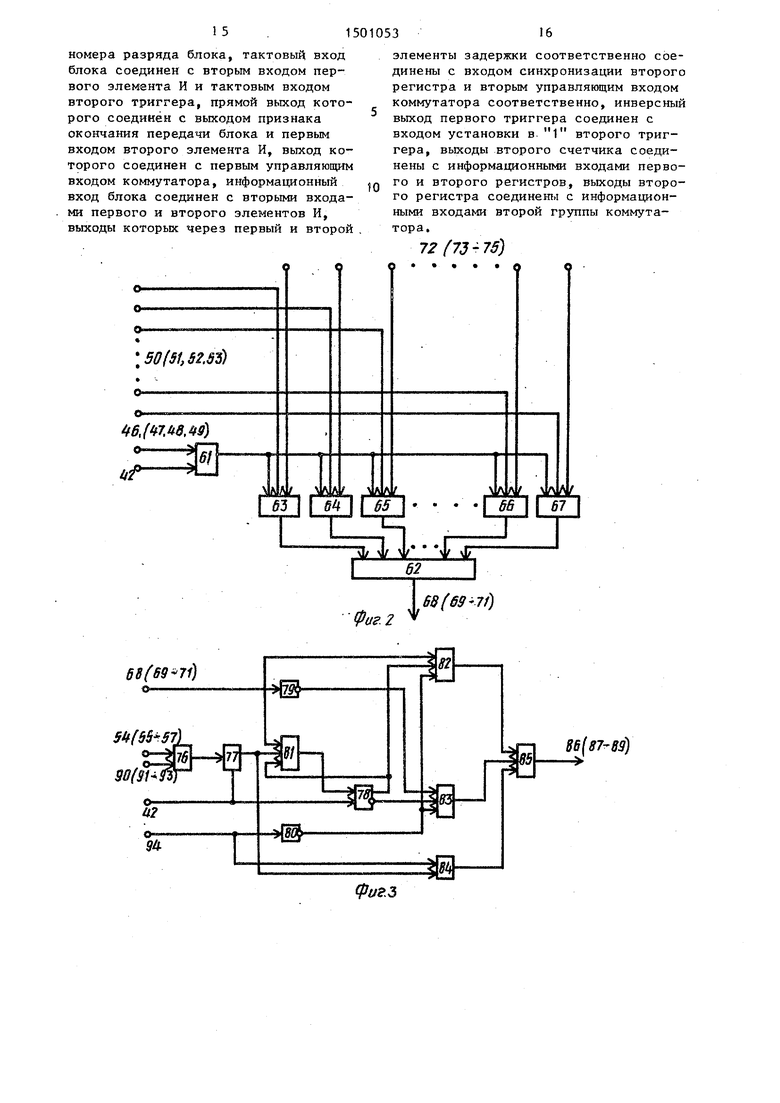

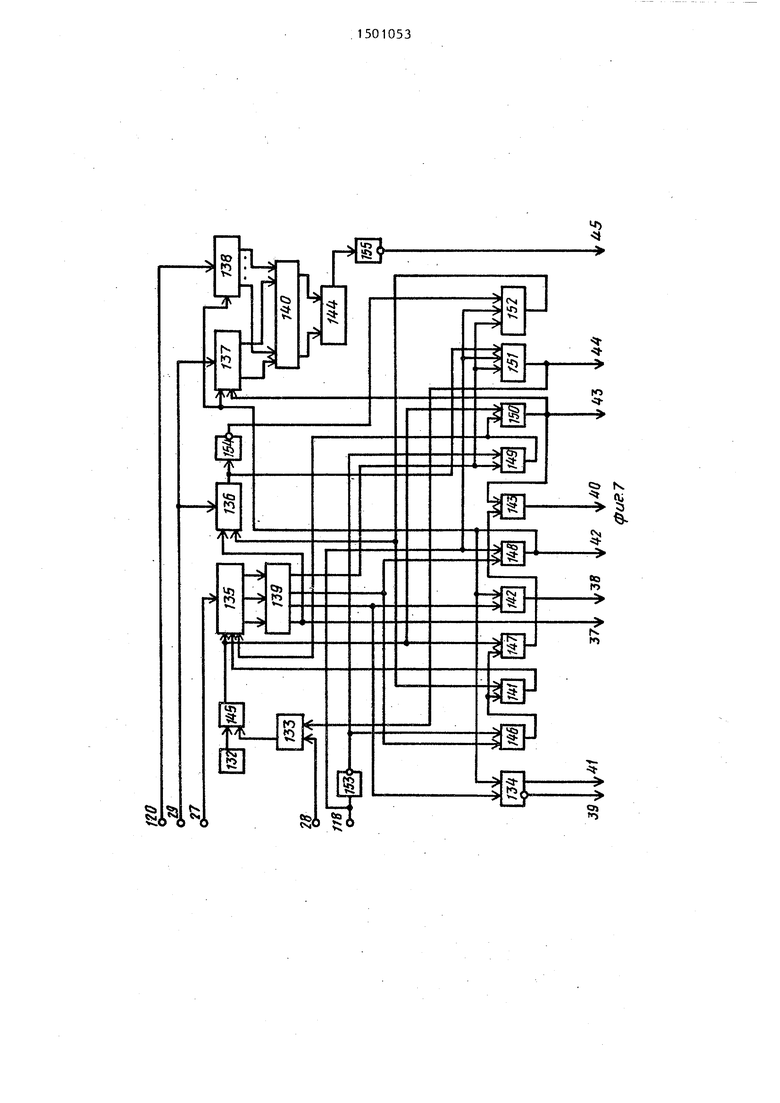

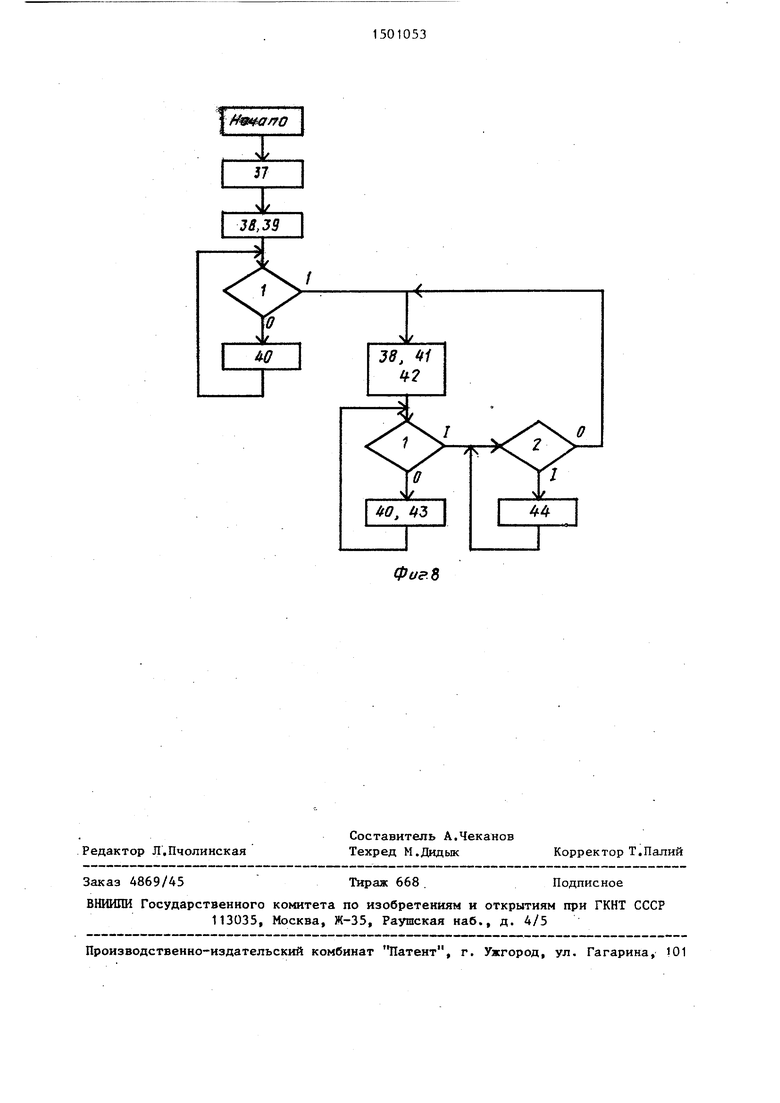

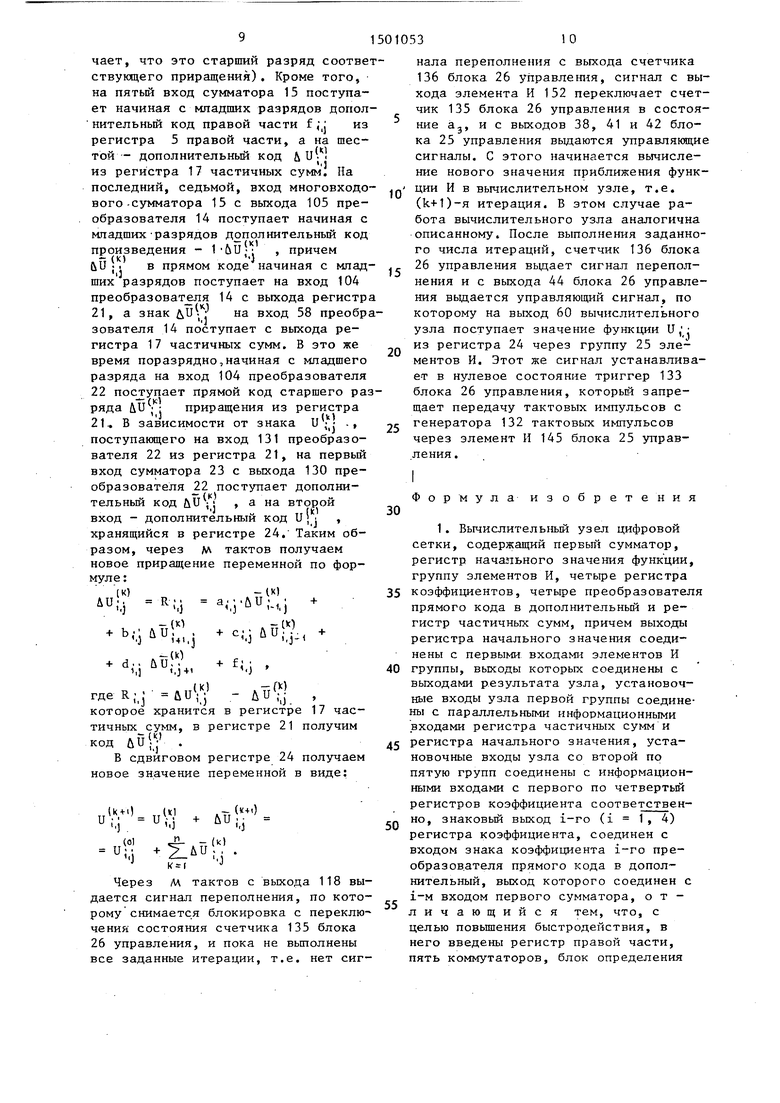

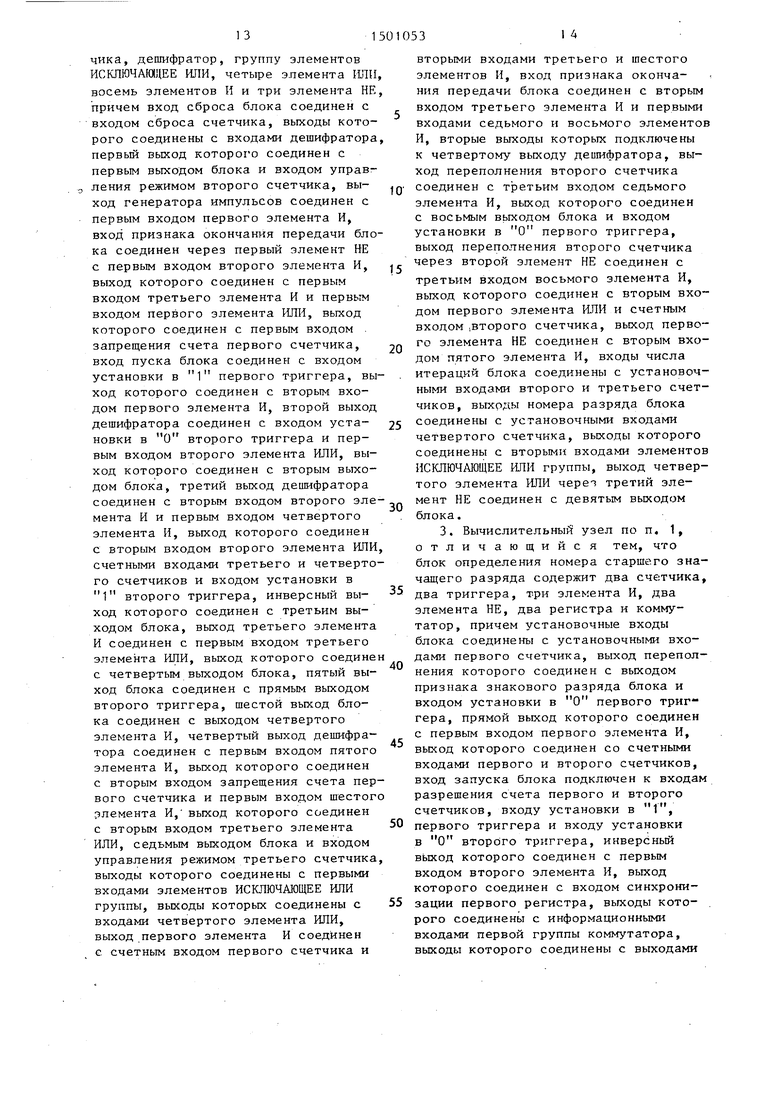

На фиг. 1 приведена схема вычислительного узла; на фиг, 2 - схема коммутаторов; на фиг. 3 - схема преобразователей прямого кода в дополнительный; на фиг. 4 - структура преобразователя прямого кода в дополни- тельный; на фиг. 5 - схема блока определения номера старшего значащего разряда; на фиг. 6 - схема преобразователя прямого кода в обратный; на фиг. 7 - схема блока управления; на фиг. В - алгоритм работы блока управления.

Вычислительный узел содержит регистры 1-4 коэффициентов, регистр 5 правой части, с первого по четвертый коммутаторы 6-9, с первого по пятый преобразователи 10-14 прямого кода в дополнительный, первый сумматор 15, пятьй коммутатор 16, регистр 17 частичных сумм, блок 18 определения номера старшего значащего разряда, дешифратор 19, регистр 20 номера разряда, регистр 21 сдвига номера разряда, шестой преобразователь 22 прямог кода в дополнительный, второй сумма- тор 23, регистр 24 начального значения, группу элементов И 25, блок 26 управления, входы и выходы 27-60.

Коммутаторы 6-9 состоят из триггера 61, элемента 62 ИЛИ и элементов И (63-67), входы и выходы 68-75.

Преобразователи 10-13 содержат элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 76, два триггера 77 и 78, два элемента НЕ 80, четыре элемента И 81-84, элемент ИЛИ 85, входы и выходы 86-94«

Преобразователь 14 состоит из дву триггеров 95 и 96, двух элементов НЕ 97 и 98, четырех элементов И 99-102

0

s

5 0 5

Q

j

и элемента ИЛИ 103, входов и выходов 104-105.

Блок 18 выполнен на двух счетчиках 106 и 107, двух триггерах 108 и 109, трех элементах И 110-112, двух элементах НЕ 113 и 114, двух регистрах 115 и 116, коммутаторе 117, входах - выходах 118-120.

Преобразователь 22 состоит из двух триггеров 121 и 122, двух элементов НЕ 123 и 124, четырех элементов И 125-128, элемента ИЛИ 129, входов и выходов 130 и 131.

Блок 26 управления содержит генератор 132 импульсов, два триггера 133 и 134, четыре счетчика 135-138, дешифратор 139, группу 140 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, четьфе элемента 141-144, восемь элементов И 145-152 и три элемента НЕ 153-155.

Блок 26 управления работает следующим образом.

По входу 27 блока 26 управления обнуляется счетчик 135. После прихода сигнала Пуск на вход 28 триггер

133устанавливается в единичное состояние и своим выходом снимает блокировку с цепи генератора 132 тактовых импульсов. По каждому тактовому импульсу генератора 132 тактовых импульсов через элемент И 145 счетчик 135 переключается в состояния 1, 2, 3, 4, 5, Дешифратор 139 на выходе формирует последовательность состояний а, а, а, а. Для каждого состояния группы элементов И 146-152, элементов ИЛИ 142 и 143 и триггер

134вьфабатьгаают управляющие сигналы 37-44, которые управляют работой регистров 1-4 коэффициентов, регистра 5 правой части, коммутаторов 6-9, преобразователей 10-14 кода, коммутатора 16, регистра 17 .частичных сумм, блока 18, регистра 21, преоб разователя 22, регистра 24 и группы 25 элементов И. Управляющий выход 45 блока 26 управления управляет ра- бoтQй сдвигателей в соседних узлах. Этот сигнал вырабатьшается следующим

51

образом. По сигналу 42 в счетчик 138 с входа 120 заносится номер старшего разряда приращения вычислительного узла, а в счетчик 137 заносится число м-1, т.е. количество информацион- ных разрядов представления информаци в вычислительном узле. По каждому сигналу 43 содержимое счетчика 137 уменьшается на единицу. Это продол- жается до тех пор, пока содержимое счетчиков 137 и 138 не станет одинаковым. В этом случае вырабатывается управляющий сигнал 45, который выдается в соседние узлы.

Предлагаемый узел может быть использован дпя решения дифференциальных уравнений в частных производных в составе цифровой сетки. При этом имеется возможность решать широкий класс нелинейных или квазилинейных уравнений, которые после линеаризации и апроксимации сводятся к зависимости вида:

(К41) (1с1 М

i

(t)

J (t)

О

Ч .Ui.jn - df,j U,,j.. f... ,

{(t+0

где U;. . - значение искомой функции, формируемое на (К+1)-й итерации в . регистре 24; и. , .. . - значение функции, сыvt fjTi

орфированные на k-й итерации в соседних узлах;

i.j i.J

Cjj . d;: - коэффициенты;

О ,

- значение правой части уравнения.

Узел работает следующим образом.

На входы 27 и 28 с информацонной шины поступают в блок 26 управления два сигнала. Сигнал с входа 27 обнуляет счетчик 136 блока 26 управления, а сигнал 28 устанавливает в единичное состояние триггер 133 блока 26 управления, который открывает элемент И 145, и первый тактовый импуль с генератора 132 импульсов переключает счетчик 135 в состояние 1, Дешифратор вьщает единицу на первом выходе, так как состояние а . По этому сигналу в счетчик 136 через инфор мационную шину и вход 29 блока 26 управления заносится дополнительный код числа итераций, которое необхо

д g

п

5

0

с

)

5

536

димо выполнить для получения решения. Одновременно на выходе блока 26 управления появляется управляющий сигнал 37, по которому через информационную шину в регистры 1-4 коэффициентов по входам 31-34 заносятся соответствующие коэффициенты в прямом коДе а-. bjj , c,.j , djj. , в регистр 5 правой части по входу 35 - дополнительный код правой части уравнения fj , в регистр 17 частичных сумм и регистр 24 по входу 30 - дополнительный код начального значения искомой функции и ; . В следугацем состоянии счетчика 135 а- выдаются управляющие сигналы 38 и 39. По сигналу 38 через информационную шину с входа 36 в кодирующий преобразователь 18 заносится дополнительный код числа м-1 (где м-1 - количество информационных разрядов представления информации в вычислительном узле). По сигналу 39 коммутатор 16 пропускает информацию с выхода регистра 17 частичных сумм. По следующему тактовому импульсу с генератора 132 тактовых импульсов счетчик 135 переключается в состояние а . В этом состоянии, так как пока нет сигнала переполнения с выхода 118 кодирующего преобразователя 18, с выхода элемента И 146 блока 26 управления сигнал открывает элемент И 147 блока 26 управления и через элемент ИЛИ 141 блокирует переключение счетчика 135 в другое состояние. В дальнейшем по каждому ин- пульсу с выхода элемента И 145 через элементы И 147 и ИЛИ 143 вьщается управляющий сигнал с выхода 40 блока 26 управления. По этим импульсам осуществляется сдвиг в сторону младших разрядов содержимого регистра 17 частичных сумм на один разряд и определение номера старшего разряда из кода содержимого регистра 17 частичных сумм, т.е. Uj; , поступающего в блок 18 через коммутатор 16. Через /м тактов (где м - разрядность представления чисел в вычислительном узле), из блока 18 на выходе 118 вьщается сигнал переполнения, по которому с выхода 120 блока 18 в регистр 20 через дешифратор 19 заносятся код номера старшего разряда U

(W

О

и дальше

из регистра 20 код номера старшего разряда и ° вместе со знаком из регистра 17 частичных вьщается на выходы 58 и 59 приращения вычислнтельного узла и записывается в регистр 21. По сигналу переполнения из блока 18 снимается блокировкя переключения счетчика 135 с элемента РШИ 14 1 и выдаются управляющие сигналы с выходов 38, 41 и 42 блока 26 управления.

. По сигналу 38 через информационную шину вычислительного узла по входу 36 в кодирующий преобразователь Заносится дополнительный код числа М -1. По сигналу 41 коммутатор 16 настраивается на передачу информации с выхода многовходового сумматора 15. По сигналу 42 запускаются коммутаторы 6-9, преобразователи 10-14 и 22., Кроме того, по сигналу 42 в блоке 26 управления в счетчик 138 с выхода 120 блока 18 заносится номер старшего значащего разряда приращения, а в счетчик 137 через информационную шину вьпшсли- тельного узла с входа 29 - прямой код числа М -1б По следукщему тактовому импульсу С генератора 132 тактовых импульсов счетчик 135 блока 26 управления переходит в состояние а, так как сигнал переполнения с выхода 118 блока 18 отсутствует, с выхода элег мента И 149 вырабатывается сигнал, которьй блокирует переключение счетчика 135 в другое состояние и открывает элемент И 150. В дальнейшем по каждому импульсу с генератора 132 тактовых импульсов через элементы

И 145 и 150 вьщается управляющий сиг- 35 Останов из блоков управлений соотнап с выхода 43 блока 26 управления и через элемент ИЛИ 143 сигнал 40. По сигналу 43 в счетчике 137 блока 26 управления содержимое уменьшается на единицу. Как только содержимое счетчиков 137 и 138 станет равным, на выходе 45 блока 26 управления появляется сигнал, который поступает в соседние вычислительные узлы и ос- танавлийает работу соответствующих сдвигателей. Кроме того, по сигналу ЛЗ осуществляется циклический сдвиг на 1 разряд в сторону младших разрядов информационных разрядов (без знакового.) содержимого регистров 1-4 коэффициентов, циклический сдвиг на 1 разряд в сторону младших разрядов содержимого всех разрядов (вместе с знаковым) регистров 5 и 21, с сдвиг на 1 разряд в сторону младших разрядов содержимого регистра 21 с одновременной записью в старший разряд результата с выхода двухвходово- го сумматора 23. По сигналу 40 по

5

0

5

дается импульс в блок 18 для выделения номера старшего разряда приращения, поступающего с выхода сумматора 15 через коммутатор 16, осуществляется сдвиг на 1 разряд в сторону младших разрядов содержимого регистра 1 7 частичных сумм с одновременной записью в старший разряд результата с выхода многовходового сумматора 15 через коммутатор 16. Количество управляняцих сигналов 40 и 43 равно М , т.е. разрядности представления чисел в вычислительном узле. По каждому тактовому импульсу с генератора 132 тактовых импульсов блока 26 управления осуществляются следующие операции. Параллельно все информационные разряды коэффициентов а Ь ,j с , и d из вующих регистров 1-4 коэффициентов поступают на соответствующие коммутаторы 6-9. Коммутаторы 6-9 осуществляют сдвиг в сторону младших разрядов значений этих коэффициентов на число разрядов, равное номеру старше- JO .разряда соответствукщего кода приЧсоответстращения i U

i- i JH

поступающего на

0

выходы 50-53 из соответствующих соседних вычислительных узлов. В результате осуществляется умножение этих коэффициентов на приращения переменной. Умножение происходит до тех пор, пока на входы 56-49 соответствующих коммутаторов не поступит сигнал

ветствующих соседних вычислительных узлов. Результаты умножения поразрядно начиная с младших разрядов поступают на входы 68-71 соответствующих преобразователей 10-13. На выходах 86-89 преобразователей 10-13 в зависимости от знаков коэффициентов, пос тупающих на входы 90-93 из знаковых разрядов соответствующих регистров 1-4 коэффициентов, и знаков приращений, поступающих на входы 54-57 из соседних вычислительных узлов, выдается дополнительный код результатов умножения. На первый вход сумматора 15 с выхода 86 преобразователя 10 поступает начиная с младших

разрядов дополнительный код произвеV г;(; дения а; -Д U; , на второй вход

с вькода 87 преобразователя 11 - Ь;; -Ли . . ; , на третий вход с вы (J Tit 1

хода 88 преобразователя 12- с;; Ли:: , , на четвертый вход с 8 Г

выхода d

t.J

преобразователя 13 (черточка над ДU означает, что это старпшй разряд соотвествующего приращения). Кроме того, на пятьш вход сумматора 15 поступает начиная с младших разрядов допол нительный код правой части f; из регистра 5 правой части, а на шестой - дополнительный код ii u ) из регистра 17 частичных сумм. Па последний, седьмой, вход многовходо вого-сумматора 15 с выхода 105 преобразователя 14 поступает начиная с младших-разрядов дополнительный код произведения - 1 , причем Ьи 1 в прямом коде начиная с младIJ

ших разрядов поступает на вход 104 преобразоват я 14 с выхода регистр 21, а знак на вход 58 преобрзователя 14 поступает с выхода регистра 17 частичных сумм. В это же время поразрядно,начиная с младшего разряда на вход 104 преобразователя 22 поступает прямой код старшего раз- fK

ряда ли ; приращения из регистра 2 К В зависимости от знака U ., поступающего на вход 131 преобразователя 22 из регистра 21, на первый вход сумматора 23 с выхода 130 преобразователя 22 поступает дополнительный код UU ; , а на второй вход - дополнительный код U ; , хранящийся в регистре 24. Таким образом, через тактов получаем новое приращение переменной по формуле :

-IK)

ли

1«)

J

R

О

где R;,j uu ;j - которое хранится в регистре

17 частичных сумм, в регистре 21 получим код uU|.,y .

В сдвиговом регистре 24 получаем новое значение переменной в виде:

) и

- (V + 0

ли;,

(0)

J

- (к)

«ч

k f

Через М тактов с выхода 118 выдается сигнал переполнения, по которому снимается блокировка с переключения состояния счетчика 135 блока 26 управления, и пока не выполнены все заданные итерации, т.е. нет сиг0

5

0

5

нала переполнения с выхода счетчика 136 блока 26 управления, сигнал с выхода элемента И 152 переключает счетчик 135 блока 26 управления в состояние а, и с выходов 38, 41 и 42 блока 25 управления вьщаются управлякядие сигналы. С этого начинается вычисление нового значения приближения функции И в вычислительном узле, т.е. (k+1)-H итерация. В этом случае работа вычислительного узла аналогична описанному. После выполнения заданного числа итераций, счетчик 136 блока 26 управления выдает сигнал переполнения и с выхода 44 блока 26 управления вьщается управляющий сигнал, по которому на выход 60 вычислительного узла поступает значение функции U, из регистра 24 через группу 25 элементов И. Этот же сигнал устанавливает в нулевое состояние триггер 133 блока 26 управления, который запрещает передачу тактовых импульсов с генератора 132 тактовых импульсов через элемент И 145 блока 25 управления .

30

Формула изобретения

0

5

0

5

сетки,

, содержащий первьш сумматор, регистр начального значения функции, группу элементов И, четыре регистра 5 коэффициентов, четыре преобразователя прямого кода в дополнительный и регистр частичных сумм, причем выходы регистра начального значения соединены с первыми входами элементов И группы, выходы которых соединены с выходами результата узла, установочные входы узла первой группы соединены с параллельными информационными входами регистра частичных сумм и регистра начального значения, установочные входы узла со второй по пятую групп соединены с информационными входами с первого по четвертый регистров коэффициента соответствен- но, знаковый выход i-ro (i 1, 4) регистра коэффициента, соединен с входом знака коэффициента i-ro преобразователя прямого кода в дополнительный, выход которого соединен с i-M входом первого сумматора, отличающийся тем, что, с целью повьшения быстродействия, в него введены регистр правой части, пять коммутаторов, блок определения

номера старшего значащего разряда, регистр номера разряда, дешифратор, блок управления, регистр сдвига номера разряда, второй сумматор, пятый и шестой преобразователи прямого кода в дополнительный, причем информационные выходы регистра коэффициента ( i 1,А), подключенные к информационным входам i-ro коммутатора, выход которого соединен с ин- формационным входом i-ro преобразователя прямого кода в дополнительный, входы номера разряда узла i-й группы (i 1,4) соединены с входами номера канала i-ro«коммутатора, вход останова которого соединен с i-M входом останова узла, выход первого сумматора соединен с первым информационным входом пятого коммутатора, выход которого соединен с информационным входом блока определения номера старшего значащего разряда и последовательным информационным входом

10

150105312

в дополнительный, выход которот о соединен первым входом второго сумматора, выход которого соединен с последовательным входом регистра начального значения, последовательный выход которого соединен с вторым входом второго сумматора, выход знака регистра частичных сумм соединен с входами знака пятого преобразователя прямого кода в дополнительный и регистра сдвига номера разряда и с вы- ходом знака приращеьшя узла, i-й (i 1,4) вход знака приращения узла подключен к входу знака приращения i-ro преобразователя прямого кода в дополнительный, входы сброса, пуска и числа итераций узла соединены с одноименными входами блока управления, первый выход которого соединен с входами синхронизации записи регистров коэффициентов, регистра частичных сумм, регистра начального значения и регистра правой части, второй

15

20

регистра частичных сумм, информацион-jj выход блока управления соединен

ный выход которого соединен с вторым информационным входом пятого коммутатора и пятым входом первого сумматора, установочные входы узла шестой группы подключены к информационным входам регистра правой части, выход которого соединен с шестым входом первого сумматора, седьмой вход которого соединен с выходом пятого преобразователя прямого кода в дополнительный, выходы номера разряда блока определения номера старшего значащего разряда соединены с входами номера разряда блока управления и входами дешифратора, выходы которого соединены с информационными входами регистра номера разряда, вьпсоды которого Соединены с выходами информационных разрядов приращения узла, и с информационными входами регистра сдвига номера разряда, информацион- ньй выход которого соединен с информационными входами пятого и шестого преобразователей прямого кода в дополнительный, выход признака окончания передачи кода блока определе- ния номера старшего значащего разряда соединен с входом признака окончания передачи блок а управления rf входами синхроимпульсов записи, регистра номера разряда и регистра сдвига номера разряда, знаковый выход которого соединен с входом знака шестого преобразователя прямого кода

30

35

40

45

50

55

входом запуска блока определения мера старшего значащего разряда тий выход блока управления соеди с первым управляющим входом пят коммутатора, четвертьй выход бло управления соединен с тактовым в блока определения номера старше значащего разряда, пятый выход управления соединен с вторым упр ляЯицим входом пятого коммутатор шестой выход блока управления со нен с входами пуска преобразоват прямого кода в. дополнительный, с мой выход блока управления соеди с входами синхроимпульса сдвига гистров коэффициентов, регистра вой части, регистра сдвига номер разряда и регистра начального зн ния, восьмой выход блока управле соединен с вторыми входами элеме И группы, девятый выход блока уп ления соединен с управляющим вых узла, установочные входы седьмой группы узла соединены с установо ми входами блока определения ном старшего значащего разряда, выхо признака знакового разряда котор соединен с входом выдачи результ преобразователей прямого кода в полнительный,

j выход блока управления соединен

0

5

0

5

0

5

входом запуска блока определения номера старшего значащего разряда, третий выход блока управления соединен с первым управляющим входом пятого коммутатора, четвертьй выход блока управления соединен с тактовым входом блока определения номера старшего значащего разряда, пятый выход блока управления соединен с вторым управ- ляЯицим входом пятого коммутатора, шестой выход блока управления соединен с входами пуска преобразователей прямого кода в. дополнительный, седьмой выход блока управления соединен с входами синхроимпульса сдвига регистров коэффициентов, регистра правой части, регистра сдвига номера разряда и регистра начального значения, восьмой выход блока управления соединен с вторыми входами элементов И группы, девятый выход блока управления соединен с управляющим выходом узла, установочные входы седьмой группы узла соединены с установочными входами блока определения номера старшего значащего разряда, выход признака знакового разряда которого соединен с входом выдачи результата преобразователей прямого кода в дополнительный,

5

0

5

вторыми входами третьего и шестого элементов И, вход признака окончания передачи блока соединен с вторым входом третьего элемента И и первыми входами седьмого и восьмого элементов И, вторые выходы которых подключены к четвертому выходу дешифратора, выход переполнения второго счетчика Q соединен с третьим входом седьмого элемента И, выход которого соединен с восьмым вьгходом блока и входом установки в О первого триггера, выход переполнения второго счетчика через второй элемент НЕ соединен с третьим входом восьмого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ и счетным входом ..второго счетчика, выход первого элемента НЕ соединен с вторым входом пятого элемента И, входы числа итераций блока соединены с установочными входами второго и третьего счетчиков, выходы номера разряда блока соединены с установочными входами четвертого счетчика, выходы которого соединены с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выход четвертого элемента ИЛИ черет третий элемент НЕ соединен с девятым выходом блока.

3, Вычислительный узел по п, 1, отличающийся тем, что блок определения номера старшего значащего разряда содержит два счетчика, два триггера, три элемента И, два элемента НЕ, два регистра и коммутатор, причем установочные входы блока соединены с установочными входами первого счетчика, выход переполнения которого соединен с выходом признака знакового разряда блока и входом установки в О первого триггера, прямой выход которого соединен с первым входом первого элемента И, выход которого соединен со счетными входами первого и второго счетчиков, вход запуска блока подключен к входам разрешения счета первого и второго счетчиков, входу установки в 1, первого триггера и входу установки в О второго триггера, инверсный вькод которого соединен с первым входом второго элемента И, выход которого соединен с входом синхрони- 5 зации первого регистра, выходы которого соединены с информационными входами первой группы коммутатора, выходы которого соединены с выходами

0

5

0

5

0

номера разряда блока, тактовый вход блока соединен с вторым входом первого элемента И и тактовым входом второго триггера, прямой выход которого соединён с выходом признака окончания передачи блока и первым входом второго элемента И, выход которого соединен с первым управляющим входом коммутатора, информационный вход блока соединен с вторыми входами первого и второго элементов И, выходы которых через первый и второй

фиг 2

68(

5fff8S

90(Si

9

элементы задержки соответственно соединены с входом синхронизации второго регистра и вторым управляющим входом коммутатора соответственно, инверсный выход первого триггера соединен с входом установки в 1 второго триггера, выходы второго счетчика соединены с информационными входами первого и второго регистров, выходы второго регистра соединен,: с информационными входами второй группы коммутатора.

72 (73-75}

86(87-89)

fpi/г.з

lOfy

5В о-

U2

О-

Wt

2

IMBi

/

и

о-

git

о-

J05

(

9Ц.

фиг. 5

130

i76

Редактор Л.Пчолинская

Составитель А.Чеканов Техред М.Дидык

Заказ 4869/45

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

О

фие.Ъ

Корректор Т.Палий

Подписное

| Вычислительный узел цифровой моделисетки для решения дифференциальных уравнений в частных производных | 1975 |

|

SU546891A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-29—Подача