1

Изобретение относится к средствам вычислительной техники и предназначе но для построения устройств, ориентированных на решение задач математи ческрй физики, описываемых дифференциальными уравнениями в частных производных.

Известен вычислительный узел цифровой сетки, содержащий процессор, выполняющий последовательно, разряд за разрядом, арифметические и логические операции и два блока памяти, емкостью по 2048 единиц каждый flj .

Недостатком этого устройства явля ется большое количество оборудования поскольку каждый вычислительный узел представляет за собой универсальную вычислительную машину, программно настраиваемую на выполнение требуемой последовательности действий, и низкое быстродействие последовательного способа обработки информации.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому устройству является вычислительный узел цифровой сетки содержащий многовходовый сумматор, регистр сдвига, элемент И, группу элементов И. Входы сумматора соединены со входами узла, выход сумматоpa соединен с последовательным входом регистра сдвига. Последовательный выход сдвигового регистра соединен с первым входом-элемента И, параллельные входы регистра соединены с первыми входами группы элементов и; Выход элемента И соединен с выходом узла, выходы группы элементов И соединены с параллельными выходами

10 узла. Управляющие входы регистра и элементов И соединены с управляющей шиной- 2 .

Недостатком устройства является узость класса решаемых задач. Решеi5ние дифференциальных уравнений с переменными коэффициентами возможно только при помощи универсальной вычислительной машины по методу невязок,что значительно увеличивает

20 общее время решения задачи, так как этотметод требует большого количества итераций,.а все операции в ЦВМ выполняются последовательно.

Цель изобретения - расширение

25 класса решаемых задач.

Поставленная цель достигается тем, что в вычислительный узел цифровой сетки, содержащий многовходовый сумматор, сдвиговый регистр и

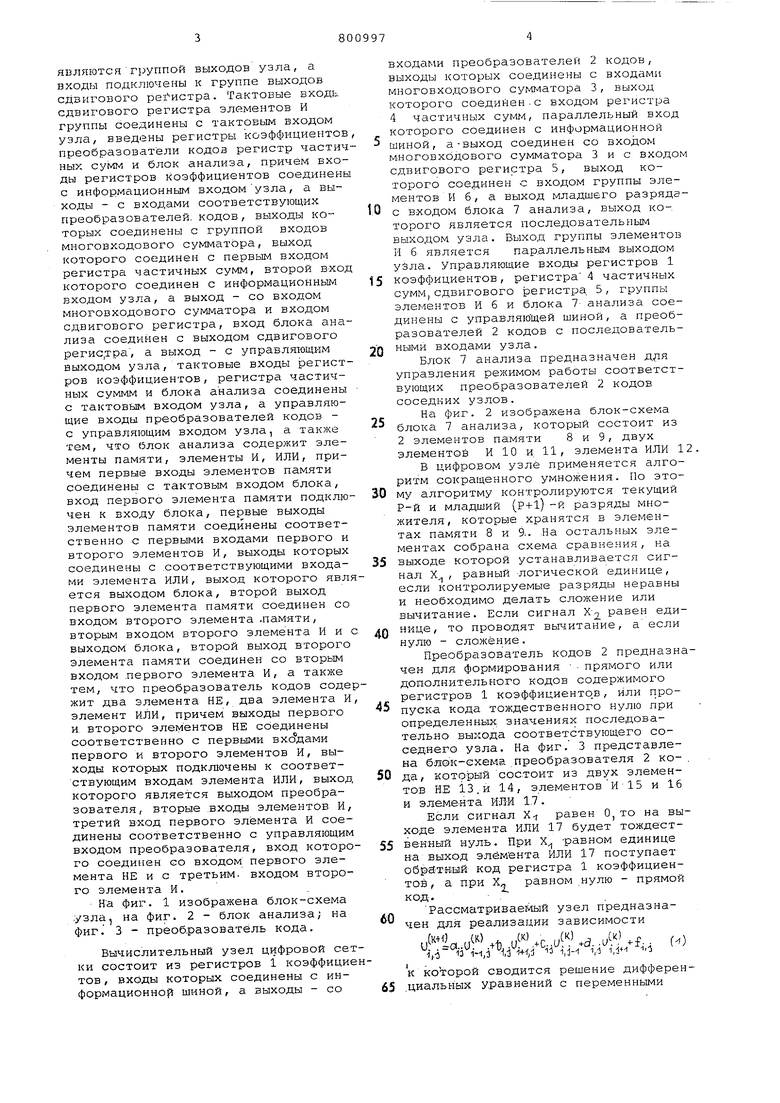

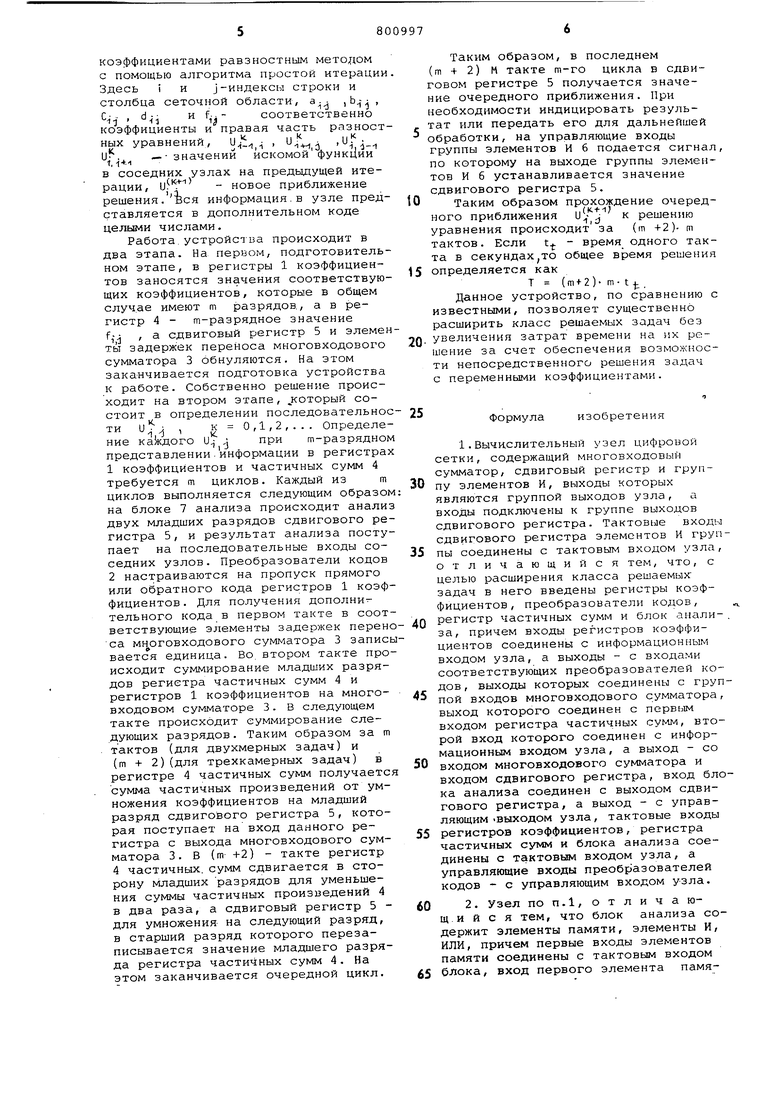

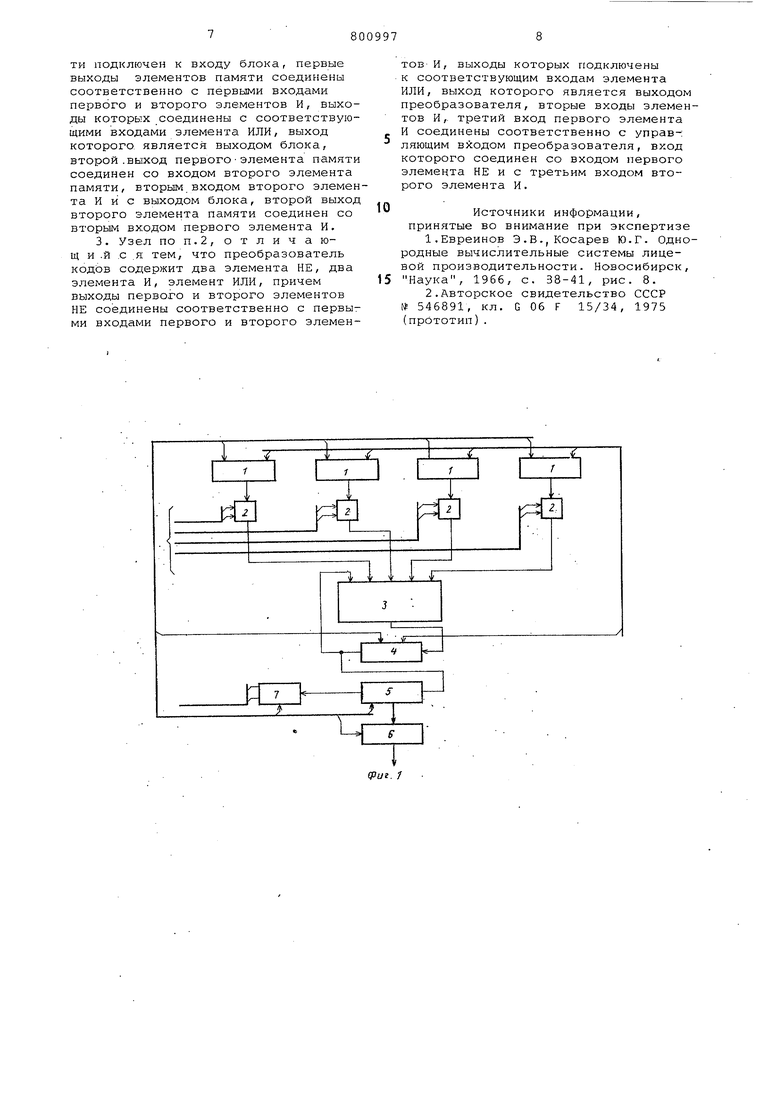

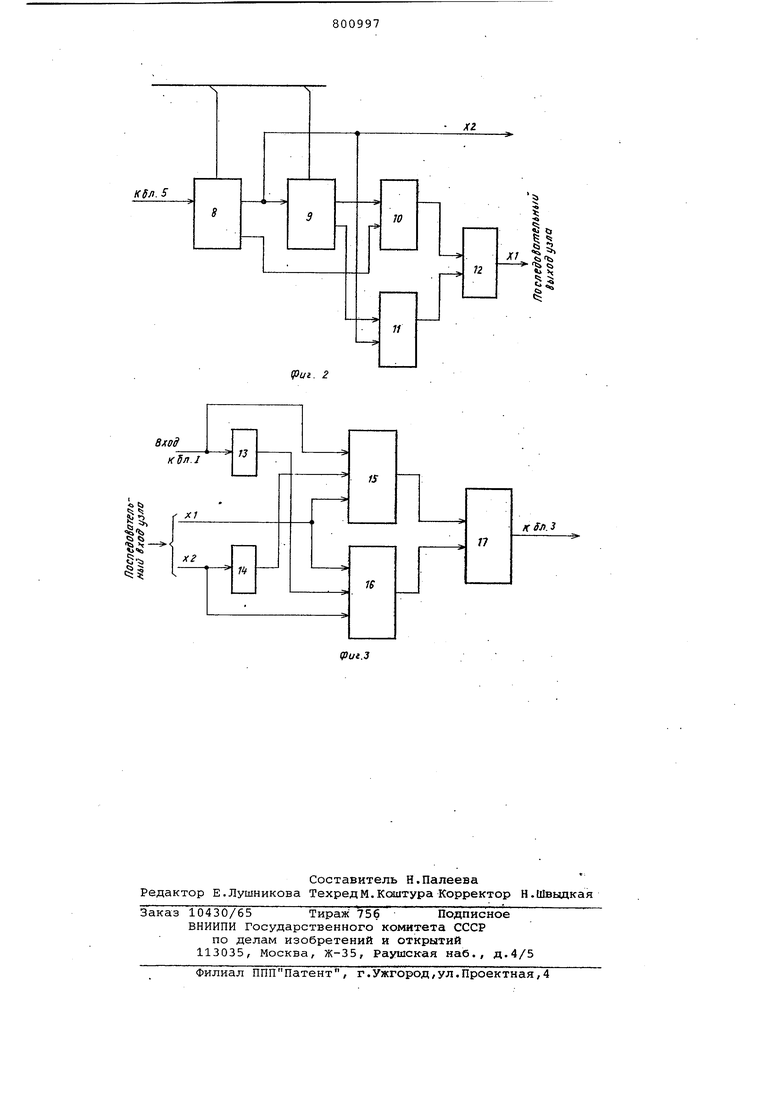

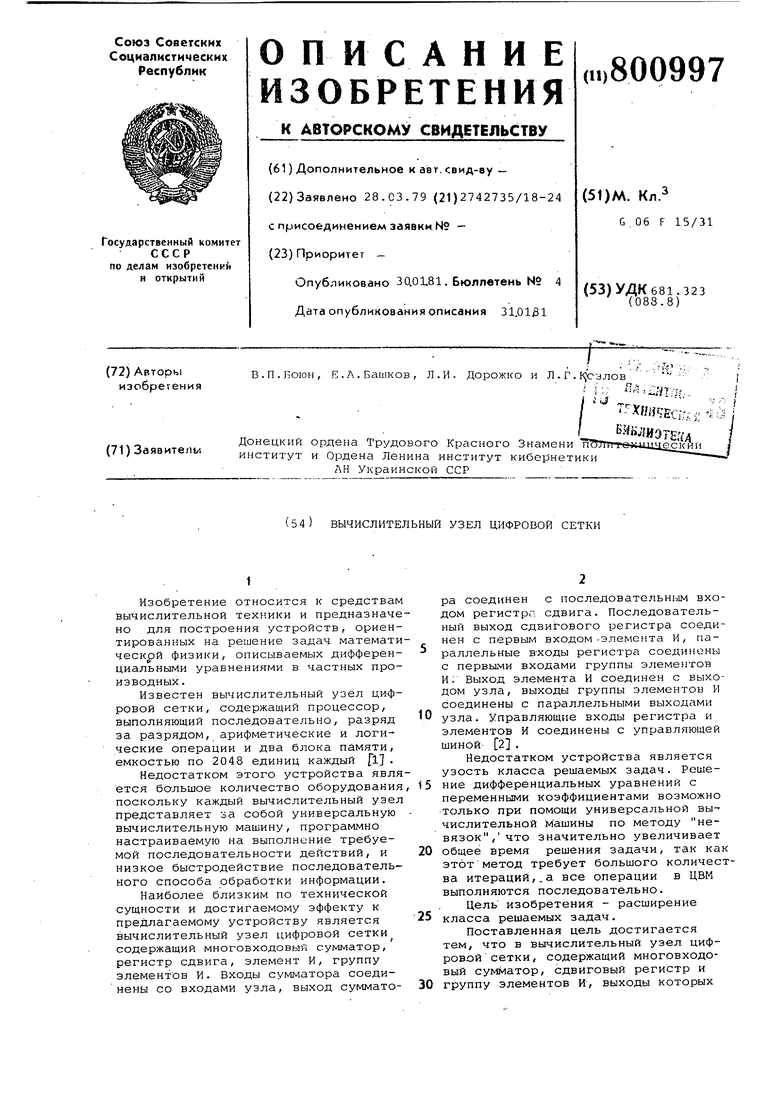

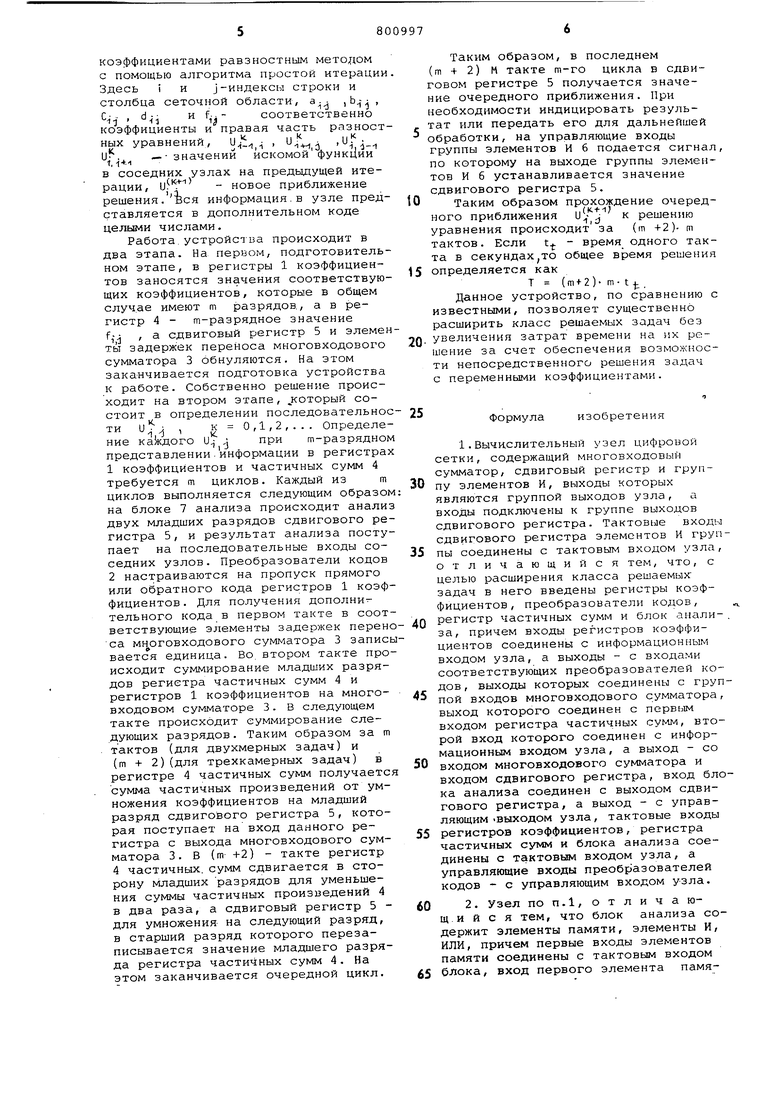

30 группу элементов И, выходы которых являются группой выходов узла, а входы подключены к группе выходов сдвигового регистра. Тактовые входь сдвигового регистра элементов И группы соединены с тактовым входом узла, введены регистры коэффициенто преобразователи кодов регистр части ных сумм и блок анализа, причем вхо ды регистров коэффициентов соединен с информационньзм входомузла, а выходы - с входами соответствующих преобразователей, кодов, выходы которых соединены с группой входов многовходового сумматора, выход которого соединен с первым входом регистра частичных сумм, второй вхо которого соединен с информационным входом узла, а выход - со входом многовходового сумматора и входом сдвигового регистра, вход блока ана лиза соединен с выходом сдвигового регис тра, а выход - с управляющим выходом узла, тактовые входы эегист ров коэффициентов, регистра частичных суммм и блока анализа соединены с TaicTOBbiM входом узла, а управляющие входы преобразователей кодов с управляющим входом узла, а также тем, что блок анализа содержит элементы памяти, элементы И, ИЛИ, причем первые входы элементов памяти соединены с тактовь м входом блока, вход первого элемента памяти подклю чен к входу блока, первые выходы элементов памяти соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены с .соответствующими входами элемента ИЛИ, выход которого явл ется выходом блока, второй выход первого элемента памяти соединен со входом второго элемента .памяти, вторым входом второго элемента И и выходом блока, второй выход второго элемента памяти соединен со вторым входом .первого элемента И, а также тем, что преобразователь кодов соде жит два элемента НЕ, два элемента И элемент ИЛИ, причем выходы первого и второго элементов НЕ соединены соответственно с первыми вхсУдами первого и второго элементов И, выходы которых подключены к соответствующим входам элемента ИЛИ, выход которого является выходом преобразователя,, вторые .входы элементов И, третий в-ход первого элемента И соединены соответственно с управляющим входом преобразователя, вход которо го соединен со входом первого элемента НЕ и с третьим, входом второго элемента И. На фиг. 1 изображена блок-схема .узла, на фиг . 2 - блок анализа; на фиг. 3 - преоб.разоватёль кода. Вычислительный узел цифровой сет ки состоит из регистров 1 коэффицие тов , входы которых соединены с информационнор шиной, а выходы - со входами преобразователей 2 кодов, выходы которых соединены с входами многовходового cyMiviaTopa 3, выход которого соединен.с входом регистра 4 частичных cyMj/i, параллельный вход которого соединен с информационной шиной, а-выход соединен со входом многовходового сумматора 3 и с входом сдвигового регистра 5, выход которого соединен с входом группы элементов И б, а выход младшего разрядас входом блока 7 анализа, выход которого является последовательным выходом узла. Выход группы элементов 1-1 6 является параллельным выходом узла. Управляющие входы регистров 1 коэффициентов, регистра 4 частичных cyMMj сдвигового регистра. 5, группы элементов И б и блока 7 анализа соединены с управляющей шиной, а преобразователей 2 кодов с последовательными входами узла. Блок 7 анализа предназначен управления режимом работы соответствующих преобразователей 2 кодов соседних узлов. На фиг. 2 изображена блок-схема блока 7 анализа, который состоит из 2 элементов памяти 8 и 9, двух элементов И 10 и 11, элемента ИЛИ 12. В цифровом узле применяется алгоритм сокращенного умножения. По этому алгоритму контролируются текущий Р-й и младший (P+I) -и разряды множителя, которые хранятся в элементах памяти 8 и 9.. На остальных элементах собрана схема сравнения, на выходе которой устанавливается сигнал Х, равный логической единице, если контролируемые разряды неравны и необходимо делать сложение или вычитание. Если сигнал Х- равен единице, то проводят вычитание, а если нулю - сложение. Преобразователь кодов 2 предназначен для формирования прямого или дополнительного кодов содержимого регистров 1 коэффициентов, или пропуска кода тождественного нулю при определенных значениях последовательно выхода соответствующего соседнего узла. На фиг. 3 представлена блок-схема преобразователя 2 ко-. да, который состоит из двух элементов ЕЕ 13.и 14, элементови 15 и 16 и элемента ИЛИ 1.7. Если сигнал K-i равен О, то на выходе элемента ИЛИ 17 будет тождественный нуль. При Х -равном единице на выход элемента ИЛИ 17 поступает обратной код регистра 1 коэффициентов , а при Х- равном нулю - прямой код. Рассматриваемый узел предназначен для реализации зависимости .u.й..,.....f., -if-j З 1-1,0 1р1 1+, 1,3-1 1, 1. к которой сводится решение дифферен.диальных уравнений с переменными

коэффициентами равзностным методом с помощью алгоритма простой итерации Здесь i и j-индексы строки и столбца сеточной области, а, , i-i (i i} соответственно коэффициенты и правая часть разностнь1Х уравнений, . , и| -Ki--, и . --значении искомой функции в соседних узлах на предьщущей итерации, - новое приближение pemefiHH .вся информация, в узле представляется в дополнительном коде целыми числами.

Работа,устройС1ва происходит в два этапа. На первом, подготовительном этапе, в регистры 1 коэффициентов заносятся значения соответствующих коэффициентов, которые в общем случае имеют m разрядов,, а в регистр 4 - т-разрядное значение f,- , а сдвиговый регистр 5 и элементы задержек переноса многовходового сумматора 3 обнуляются. На этом заканчивается подготовка устройства к работе. Собственно решение происходит на втором этапе, .который состоит в определении последовательности и , к 0,1,2,... Определение кakдoгo и ,j при т-разрядном представлении .информации в регистрах

1коэффициентов и частичных сумм 4 требуется m циклов. Каждый из m циклов выполняется следующим образом на блоке 7 анализа происходит анализ двух младших разрядов сдвигового регистра 5, и результат анализа поступает на последовательные входы соседних узлов. Преобразователи кодов

2настраиваются на пропуск прямого или обратного кода регистров 1 коэффициентов . Для получения дополнительного кода в первом такте в соответствующие элементы задержек переноса мн оговходового сумматора 3 записывается единица. Во. втором такте происходит суммирование младших разрядов регистра частичных сумм 4 и регистров 1 коэффициентов на многовходовом сумматоре 3. В следующем такте происходит суммирование следующих разрядов. Таким образом за m тактов (для двухмерных задач) и

(т + 2)(для трехкамерных задач) в регистре 4 частичных сумм получается сумма частичных произведений от умножения коэффициентов на младший разряд сдвигового регистра 5, которая поступает на вход данного регистра с выхода многовходового сумматора 3. В (т +2) - такте регистр 4 частичных, сумм сдвигается в сторону младших разрядов для уменьшения суммы частичных произведений 4 в два раза, а сдвиговый регистр 5 для умножения на следующий разряд, в старший разряд которого перезаписывается значение младшего разряда регистра частичных сумм 4. На этом заканчивается очередной цикл.

Таким образом, в последнем (т 4 2) М такте т-го цикла в сдвиговом регистре 5 получается значение очередного приближения. При необходимости индицировать результат или передать его для дальнейшей обработки, на управляющие входы группы элементов И 6 подается сигнал, по которому на выходе группы элементов И б устанавливается значение сдвигового регистра 5.

0

Таким образом прохождение очередного приближения u5, к решению уравнения происходит за (т +2)- m тактов. Если t.j. - время одного такта в секундах,то общее время решения

5 определяется как

Т (). т- t .

Данное устройство, по сравнению с известными, позволяет существенно расширить класс решаемых задач без увеличения затрат времени на их ре0шение за счет обеспечения возможности непосредственного решения задач с переменнь№1и коэффициентами.

25

Формула

изобретения

1.Вычислительный узел цифровой сетки, содержащий многовходовый сумматор, сдвиговый регистр и груп0пу элементов И, выходы которых являются группой выходов узла, а входы подключены к группе выходов сдвигового регистра. Тактовые вход.-1Ы сдвигового регистра элементов И груп5пы соединены с тактовым входом узла, отличающийся тем, что, с целью расширения класса решаемых задач в него введены регистры коэффициентов, преобразователи кодов, регистр частичных сумм и блок знали- .

0 за, причем входы регистров коэффициентов соединены с информационным входом узла, а выходы - с входами соответствующих преобразователей кодов, выходы которых соединены с груп5пой входов многовходового сумматора, выход которого соединен с первым входом регистра частичных сумм, второй вход которого соединен с информационным входом узла, а выход - со

0 входом многовходового сумматора и входом сдвигового регистра, вход блока анализа соединен с выходом сдвигового регистра, а выход - с управляющим -выходом узла, тактовые входы

5 регистров коэффициентов, регистра частичных сумм и блока анализа соединены с тактовым входом узла, а управляющие входы преобразователей кодов - с управляющим входом узла.

2. Узел по П.1, отличаю0щ и и с я тем, что блок анализа содержит элементы памяти, элементы И, ИЛИ, причем первые входы элементов памяти соединены с тактовым входом блока, вход первого элемента памя5

ти подключен к входу блока, первые выходы элементов памяти соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого, является выходом блока, второй .выход первогоэлемента памяти соединен со входом второго элемента памяти, вторым входом второго элемента И и с выходом блока, второй выход второго элемента памяти соединен со вторым входом первого элемента И. 3. Узел по п.2, отличающ и .и .с .я тем, что преобразователь кодов содержит два элемента НЕ, два элемента И, элемент ИЛИ, причем выходы первого и второго элементов НЕ соединены соответственно с первыми входами первого и второго элементов и, выходы которых подключены к соответствующим входам элемента ИЛИ, выход которого является выходом преобразователя, вторые входы элементов И,, третий вход первого элемента И соединены соответственно с управ-: ляющим входом преобразователя, вход которого соединен со входом первого элемента НЕ и с третьим входом второго элемента И.

Источники информации, принятые во внимание при экспертизе

1.Евреинов Э.В., Косарев ю.Г. Однородные вычислительные системы лицевой производительности. Новосибирск, Наука, 1966, с. 38-41, рис. 8.

2.Авторское свидетельство СССР № 546891, кл. G 06 F 15/34, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Вычислительный узел цифровой моделисетки для решения дифференциальных уравнений в частных производных | 1975 |

|

SU608165A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1981 |

|

SU976448A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Вычислительный узел цифровой сеточ-НОй МОдЕли для РЕшЕНия диффЕРЕНциАль-НыХ уРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU840920A1 |

Вход

Авторы

Даты

1981-01-30—Публикация

1979-03-28—Подача