П34932

tereqirafi деишфратор к второму входурым и третьим выходами блока соответшифратора, выходы которого явл5гются вто-ственио.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации от датчиков | 1980 |

|

SU981981A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Многоканальный преобразователь угла поворота вала в код | 1975 |

|

SU537371A1 |

| Многоканальный преобразователь угла поворота вала в код | 1983 |

|

SU1144190A1 |

| Устройство для сопряжения абонентов с ЦВМ | 1985 |

|

SU1278863A1 |

| Устройство для контроля состояния объекта | 1983 |

|

SU1119055A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

1. УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ ОТ ДАТЧИКОВ, содержащее а|5ифметический блок, преобразователь уголкод, группу преобразователей угол-код, первый коммутатор, первый дешифратор, первый счетчик, первый и второй блоки памяти, информациоиные входы преобразователей уголкод группы являются И11формационными входами устройства, управляющие входы преобразователей угол-код группы и преобразователя угол-код соединены с первым выходом блока управления, а выходы - с информациоиными входами первого коммутатора, выход которого подключен к информационному входу арифметического блока, управляющий вход которого соединен со вторым выходом блока управления, информационный вход-выход - с информационным входом-выходом нервсиго блока памяти, управляющий вход которого подключен к третьему выходу блока увравлею{я, информационный вход-выход является информационным входом-выходом устройства, выход второго блока памяти подключен к входу блока управления, четвертый выход которого соедииен со счетным входом первого счетчика, выходы которого подключены к входам первого дегтшфратора, пятый выход блока управления является выходом синусоидального напряжения устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит вторые счетчик, дешифратор и коммутатор, блок элементов И-НЕ и третий дещифратор, щестой выход блока управления подключен к счетному входу второго счетчика, выход которюго подключен ко входу второго дещифратора и к первому входу блока элементов И-НЕ, выход второго дешифратора соединен с управляющим входом второго коммутатора, информационные входы которого являются инфopмaциoн ыми входами устройства, а вьгход подключен к информационному входу преобразователя угол-код, выходы первого дешифратора подключены к управляющим входам первого коммутатора и к второму и (Л третьему входам блока элементов И-НЕ со:ответственно, четвертый и пятый входы которого подключены соответственно к выходу первого счетчика и седьмому выходу блоЧР ка управления, а выход - к адресному входу первого блока памяти и к входу третьего дешифратора, выходы которого . . соединены с адресными входами второго 00 4 СО блока памяти. 2. Устройство поп. I,oтличaюсо о щ е е с я тем, что блок управления содержит третий счетчик, четвертый дешифратор, шифратор, узел приоритета и формирователь синусоидального напряжения, BbtxojD которого является пятым выходом блока, первый вход шифратора и вход узла приоритета являются входом блока, одни выходы узла приоритета соединены с входами формирователя синусоидального, напряжения и третьего счетчика, другие выходы являются первым, четвертым, шестым и седьмым выходами блока соответственно, выход третьего счетчика подключен через

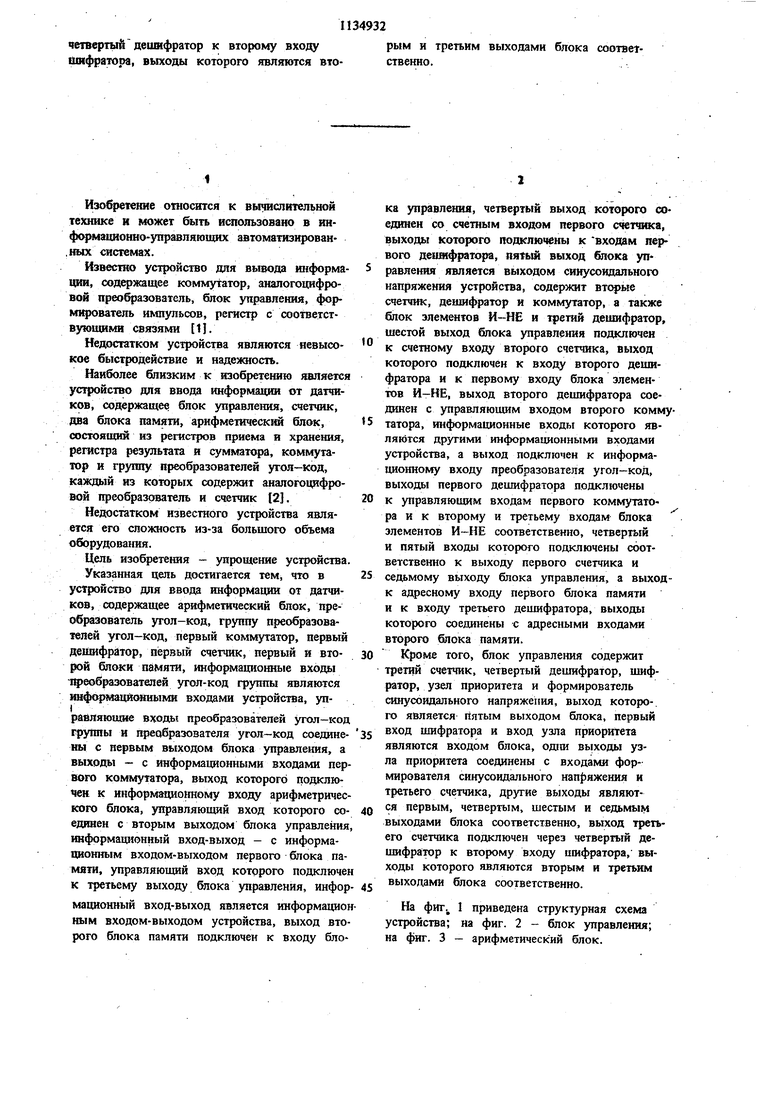

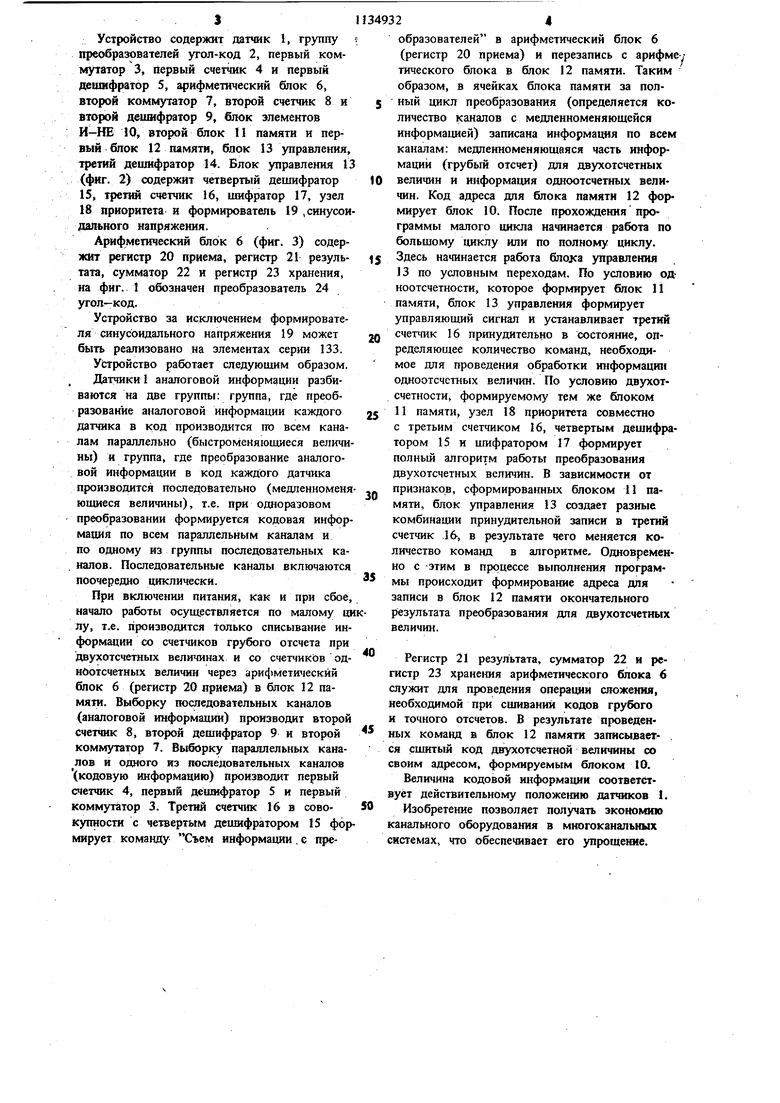

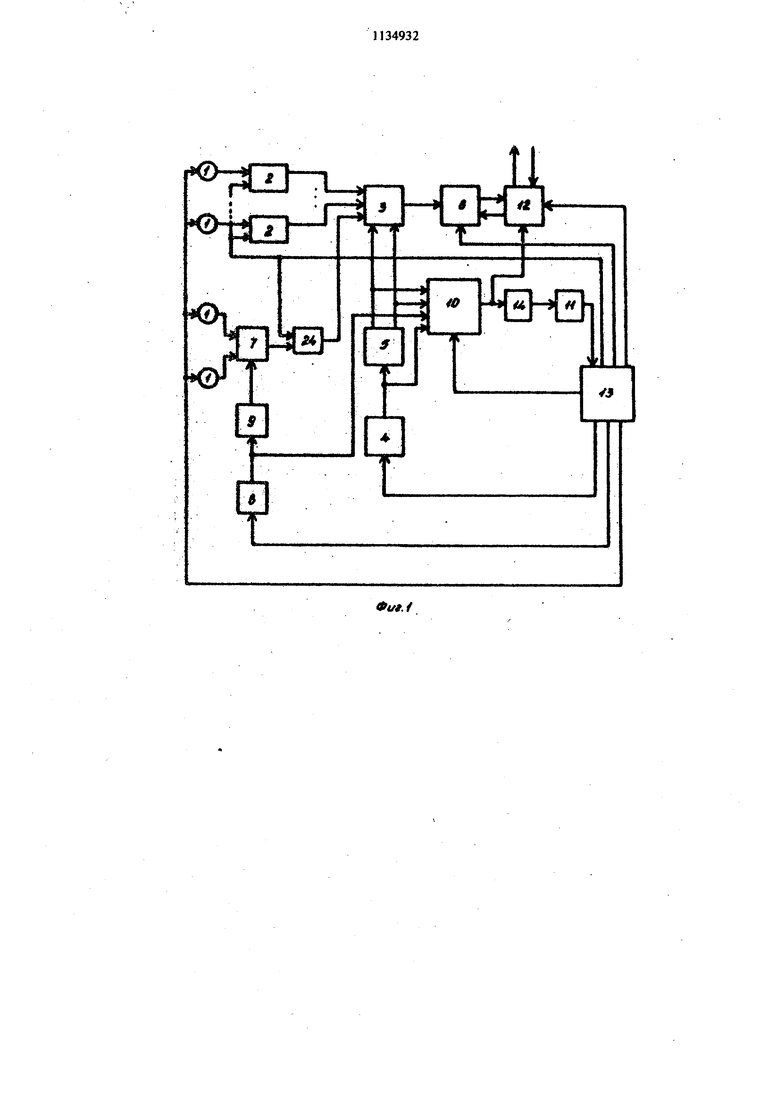

Изобретение относится к вычислительной технике и может быть использовано в иифсфмационно-управляюицис автоматизирован,ных системах. Известно устройство для вывода информаЩ и, содержащее коммутатор, аналогоцифровой преобразователь, блок управления, форМ1фователь импульсов, регистр с соответствзпощими связями 1. Недостатком устройства являются невысокое быстродействие и надежность. Наиболее близким к изобретению является устройство для ввода информации от датчиков, содержащее блок управления, счетчик, два блока памяти, арифметическ блок, состоящий из регастров приема и хранения, регистра результата я сумматора, коммутатор и группу преобразователей угол-код, каждый из которых содержит аналогоцяфровой преобразователь и счетчик 12. Недостатком известного устройства является его сложность из-за большого объема оборудования. Цель изобретения - упрощение устройства. Указанная цель достигается тем, что в устройство для ввода информащш от датчиков, содержащее арифметический блок, преобразователь угол-код, rpjoiny преобразователей угол-код, первый коммутатор, первый дешифратор, первый счетчик, первый и второй блоки памяти, информационные 1феобразователей угол-код группы являются информацйо {иыми входами устройства, управляющие входы преобразователей угол-код группы и преобразователя угол-код соещшены с первым выходом блока управления, а выходы - с информационными входами пер вого коммутатора, выход которого подключен к информационному входу арифметричес кого блока, управляюиий вход которого соедшнен с вторым выходом блока управления информащ{онный вход-выход - с информационным входом-выходом первого блока памяти, управляющий вход которого подключе к третьему выходу блока упргшления, инфор мационный вход-выход является информацио ным входом-выходом устройства, выход вто рого блока памяти по1цслючен к входу блока управления, четвертый выход которого соединен со счетным входом первого счетчика, выходы которого подаслю ны к входам первого дешифратора, пятый выход блока управления является выходом синусоидального напряжения устройства, содержит вторые счетчик, дешифратор и коммутатор, а также блок злементов И-НЕ и трегай дешифратор, щестой выход блока управления подалючен к счетному входу второго счетчика, выход которого подключен к входу второго дешифратора и к первому входу блока злементов И-НЕ, выход второго дешифратора соединен с управляющим входом второго коммутатора, информационные входы которого являются информационными входами устройства, а выход подключен к информационному входу преобразователя угол-коД, выхода первого дешифратора подключены к управляющим входам первого коммутатора и к второму и третьему входам блока элементов И-ИЕ соответственно, четвертый и пятый входы которого подключены соответственно к выходу первого счетчика и седьмому выходу блока управления, а выходк адресному входу первого блока памяти и к входу третьего дешифратора, выходы которого соединены с адресными входами второго блока памяти. Кроме того, блок управления содержит третий счетчик, четвертый дешифратор, шифратор, узел приоритета и формирователь синусоидального напряжения, выход которого является- пятым выходом блока, первый вход шифратора и вход узла приоритета являются входом блока, од1Щ вь1ходы узла приоритета соединены с входами формирователя синусоидального нзпряжскня и третьего счетчика, другие выходы являются первым, четвертым, шесть1м и седьмым выходами блока соответственно, выход третьего счетчика подключен через четвер1ый дешифратор к второму входу пшфратсфа, выходы которого являются вторым и третьим выходами блока соответственно. На фиг., 1 приведена структурная схема устройства; на фиг. 2 - блок управления; на фиг. 3 - арифметический блок. Устройство содержит датчик 1, группу преобразователей угол-код 2, первый коммутатор 3, первый счетчик 4 и первый дешифратор 5, арифметический блок 6, второй коммутатор 7, второй счетчик 8 и второй дешифратор 9, блок элементов И-НЕ Ю, второй блок 11 памяти и первый блок 12 памяти, блок 13 управления, третий дешифратор 14. Блок управления 13 (фиг. 2) содержит четвертый дешифратор 15, трепш счетчик 16, ишфратор 17, узел 18 приоритета и формирователь 19 , синусои дального напряжения. Арифметический блок 6 (фиг. 3) содержит регистр 20 приема, регистр 21 результата, сумматор 22 и регистр 23 хранения, на фиг. 1 обозначен преобразователь 24 угол-код. Устройство за исключением формирователя синусоидального напряжения 19 может быть реализовано на элементах серии 133. Устройство работает следующим образом. Датчики аналоговой информации разбиваются на дае группы: группа, где преобразование аналоговой информации каждого датчика в код производится по всем каналам параллельно (быстроменяющиеся величи ны) и группа, где преобразование аналоговой информации в код каждого датчика производится последовательно (медленноменя ющиеся величины), т.е. при одаоразовом преобразовании формируется кодовая инфор маш1я по всем параллельным каналам и по одному из группы последовательных каналов. Последовательные каналы включаются поочередно циклически. При включении питания, как и при сбое начало работы осуществляется по малому ц лу, т.е. производится только списывание информации со счетчиков грубого отсчета при двухотсчетных величинах и со счетчикОв однОотсчетных величин через ари(}1метическйй блок 6 (регистр 20 приема) в блок 12 памяти. Выборку последовательных каналов (аналоговой информашш) производит второй счетчик 8, второй дешифратор 9 и второй коммутатор 7. Выборку параллельных каналов и одного из последовательных каналов (кодовую информацию) производит первый счетчик 4, первый дешифратор 5 и первый коммутатор 3. Третий счетчик 16 в совокупности с четвертым дешифратором 15 фор мирует команду информации . с пре24образователей в арифметический блок 6 (регистр 20 приема) и перезапись с арифмеу тического блока в блок 12 памяти. Таким образом, в ячейках блока памяти за полный цикл преобразования (определяется количество каналов с медленноменяющейся информацией) записана информация по всем каналам: медленноменяюшаяся часть информации (грубый отсчет) для двухотсчетных величин и информация одноотсчетных величин. Код адреса для блока памяти 12 формирует блок 10. После прохождения программы малого цикла начинается работа по большому циклу или по полному циклу. Здесь начинается работа блока управления 13 по условным переходам. По условию одноотсчетности, которое формирует блок 11 памяти, блок 13 управления формирует управляющий сигнал и устанавливает третий счетчик 16 принудительно в состояние, определяющее количество команд, необходимое для проведения обработки информаци1{ одноотсчетных величин. По условию двухотсчетности, формируемок у тем же блоком И памяти, узел 18 приоритета совместно с третьим счетчиком 16, четвертым дешифратором 15 и шифратором 17 формирует полный алгоритм работы преобразования двухотсчетных величин. В зависимости от признаков, сформированных блоком 11 памяти, блок управления 13 создает разные комбинации принудительной записи в третий счетчик 16, в результате чего меняется количество команд в алгоритме, Одиовременио с -этим в процессе выполнения программы происходит формирование адреса для записи в блок 12 памяти окончательного результата преобразования для двухотсчетных величин. Регистр 21 результата, сумматор 22 н регистр 23 хранения арифметического блока 6 служит для проведения операции сложения, еобходимой при сшиваний кодов грубого и точного отсчетов. В результате проведеных команд в блок 12 памяти записывает- . ся сшитый код днухотсчетной величины со воим адресом, формируемым блоком 10. Величина кодовой информации соответстует действительному положению датчиков I. Изобретение позволяет получать экономию анального оборудования в многоканальных истемах, что обеспечивает его з рощенне.

нов лиг л

/к 4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для регистрации информации | 1978 |

|

SU824180A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для ввода информации от датчиков | 1980 |

|

SU981981A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-15—Публикация

1983-08-15—Подача