ца матрицы, выходы элементов ШШ первой группы .соединены с вторыми вхо дами соответствующих вычислительных :ячеек, nepBdjt строки матрицы, при этом кадцая вычислительная ячейка ч матрицы содержит два. элемента И и первый. одноразрядный i сзгиматор, причем первый вход вычислительной ячейки соединен.с первым входом первого элемента И и первым- выходом вычислительной ячейки, второй- вход первого .элемента И соединен с вторым входом и вторым выходом вычислительной янейки, выход первого элемента И . соединен с первым входом первого одноразрядного сумматора, второй и третий входы которого соединены.соответственно с третьим и -четвертым входами вычислительной ячейки, выход переноса первого одноразрядного сумматора подключен к первому входу второго элемента И, второй вход которого подключен к соответствующему входу, управления матрицы вычислительных ячеек, а выход - к четвертому выходу вычислительной-ячейки, выход суммы одноразрядного сумматора подключен к третьему выходу вычнсли- тельной .ячейки, управляющие входы первого и второго -входных коммутаторов и матричных коммутаторов подключены соответственно- к первому, второму и. третьему управляющим входам подачи, информации устройства, отличающееся тем, что с целью расширения,функциональных возможностей за счет вычисления полинома-ошибок, устройство содержитттретий входной регистр. третий входной- коммутатор, регистр результата, три группы элементов И, элемент ИЛИ, а вычислительная ячейка дополнительно содержит третий элемент И и второй одноразрядный сумматор, причем пятый вход вычислительной ячейки соединен |с ее пятым выходом, выход .суммы первого одноразрядного-сумматора и пятый вход.вычислительной ячейки соединены с первым и вторым входами второ го одноразрядного сумматора,выход сумм которого подключен к первому входу третьего, элемента И, второй вход которого подключен к шестому входу вьг числительной ячейки, а выход - .к шестому выходу вычислительной ячейки, третьи входы вычислительных ячеек первой строки матрицы, подключены ксоответствующим выходам третьего . входного коммутатора, информационные входы первой группы которого, кроме входа последнего разряда, соединены с соответствующими выходами второй группы второго входного коммутатора, информационные входы второй труппы третьего входного коммутатора, кроме входа первого разряда, соединены с выходами регистра результата, первый информационный вход последнего разряда третьего входного коммутатора подключен к выходу (m + l)-го разряда первого входного регистра, второй информациоиный вход первого разряда

третьего входного коммутатора соединен с шиной значения О, входы регистра результата подключены к выходам .элементов И первой группы, первые входы которых подключены к третьим выходам вычислительных ячеек последней строки матрицы, выходы третьего входного-регистра подключены к пятым входам вычислительных ячеек первой строки матрицы, пятые выходы вычислительных ячеек матрицы подключены к пятым входам следующих ячеек тех же столбцов, третьи входы вычислительных ячеек последнего столбца матрицы соединены о выходами элементов И второй ГРУППЫ) первые входы котсфых соединены с выходами младших разрядов первого входного регистра, шестые выходы вычислительных ячеек первого столбца.матрицы подключены к. первым входам элементов И третьей группы, выходы которых подключены к счетным входам старпюх разрядов первого входного -регистра, шестые входы вычислительных ячеек последнего, столбца матрицы,Vподключены к пмне значения- I, шесв-ые выходы вычие- лителльных ячеек всех столбцов матрицы, .кроме первого, соединены-с шестыми входами- предыдущих вычислитель-. ных ячеек тех же строк матрицы, выходы регистра результата подключены к Входам элемента ИЛИ, выход которого подключен-К выходу признака ошибки устройства, вторые входы элемен тов И первой., второй.и третьей групп подключены соответственно к первому, второ 4у;И третьему управляющим вхо- дам выбора рещма устройства, управлякищй вход третьего входного комму- |татора подключен к четвертому управ- ляющему входу подачи информации. Изобретение относится к автоматике и вычислительной технике и может быть использовано в быстродействующих процессорах и кодирующих-декодирующих устройствах, Известно матричное вычислительное устройство для выполнения операций деления, состоящее из матрицы ячеек каждая из которых содержит одноразрядный сумматор- вычи слит ель и имеет четыре входа: делимого, делителя, переноса- заема из однораарядного сум матора-вычитателя последующей ячейки строки матрицы в одноразрядный сумматор-вычигатель предыдущей- ячейки этой же строки матрицы, вход управления - и четыре выхода: частичного остатка, переноса-заема из одноразрядного- сумматора-вычитателя данной ячейки строки матрицы в од- .норазрядный сумматор-вычитатель пре дущей ячейки этой же строки матрицы делителя, выход управления ij . Основным недостатком этого устрой ства являются ограниченные функцио- нальные возможности, т.е. оно позволяет выполнить-только одну операцию деления двоичных чисел. Известно матричное вычислительное устройство для выполнения операции умножения, содержащее входные регист ры, матрицу вычислительных ячеек и блок сумматоров Выходы первого входного регистра соединены с соответствующими первыми входами- вычис- лительных ячеек первого столбца матрицы, а первые выходы вычислительных ячеек строк.матрицы соединены последовательно с первыми входами последующих вычислительных ячеек тех же строк матрицы, выходы второго входного регистра соединены, с соответствующими вторыми входами вычислительных ячеек строки матрицы, вторые выходы вычислительных ячеек -матрицы соединены последовательно с вторыми входами ячеек последующих строк тех же столбцов матрицы, третьи выходы вычислительных ячеек соединены с третьими входами вычислительных ячеек предыдущих столбцов последующих строк матрицы,-третьи выходы ячеек последней строки матрицы являются выхода устройства, че ;вертые выходы ячеек соединены с четвертыкм входами янеек тех же строк матрицы, четвертые выходы ячеек лервого столбца соединены с входами блока сумматоров-, выходы |сумм.которого являются выходами-устройства. Каждая ячейка устгайства содержит элемент И и одноразрядный сумматор 2J . Недостаток данного устройства т . ограниченные функциональные возможности (устройство выполняет только операцию умножения двоичных чисел), Наиболее близкимк предлагаемому является матричное вычислительное устройство, выполняющее операцию деления полиномов, необходимую для кодирования и декодирования, информации, содержащее первый и второй входные регистры, два входных коммутатора, матрицу вычислительных ячеек блок сумматоров, элементы ИЛИ, матричные коммутаторы, причем первые выходы вычислительных ячеек каждой строки матрицы соединены последовательно с первыми входами последующих вычислительных ячеек этой же строки, вторые выходы вычислительных ячеек строк матрицы соединены последовательно с вторыми входами вычислительных ячеек,последующих строк тех же столбцов, третьи выходы вычислительных ячеек соединены с третьими входами вычислительных ячеек предыдущих столбцов очередных строк, а третьи выходы вычислительных ячеею последней строки матрицы являются выходами устройства, четвертые вьЬсоды вычислительных ячеек строк, матрицы соединены-последовательно -С четвертыми входами пре- дьщущих вычислительных ячеек тех же строк матрицы, а четвертые выходы вычислительных ячеек первого столбца матрицы .соединены- с соответствующими одними входами сумматоров блока сумматоров, причем выходы переноса каждого сумматора-блока сумматоров соединены с входами переноса предыдущего сумматора указанного блока, а выходы сумм сумматоров блока су маторов-являются выходами устройств ва, выходы первого входного -регистра соединены с информационными входаьш первого входного коммутатора, вторые выходы которого соединены с соответствующими вторыми входа ш элементов ИЛИ-первой группы, выходы-второго входного регистра соединены с инфор- мационным входаьш второго входного коммутатора, первые выходы которого соединены, с соответствующими первыми входами элементов ИЛИ первой группы, а вторые шлходы.- с. соответствующими вторыми входами элементов ИЛИ второй

группы, первые входы элементов ИЛИ второй группы, кроме первого элемента соединены с соответствующими вторыми выходами матричных коммутаторов, информационные входы которых соедннены с соответствующими третьими выходами вычислительных ячеек первого столбца матрицы, а первые выходы матричных коммутаторов соединены с соответствующими другими входами сумматоров блока сумматоров, выходы элементов ЩШ. второй группы соединены .с соответствующими первыми входами вычислительных ячеек первого столбца матрицы, выходы элементов ИЛИ первой группы соединены-с соответствующими вторыми входами вычислительных ячеек первой- строки матрицы-. Каждая вычислительная ячейка матрицы содержит элемент И, одноразрядный сумматор и ключ 3j I

Недостаток данного устройства ограниченные функциональные возможности, так как оно позволяет выполнять толькогоперацию деления,полиномов при кодировании и декодировании информации.

Целью изобретения является расширение функциональшлх возможностей устройства за счет выполнения операции вычисления полинома ошибки, необходимой для исправления искаженных символов при декодировании информации.

Поставленная, цель.достигается тем, что матричное вычислительное-устройство, содержащее первый и второй входные регистры, два входных коммутатора, матрицу вычислительных ячеек, бЛок сумматоров, элементы ИЛИ, матрич- ные коммутаторы,.причем первые выходы вычислительных ячеек.каждой строки матрицы соединены с первыми входами последуюпщх.вычислительных ячеек этой же строки матрицы, вторые выходы вы- числительных ячеек строк-матрицы соединены с вторьши входами последующих вычислительных .ячеек тех же столбцов матрицы, третьи выходы вычислительных ячеек матрицы соединены с третьими входами вычислительиых ячеек.предыду- щнх столбцов последующих строк матриm i, а третьи выходы вычислительных ячеек.последней строки матрицы являются выходами устройства четвертые выходы вычислительных-ячее к стро матрицы соединеныпоследовательно с. четвертыми входами предыдущих вычислительных ячеек тех же строк матрицы, а четвертые выходы вычислитель ных ячеек первого столбца матрицы соединены с первыми входами соответствующих сумматоров блока сумматоров выход переноса каждого сумматора блока сумматоров соединен с вторым входом предыдущего сумматора блока сумматоров,выходы суммы сумматоров блока сумматоров являются выходами устройства, выходы первого входного регистра соединеньг с информационными входами первого входного коммутатора выходы первой группы которого соеди|нены с первыми входами соответствую Щих элементов ИЛИ первой группы, выходы второго входного регистра соединены с информационныь«и входами второго входного коммутатора, выходы первой группы которого соединены

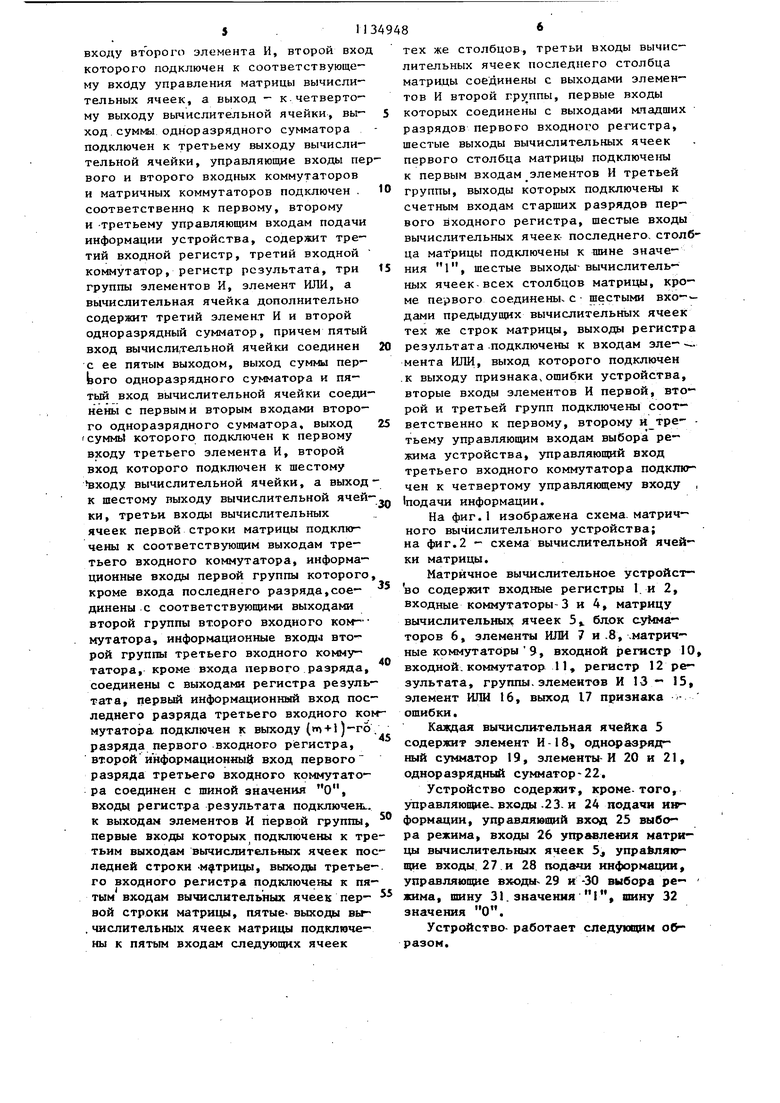

с вторыми, входами соответствукнцих элементов ИЛИ первой группы, выходы второй группы второго входного.коммутатора соединены с первыми входами соответствующих элементов ИЛИ второй ;группы, вторые входы элементов ИЛИ второй группы,, кроме первого, соединены с первыми выходами соответствующих матричных коммутаторов, информационные входы которых соединены с третьими выходами соответствующих вычислительных ячеек первого столбца матрицы, вторые выходы матричных коммутаторов соединены с третьими входами соответствующих сумматоров блока сумматоров, выходы элементов ИЛИ второй группы соединены с первыми входами, соответствующих вычислительных ячеек первого столбца матрицы, выходы элементов ИЛИ первой rpynrai соединены с- вторыми входами соответствующих вычислительных ячеек первой строки матрицы, при этом каждая вычислительная ячейка матрицы содержит два элемента И.и первый одноразрядный сумматор, причем первый вход, вычислительной ячейки соединен с первым входом первого элемента И и первым выходо 1 вычислительной ячейки, второй вход.первого элемента И соединен с вторым входом и вторым выходом вычислительной, ячейки, выход первого элемента И соединен с первым входом перBOQO одноразрядного сумматора:, второй и третий входы.которого соединены соответственно с третьим и четвертым входами вычислительной ячейки, выход переноса первого одноразрядного сумматора .подключен к первому 5 . 11 входу второго элемента И, второй вход которого подключен к соответствующему вхсЗду управления матрицы вычислительных ячеек, а выход - к.четвертому выходу вычислительной ячейки, выход . cyMNW одноразрядного сумматора подключен к третьему выходу вычислительной ячейки, управляющие входы пер вого и второго входных коммутаторов и матричных коммутаторов подключен . соответственно к первому, второму и -третьему управляющим входам подачи информации устройства, содержит третий входной регистр, третий входной коммутатор, регистр результата, три группы элементов И, элемент ИЛИ, а вычислительная ячейка дополнительно содержит третий элемент И и второй одноразрядный сумматор, причем пятый вход вычислительной ячейки соединен с ее пятым выходом, выход суммы пер- Ього одноразрядного сумматора и пятый вход вычислительной ячейки соединены с первым и вторым входами второго одноразрядного сумматора, выход суммь которого подключен к первому входу третьего элемента И, второй вход которого подключен к шестому входу вычислительной ячейки, а выход к шестому выходу вычислительной ячейки, третьи входы вычислительных ячеек первой строки матрицы подключены к соответствующим выходам третьего входного коммутатора, информационные входы первой группы которого кроме входа последнего разряда,соединены .с соответствующими выходами второй группы второго входного ком- мутатора, информационные входы второй группы третьего входного комму татора, кроме входа первого разряда, соединены с выходами регистра результата, первый информационный вход последнего разряда третьего входного KCJ мутатора подключен к выходу (|т) + 1)-го разряда первого входного регистра, второй информационны вход первого разряда третьего входного коммутатора соединен с шиной значения О, входы регистра результата подключеш.. к выходам элементов И первой группы, первые входы которых подключены к тре тьим выходам вычислительных ячеек пос ледней строки -матрицы, выходы третьего входного регистра подключешл к пятым входам вычислительных ячеек первой строки матрицы, пятые- выходы вы.числительных ячеек матрицы подклгачены к пятым входам следующих ячеек 8 тех же столбцов, третьи входы вычислительных ячеек последнего столбца матрицы соединены с выходами элементов И второй , первые входы которых соединены с выходами младших разрядов первого входного регистра, шестые выходы вычислительных ячеек первого столбца матрицы подключены к первым входам элементов И третьей группы, выходы которых подключены к счетным входам старших разрядов первого входного регистра, шестые входы вычислительных ячеек последнего, столбца матрицы подключены к шине значе- « 11I ния 1 , шестые выходы-вычислительных ячеек всех столбцов матрицы, кроме первого соединены с шестыми вхо-дами предыдущих вычислительных ячеек тех же строк матрицы, выходы регистра результата подключены к входам эле---. мента ИЛИ, выход которого подключен .к выходу признака,ошибки устройства, вторые входы элементов И первой, второй и третьей групп подключены соот ветственно к первому, второму тьему управляющим входам выбора режима устройства, управляющий вход третьего входного коммутатора подклкгчей к четвертому управляющему входу , подачи информации. На фиг.1 изображена схема, матричного вычислительного устройства; на фиг.2 - схема вычислительной ячейки матрицы. Матричное вычислительное устройст- во содержит входные регистры 1. и 2, входные коммутаторы-3 и 4, матрицу вычислительных ячеек 5 блок ауНма- торов 6, элементы ИЛИ 7 и .8, чматрич- ные коммутаторы 9, входной регистр 10, входной, коммутатор 11, регистр 12 результата, группы.элементов И 13 15, элемент ШШ 16, выход 17 признака ошибки. Каждая вычислительная ячейка 5 содержит элемент И-18, одноразрядный сумматор 19, элементы-И 20 и 21, одноразрядный сумматор-22, Устройство содержит, кроме, того, Управляюище. входы .23. и 24 подачи ин формации, управляющий вход 25 выбора режима, входы 26 управлення матрицы вычислительных ячеек 5j управляющие входы 2 7.и 28 подачи информации, управляющие входы- 29 и -30 выбора ре- има, шину 31. значения I, шииу 32 значения О. Устройство- работает следуюощм обазом. При кодировании в регистре 1 за- писаны коэффициенты, информационного полинома (х). в старших k разрядах регистра 2 записаны коэффициен ты порождающего полинома р(х), кроме старшего коэффициента. Коммутаторы 3 и 4 подключают к своим выходам выходы регистров 1 и 2 при подаче единичных сигналов на входы 23 и 28. Элементы И 13. открыты подачей единичного-сигнала на вход 25. И 14, 15 и 20 закрыты подачей нулевого сигнала на входы 29, 30 и 26, в результате, чего в сумматорах 19 ячеек 5 выполняется суммиров.ание по модулю два. Коммутатор 11подключает к вторым входам ячеек 5 .выходы коммутатора 3 подачей единичного сигнала на вход 24. Коммутато. ры,9подключают, третьи выходы ячеек 5 к дходам элементов ИЛИ 8 подачей единичного сигнала на вход 27. Goдержимое старшего разряда регистра ч.ерез 1 оммутаторы 3 и 11 и элемент ШШ 8 управляет элементами, И 18 ячеек 5 первой строки матрицы; третсьи. выходы ячеек 5 первого столбца через коммутаторы 9 и элементы ИЛИ 8 управляют элементами И 18 ,к 5 очередных строк матрицы; содер;р1Ное разрядов, регистра 1 с в.Т;О. по (гя + О и через коммутаторы 3 и 1 Г поступают на сумматоры 19 ,;ячеек -5, первой строки- матрицы; со держимое П-т-1 младших разрядов ;регистра. I через элементы , посlTyq;a.eTi,на сумматоры- 19 ячеек 5-последнего.. столбца матрицы.- В первой ,5 матрицы выполняется сумми- .ррБа;Ние по модулю два делимого g(.х}х и, де ителя р(х) в случае, если йоде яммое.старшего разряда делимого рав но 1, а если содержимое старшего разряду делимого равно О, то выпо няется су 14№ррвание делимого (x)vx с нулем,флучаем частичный о таток который при передаче-В следующую строку, матрицы ячеек 5 сдвигается ,,:Да один, разряд. В последующих ст,р9. ,мат. ячеек 5 после сдвиг прке ь1ду;дегр. астичного. остатка выпо ,ся, суммирование его либо с р ( ес,ш,,аначеийе старшего-разряда равн ii--,Vi-,i- j:- X м f Jc.;j- ,риро :С 1|;улем, если значение ст шето рйзряда равно О. В итоге на выходах ячеек 5 последней строки ма рОДы адЬлучаем. проверочный полином ) кодового полинома t (х) . 88 Декодирование циклического кода состоит из двух этапов: вычисление локатора ошибки 5 1,х) , вычисление полинома ошибки е(х) для исправления ошибки. При вычислении локатора ошибки (х. в регистре 1 записан принятый кодовый полином h (х); в старших k разрядах регистра 2 записаны t младших коэффициентов порождающего полинома р(х), в регистре 10 записано инверсное значение локатора ошибки для старшего разряда полиномаh (х). Коммутаторы 3 и 4 подключают к своим выходам выходы регистров 1 и 2 подачей, единичного сигнала на.входы 23 и 28. Элементы И 13 и 14 открыть: подачей единичного сигнала на входы 25 и 29. Элементы И 15 и 20 закрыты подачей нулевого сигнала на входы 26 и 30, в результате чего в сумматорах 19 ячеек 5 выполняется сум мирование по модулю два. Коммутатор 11 подключает, к вторым входам ячеек 5 выходы коммутатора 3 подачей единичного сигнала на вход-24,. Коммутаторы 9 подключают третьи выходы ячеек 5 к входам элементов ИЛИ 8 подачей единичного сигнала на вход 27. Содержимое старшего разряда регистра .1 через коммутаторы 3 и 11,и элемент ИЛИ 8 управляет элементами И IВ ячеек 5 первой строки.матрицы; третий выход каждой ячейки 5 первого столбца через коммутатор 9 и элемеит ИЛИ 8 управляет элементом И 18 ячейки 5очередной строки матрицы; содержимое старших разрядов регистра I через коммутаторы 3 и П поступает на сумма- торы 19 ячеек 5 первой строки,матри- цы, содержимое 1Г|-т-1 мпадцшх разрядов регистра 1 через элементы И 13 - (поступает на сум аторы 19 ячеек 5 последнего столбца матрицы Как и при «одировании, в каждой строке матрицы ячеек 5 формируется частичный остаток в результате суммирования по модулю два значения предыдущего частичного остатка с порождающим полиномом р х) в зависимости от. содержимого старшего разряда предыдущего частичного остатка. При передаче частичного остатка на входы ячеек 5 tuieдующей строки матрицы частичный остаток сдвигается влево .на-один разряд. В итоге, получаем локатор ошибки 5(х), который через открытые элементы И 14 записывается в регистр 12 .Элемент ИЛИ 16 проверяет содержимое регистра 12 на нуль. Если локатор ошибки 6(xj не равен иулю, т.е. принятый полином Ь (х) содержит ошибку, то на выходе 17 появляется сигнал, В этом случае выполняется второй этап .декодирования - вычисление полинома ошибки е (х) . При вычислении полинома ошибки elx элементы И 13, 14 и 20. закрыты подачей нулевого сигнала на входы 25 26 и 29. Элементы И 15 открыты подачей единичного сигнала на вход 30. Содержимое регистра 2 через коммутатор 4 и элементы ИЛИ 7 поступает на входы элементов И 18 ячеек 5 первой строки матрицы подачей единичного си нала на вход 28, Коммутатор 11 подключает- содержимое регистра 12 к вхо дам сумматоров 19 ячеек 5 первой строки матрицы подачей нулевого сигнала на вход 24, Содержимое регистра 12 поступает на входы сумматоров 19 ячеек 5. первой строки матрицы и суммируется с нулем. Результат на выходах сумматоров 19 суммируется по модулю два с содержимым регистра 10, т,е, осуществляется сравнение вычисленного локатора ошибки с инверсным значением локатора ошибки первой позиции.Результат сравнения с выходов сумматоров 22 анализируется элементами И 21 всех ячеек 5.. Если сравниваемые локаторы равны, т.е. на вьссодах. всех сумматоров 22 появляется 1, то на шестом выходе ячейки 5 первого столб ца матрицы вырабатывается сигнал 1 который через открытый элемент И.15 поступает на соотлетствукнций счетный вход регистра 1, благодаря чему исправляется ошибка.в принятом полиноме Ь (х. Если сраввияаеные локаторы не равны, то .вычисленный локатор с выходов сумматоров 19 ячеек 5 постзг пает с одновременным, сдвигом иа трет входы ячеек 5 очередной, строки натри цы, причем выход старшего разряда через коммутатор., 9 и элемент ИЛИ 8 управляет первыми-входаъв элементов И 18 ячеек 5, благодаря-чему предыдущий локатор ошибки су в4ируется по модулю два с р х) или. с .нулем. Далее вновь сравнивается полученное значение.локатора ошибки с содержимым регистра 10 и. если сравниваемь1е локаторы равны, то н.а шестом выходе ячейки 5 появляется значение 1И, которое через элемент И 15 исправляет ошибки; в полиноме h (xj , если срав ниваемые локаторы не равны то осу- ществляется. переход к. ячейкам 5 следующей строки матрицы,- и -так далее до последней строки матрицы, В результате получаем-..-исходный кодовый полином t (х). При выполнении умножения в регистрах 1 и 2 записаны множимое и множитель. Коммутаторы 3 и 4 подключают к своим выходам выходы регистров 1 и 2 подачей нулевого сигнала-на входы 23 и 28. Элементы И 13.- 15 закрыты .подачей нулевых сигналов на входы 25, 29 и 30. Элементы И 20 открыты подачей единичного сигнала на входы 26, благодаря чему в сумматоре 19 выполняется арифметическое сложение, &.1ХОДЫ регистра I через коммутатор 3 и элементы ИЛИ 7 управляют, входами элементов И 18, выходы регистра 2 через коммутатор 4.и элементы ИЛИ 8 управляют первыми входами.элементов И 18. Коммутаторы 9 подключают выходы сукг маторов. 19 ячеек -5 первога столбца матрицы к входам сумматоров 6 подагчей нулевого сигнала на вход 27. В каждой строке-ячеек 5 матрицы выполняется умножение множимого из регистра I на соответствующий разряд множителя и сложение с предыдущим частным произведением, сдвинутым влево. После выполнения умножения на выходах сзгмматоров 6- появляются старшие разряда произведения) at на- тре- тьих выходах ячеек 5 последней -стро- ки матрицы .- младшие разряды произведения . Данное устройство- по сравнению с прототипом выполняет-дополнительные функции: вычисление полинома опвс- бок, исправление,искаженных символов, что позволяет-расширить область прнменения устройства и сократить суммарные затраты, оборудования на реализацию всех функций устройства отдельными специалнзированшлми модулями (арифметический.умножитель, модуль вычисления-синдрома, модульвычисления полинома ошибок, модуль исправления искаженных символов), Введение дололнительных.функций в устройство, позволяет «е только об- нарулявать наличие ошибок, но и исправлять искаженные символы, увеличивая тем саьшм помехозащищенность системы что создает возможность адаптации к уровню помех в.канале связи, памяти, накопителях и т.п. в зависимости от области применения.

Ф 4 Д Ф

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1978 |

|

SU750485A1 |

| Матричное вычислительное устройство | 1979 |

|

SU809173A1 |

| Матричное вычислительное устройство | 1990 |

|

SU1833890A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

МАТРИЧНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый и второй входные регистры, два входных коммутатора, матрицу вычислительных ячеек, блок сумматоров, элементы ИЛИ, матричные коммут аторы, причем первые выходы вычислительных ячеек каждой строки матрицы соединены с первыми входами последующих вычислительных ячеек этой же строки матрицы, вторые выходы вычислительных ячеек строк матрицы соединены с вторыми входами последующих ячеек тех же столбцов матрицы, третьи выходы вычислительных ячеек, матрицы соединены с третьими входами вычислительных ячеек предыдуц1их столбцов последующих строк матрицы, а третьи выходы вычислительных ячеек последней строки матрицы являются выходами устройства, четвер- ibie выходы вычислительных ячеек строк матрицы соединены последовательно с четвертыми входами предьвдущих вычислительных ячеек тех же строк матрицы, а четвертые выходы вычислительных ячеек первого столбца матрищя соединены с первыми входами соответ- ствующиз{ сумматоров блока сумматоров, выход переноса каждого сумматора блока сумматоров соединен- с вторым входом предыдущего сумматора блока суымоторов, выходы суммы сумматоров блока сумматоров являются выходами устройства, выходы первого входного регистра соединены с информационными - входами первого входного коммутатора, g выходы первой группы которого соединены с первыми входами соответствую- taHx элементов ИЛИ первой группы, выходы второго входного регистра соединены с информационными входами второго входного коммутатора, выходы первой группы которого соединены с вторыми входами соответствующих элементов ИЛИ первой группы, выходы второй группы второго входного коммутатора соединены с первыми входа- ми соответствующих элементов ИЛИ втоСАЭ 4 рой )1, вторые входы элементов ИЛИ второй группы, кроме первого, ;о эо соединены с пе)выми выходами соответствующих матричшлх коммутаторов, информационные входы которых соединены с третьими выходами соответствующих вычислительных ячеек первого столбца матоицы, втооые выходы, мат- оичных коммутаторов,соединены с третьими входами соответствующих сумматоров блока сумматоров, выходы элементов ИЛИ второй группы соединены с первыми вxoдa tи соответствующих вычислительных ячеек первого столб

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Gnild Н.Н | |||

| Some Cellular Logic Arrays for Non - Restoring Binary Division | |||

| - The Radio and Electronic Eng., 1970, 39, №6, pp | |||

| Способ изготовления струн | 1924 |

|

SU345A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Арифметика цифроfebix машин.М., Наука, 1969 | |||

| Фрикционная муфта с переменною скоростью вращения | 1920 |

|

SU444A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-01-15—Публикация

1983-05-06—Подача