Изобретение относится к вычислительной технике и может быть использо-1 вано при построении однотактовых вычислителей матричного типа для выполнения операции умножения и деления двоичных целых и дробных чисел, представленных в дополнительном коде.

Цель изобретения - расширение , . функциональных возможностей за счет умножения и деления двоичных чисел в дополнительных кодах.

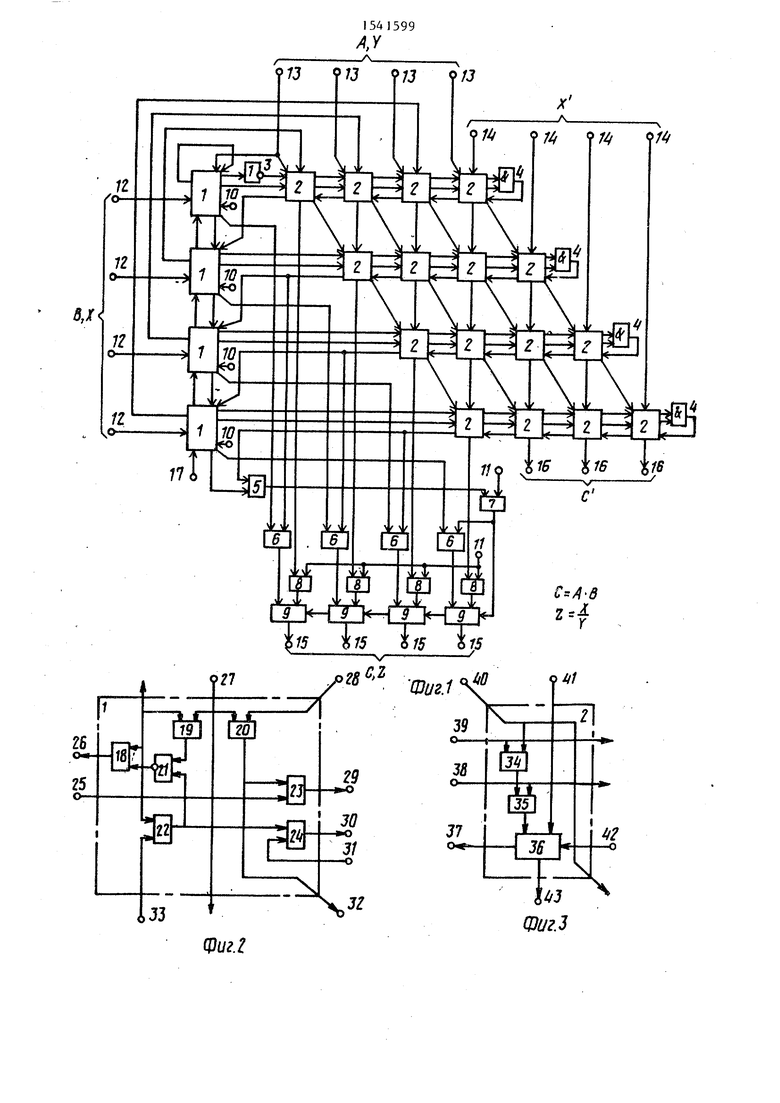

На фиг. 1 приведена структурная схема предлагаемого устройства при на фиг. 2 функциональная схема узла; на фиг. 3 - функциональная схема ячейки, используемой в устройстве; на фиг. 4 и 5 - схемы вычислительных процессов, происходящих при

умножении и делении (N - разрядность операндов).

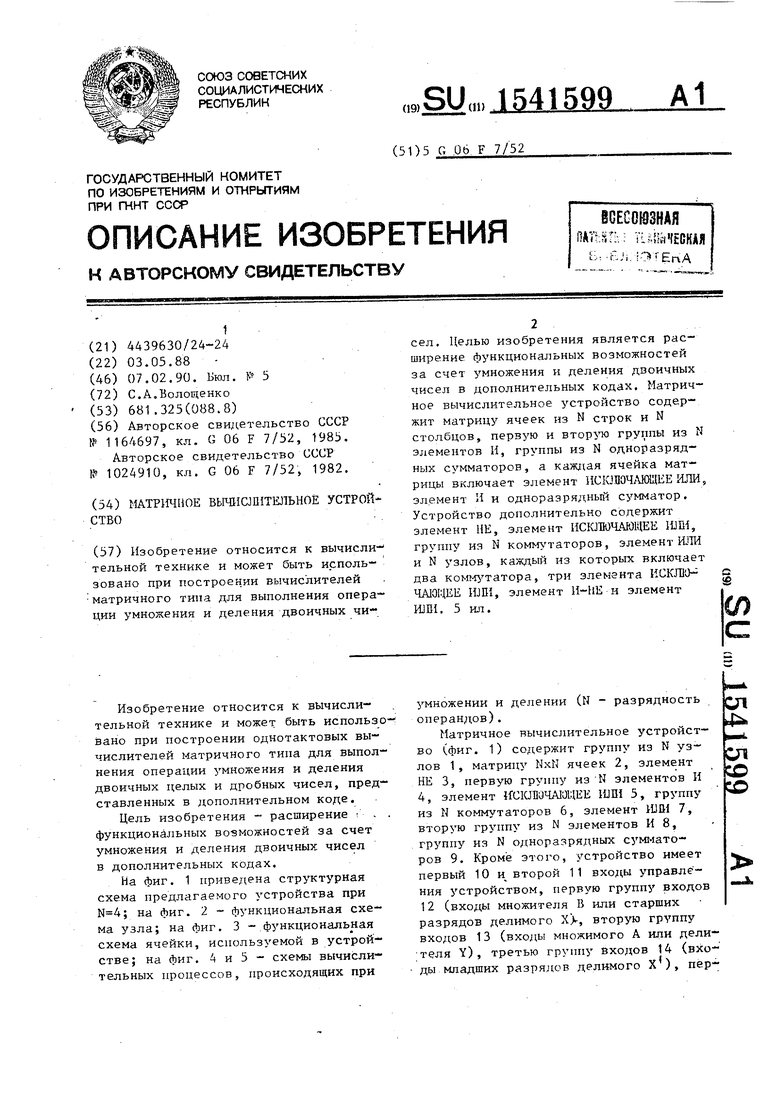

Матричное вычислительное устройство (фиг. 1) содержит группу из N узлов 1, матрицу NxN ячеек 2, элемент НЕ 3, первую группу из N элементов И 4, элемент {ГСКЛЮЧАЮЦЕЕ ИЛИ 5, группу из N коммутаторов 6, элемент ИЛИ 7, вторую группу из N элементов И 8, группу из N одноразрядных сумматоров 9. Кроме этого, устройство имеет первый 10 и второй 11 входы управления устройством, первую группу входов 12 (входы множителя В или старших разрядов делимого Х, вторую группу входов 13 (входы множимого А или делителя Y), третью группу входов 14 (входы младших разрядов делимого X ), персд

Јь

:л

ее о

вую группу выходов 13 (выходы старши разрядов произведения С или частного Z) , вторую группу выходов 16 (выходы младших разрядов произведения С ), а также вход 17 логического нуля.

Каждый узел 1 (фиг. 2), выполняющий в устройстве функции локального (поразрядного) управления, содержит первый коммутатор 18, первый 19 и второй 20 элементы ИС1СЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ 21, третий элемент ИСКЛЮЧАЮЩЕЕ ШШ 22, второй коммутатор 23 и элемент ИЛИ 24. Кроме этого, узел 1 имеет вход 25, подключенный к первому входу коммутатора 18, первым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и 22, а также второму входу коммутатора 23, выход 26 первого коммута-

тораfвход 27, подключенный к второму JQ систему счисления (-1, 0, +0, ис30

и первому входу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и 20 соответственно, второй вход 28 второго элемента ИСЮШЧАЮЩЕЕ ИЛИ, выход 29 второго коммутатора, выход 30 элемента ИЛИ, второй вход 31 25 элемента ИЛИ, выход 32 второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход 33 третьего элемент ИСКЛЮЧАЮЩЕЕ ШШ.

Каждая ячейка 2 (фиг. 3), выполняющая функции поразрядной арифметической обработки, содержит элемент ИСКЛЮЧАЮЩЕЕ ШШ 34, элемент И 35 и одноразрядный сумматор 36. Кроме этого., ячейка 2 имеет выход 37 переноса одноразрядного сумматора, второй вход 38 элемента И, первый 39 и второй 40 входы элемента ИСКЛЮЧАЮЩЕЕ ШШ, второй вход 41, вход переноса 42 и выход 43 одноразрядного сумматора соответственно.

Входы управления коммз таторов не изображены. При делении коммутаторы передают информацию через первые входы, расположенные на условных графических отображениях (УГО) сверху и слева, а при умножении - с вторых входов, расположенных соответственно снизу и справа.

Номера строк в устройстве возрастают сверху вниз, а столбцов - слева направо. Аналогична нумерация элемен- тов в группах. Входы знаковых разрядов операндов и выход знака результата расположены в разрядных группах слева и сверху.

Умножение в устройстве выполняется следующим образом (фиг.1). На вход 10 управления должен поступать нулевой урове.нь, а на вход 11 - еди-

пользуемую только для внутреннего представления множителя. В этом слу чае произведение С будет представле но обычным двоичным кодом (0,1), та как оно получено в результате сумми рования либо вычитания кодов множим го А, не подвергавшихся преобразова нию. Код (2Н-1)-разрядного произвед ния С формируется на выходах 15 и 1 устройства (соответственно N старши и N-1 младших разрядов).

Алгоритм умножения основан на сл дующей формуле (для дробных чисел):

О +1г(а„ФЬ; Д(Ь;®Ь;

-Ч2.2.,

I :

(1

40

45

где А - множимое, равное а0,а,,а ..

а(Ы Ь; - разряд множителя В (где В

Ь„ ,b, ,b. . .bN.f), причем Ь,(0,1) и считается, что Ь- - разряд множителя В, выражен ного в двоичной системе счи ления (-1, 0, +1), причем Ь „, (-1, 0, +1);

2-2 - константный поправочный чле Ф - операция ИСКЛЮЧАЮЩЕЕ ШШ.

55

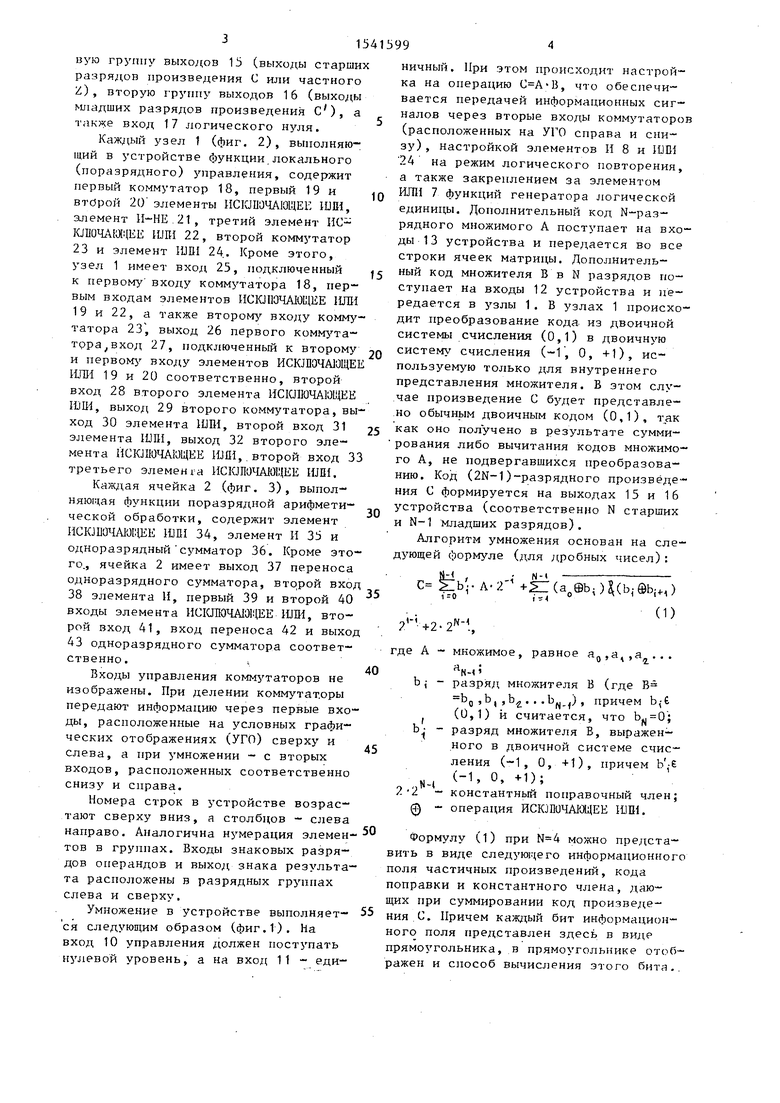

Формулу (1) при можно предст вить в виде следующего информационн поля частичных произведений, кода поправки и константного члена, дающих при суммировании код произведения С. Причем каждый бит информацио ного поля представлен здесь в виде прямоугольника, в прямоугольнике от ражен и способ вычисления этого бит

ничный. При этом происходит настройка на операцию , что обеспечивается передачей информационных CHI- налов через вторые входы коммутаторов (расположенных на УГО справа и снизу) , настройкой элементов И 8 и ИЛИ 24 на режим логического повторения, а также закреплением за элементом

ИЛИ 7 функций генератора логической единицы. Дополнительный код N-раз- рядного множимого А поступает на входы 13 устройства и передается во все строки ячеек матрицы. Дополнительный код множителя В в N разрядов поступает на входы 12 устройства и передается в узлы 1. В узлах 1 происходит преобразование кода из двоичной системы счисления (0,1) в двоичную

0

пользуемую только для внутреннего представления множителя. В этом случае произведение С будет представлено обычным двоичным кодом (0,1), так как оно получено в результате суммирования либо вычитания кодов множимого А, не подвергавшихся преобразованию. Код (2Н-1)-разрядного произведения С формируется на выходах 15 и 16 устройства (соответственно N старших и N-1 младших разрядов).

Алгоритм умножения основан на следующей формуле (для дробных чисел):

О +1г(а„ФЬ; Д(Ь;®Ь;)

-Ч2.2.,

I :

(1)

где А - множимое, равное а0,а,,а ...

а(Ы Ь; - разряд множителя В (где В

Ь„ ,b, ,b. . .bN.f), причем Ь,6 (0,1) и считается, что Ь- - разряд множителя В, выраженного в двоичной системе счисления (-1, 0, +1), причем Ь ,-6 „, (-1, 0, +1);

2-2 - константный поправочный член; Ф - операция ИСКЛЮЧАЮЩЕЕ ШШ.

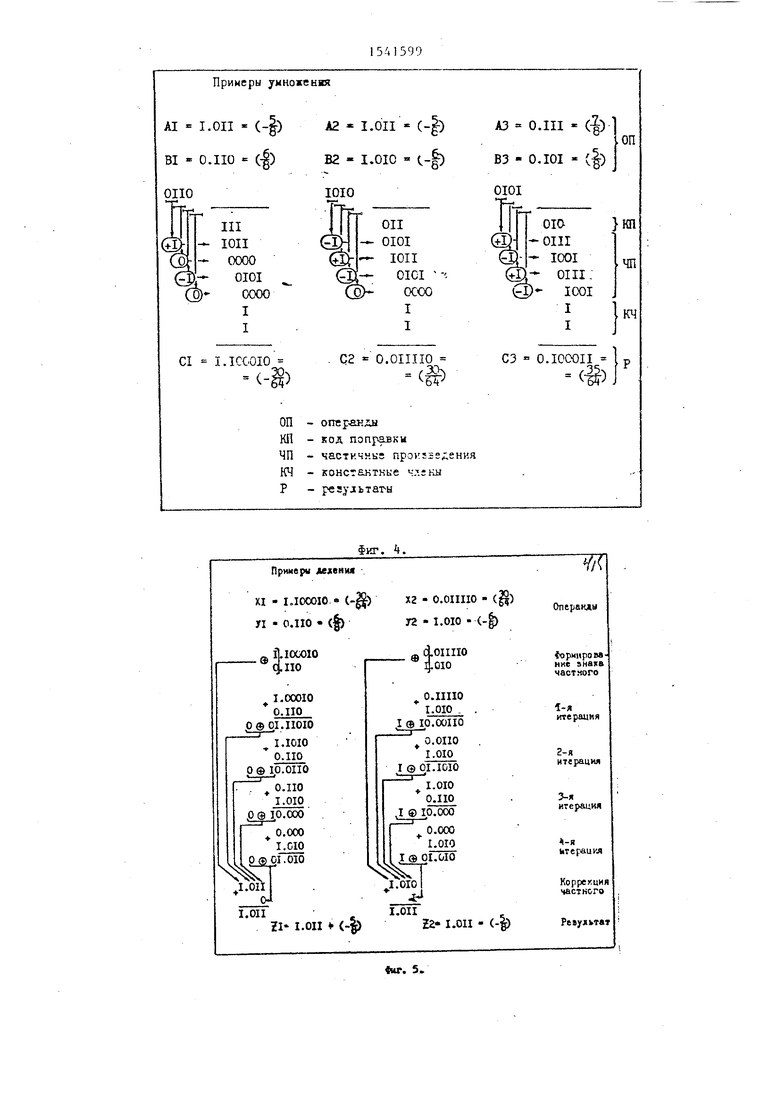

Формулу (1) при можно представить в виде следующего информационного поля частичных произведений, кода поправки и константного члена, дающих при суммировании код произведения С. Причем каждый бит информационного поля представлен здесь в виде прямоугольника, в прямоугольнике отображен и способ вычисления этого бита.

N-

1-1

(a0€b,)Sc(b,©blt,).2

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Вычислительное устройство | 1989 |

|

SU1697077A2 |

Изобретение относится к вычислительной технике и может быть использовано при построении вычислителей матричного типа для выполнения операции умножения и деления двоичных чисел. Целью изобретения является расширение функциональных возможностей за счет умножения и деления двоичных чисел в дополнительных кодах. Матричное вычислительное устройство содержит матрицу ячеек из N строк и N столбцов, первую и вторую группы из N элементов И, группу из N одноразрядных сумматоров, а каждая ячейка матрицы включает элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И и одноразрядный сумматор. Устройство дополнительно содержит элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, группу из N коммутаторов, элемент ИЛИ и N узлов, каждый из которых включает два коммутатора, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ и элемент ИЛИ. 5 ил.

;iJ il г1.1 °f.

Код поправки формируется на выхода коммутаторов 18 узлов 1 и поступает для суммирования на вторые входы сум- маторов ячеек 2 первой строки матрицы Вычисление каждого информационного разряда кода поправки происходит на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 19 (операция aa@bt-), элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 22 (операция ,-) и элементе И-НЕ 2Т..

Вычисление частичных произведений выполняется на элементах ИСКЛЮЧАЮЩЕЕ и И 35 каждой из строк ячееек 2 матрицы, управляемых сигналами с выходов коммутатора 23 и элемента ИЛИ 24 соответствующего этой строке узла 1. При Ь.+1 на выходе коммутатора 23 и элемента ИЛИ 24 формируется код 01, при Ь.-1 формируется код 11, а при Ь. 0 этот код равен 10 или 00. Сами же Ь,- определяются по значению двух разрядов bj и Ь(м. Причем , если Ь и Ь,-м одинаковы; в противном случае , если Ь- 1, иначе ,

если .

N -1 Константный чл ен 2- 2 задается

единичным уровнем на выходе элемента ИЛИ 1 (так как на входе 11 единица), и уровнем единицы, формируемым при этом на выходе N-ro коммутатора 6.

Сформированные таким образом слагаемые формулы (1) суммируются сумматорами ячеек 1 и сумматорами 6 группы. Полнорлзрядное произведение фор-

, Частичные произведения

b:- A-7

,-1

Константный член 2-2

к-

5

0

0

5

0

5

мируется на выходах сумматоров ячеек 2М-й строки и группы 6, и далее поступает на выходы 15 и 16. При этом на входах 14 должен быть нулевой код при вычислении . В противном случае устройство реализует формулу С АВ+Х (где X1 - код на входах 14), что позволяет дополнительно вводить поправки в виде смещений либо осуществлять округление при усечении разрядности произведения.

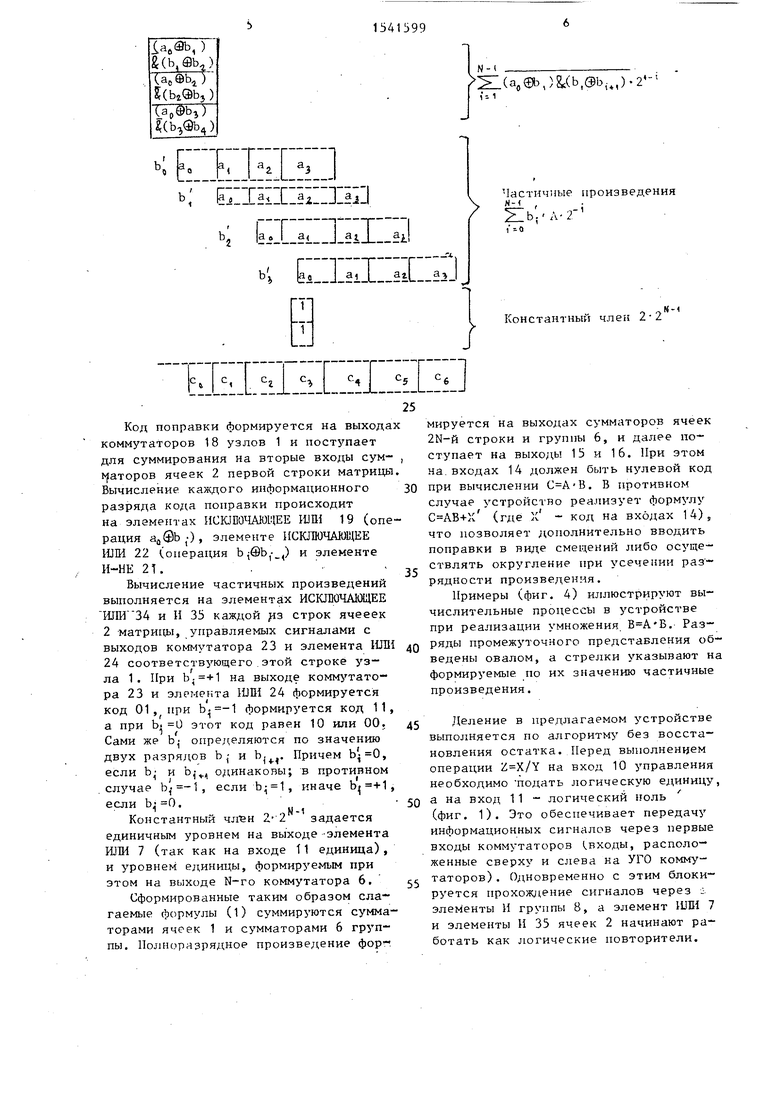

Примеры (фиг. 4) иллюстрируют вычислительные процессы в устройстве при реализации умножения . Разряды промежуточного представления обведены овалом, а стрелки указывают на формируемые по их значению частичные произведения.

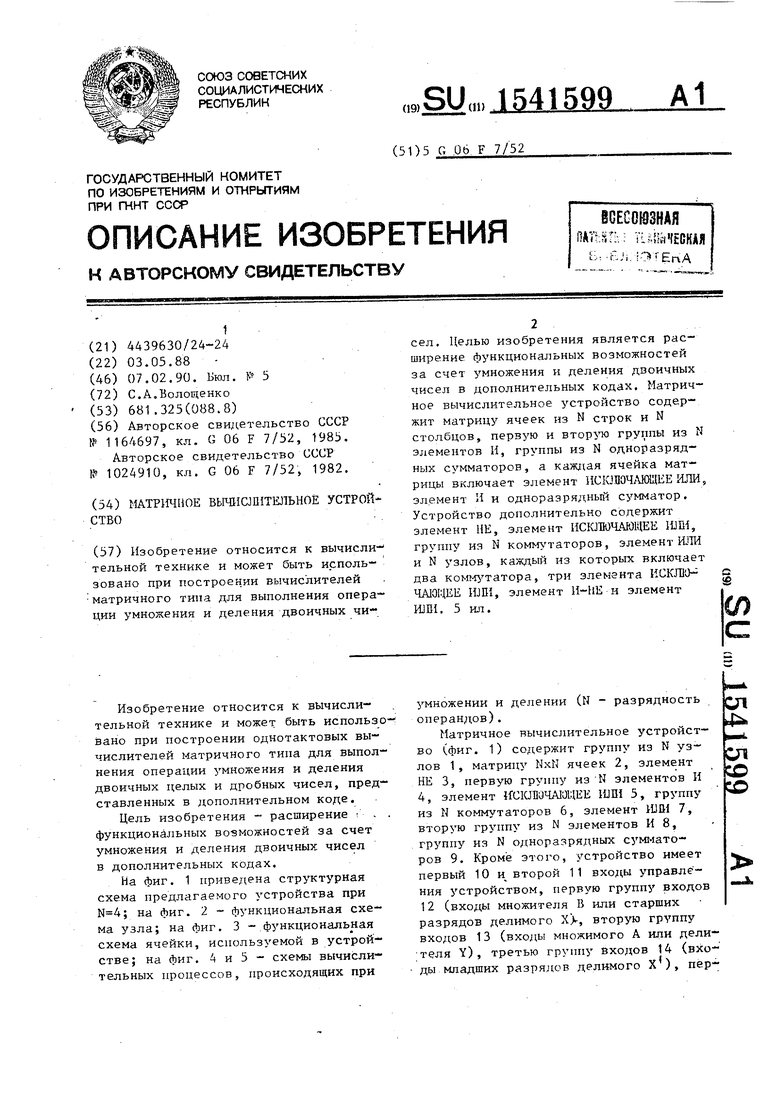

Деление в предлагаемом устройстве выполняется по алгоритму без восстановления остатка. Перед выполнением операции на вход 10 управления необходимо подать логическую единицу, а на вход 11 - логический ноль (фиг. 1). Это обеспечивает передачу информационных сигналов через первые входы коммутаторов (.входы, расположенные сверху и слева на УГО коммутаторов) . Одновременно с этим блокируется прохождение сигналов через . элементы И группы 8, а элемент ИЛИ 1 и элементы И 35 ячеек 2 начинают работать как логические повторители.

Код 2М-разрядного делимого X поступает на входы 12 (старшие разряды) и входы 14 (младшие разряды). Код делителя Y в N разрядов - на входы 13 устройства. Между величинами делимого и делителя должно выполняться соотношение . Код частного Z формируется на выходах Т5.

. Знак частного Z0 формируется на выходе элемента ИСКЛЮЧАЮЩЕЕ HJIH 20 первого узла 1 и передается на знаковый разряд выходов 15, проходя последовательно, первый коммутатор 6 и первый сумматор 9. Процесс вычисления остальных цифр частного Z- состоит в итерационном вычислении очередных остатков (ц , формируемых последовательно в каждой из строк ячеек 2 матрицы. При этом каждая очередная цифра частного Z вычисляется в (1+1)-м узле 1 на основе следующих выражений

,+SiBn(ft)Y, при , (2)

где Sign(Ј,)

+ 1, если знаки (},, и Y противоположны; -1 , если знаки ( и Y равны;

и Y противо-

0,если знаки Q и Y противо- иоложны;

1,если знаки Q-, и Y равны. Причем вычитание.в выражении (2)

заменено суммированием с дополнительным кодом путем инвертирования кодаY на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 34 яче- ек 2 и суммирования единицы в младший разряд через элемент И 4.

Определение выполняемого действия (суммирование либо вычитание), а также очередной цифры Zj осуществляется на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 20 (i-f +1)-го узла 1. Вычисленные таким образом Z j поступают через коммутато- ры 6 на первые входы сумматоров 9 группы, на которых осуществляется корекция частного.

Необходимость коррекции частного

следует из особенности деления в до-

полнительных кодах и выполняется после определения N-разрядного кода Z0 ,Z, ,Z,j .. . Zw.f. Для этого вычисляется дополнительная цифра частного Zn (это осуществляется в N-й строке ячеек 2 матрицы с использованием элемента ИСКЛЮЧАЮЩЕЕ ШШ 5), после чего Z. суммируется в младший разряд этого кода.

0

5

0

r

0 5

0

,

Таким образом, окончательный результат равен

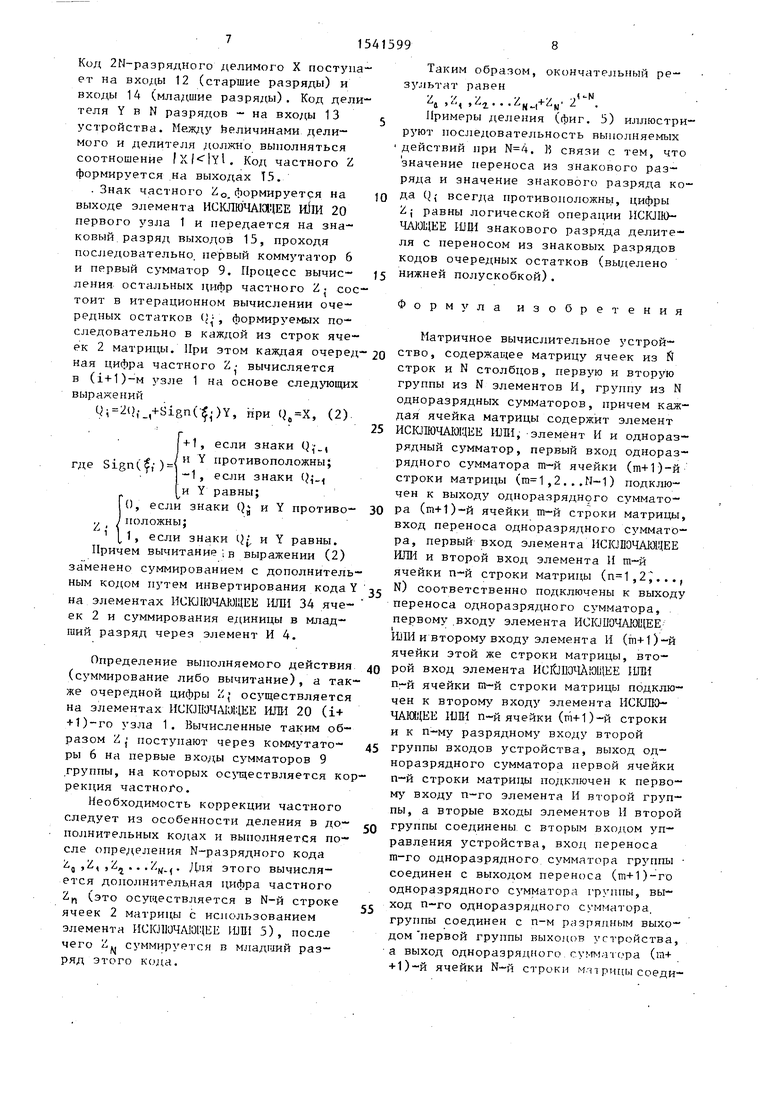

/ /+/. а ч Ч w Примеры деления (фиг. 5) иллюстрируют последовательность выполняемых действий при . К связи с тем, что значение переноса из знакового разряда и значение знакового разряда кода Q; всегда противоположны, цифры Z; равны логической операции ИСКЛЮЧАЮЩЕЕ знакового разряда делителя с переносом из знаковых разрядов кодов очередных остатков (выделено нижней полускобкой).

Формула изобретения

Матричное вычислительное устройство, содержащее матрицу ячеек из ft строк и N столбцов, первую и вторую группы из N элементов И, группу из N одноразрядных сумматоров, причем каждая ячейка матрицы содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И и одноразрядный сумматор, первый вход одноразрядного сумматора m-й ячейки (т+1)-й строки матрицы (,2...N-1) подключен к выходу одноразрядного сумматора (т+1)-й ячейки tn-й строки матрицы, вход переноса одноразрядного сумматора, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второй вход элемента И т-и ячейки n-й строки матрицы (,2,..( N) соответственно подключены к выходу переноса одноразрядного сумматора, первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второму входу элемента И (m-f-1 )-й ячейки этой же строки матрицы, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ n-й ячейки га-й строки матрицы подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ n-й ячейки (т+1)-й строки и к n-му разрядному входу второй группы входов устройства, выход одноразрядного сумматора первой ячейки п-и строки матрицы подключен к первому7 входу n-го элемента И второй группы, а вторые входы элементов И второй группы соединены с вторым входом управления устройства, вход переноса m-ro одноразрядного сумматора группы соединен с выходом переноса (тп+1)-го одноразрядного сумматора группы, выход п-го одноразрядного сумматора. группы соединен с n-м разрядным выходом первой группы выходов устройства, а выход одноразрядного гуммлчора (га+ + 1)-й ячейки N-и строки м -п рчцы соединен с m-м разрядным выходом второй группы выходов устройства, о т л и- чающееся тем, что, с целью расширения функциональных вочможнос- тей за счет умножения и деления в дополнительных кодах, введены элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, группа из N коммутаторов, элемент ИЛИ и N управляющих узлов, каждый из которых содержит два коммутатора, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ и элемент ИШ1, n-й разрядный вход первой группы входов соединен с первым входом первого и третьего эле- ментов ИСКЛЮЧАЮЩЕЕ ИЛИ, первым входо первого коммутатора и вторым входом второго коммутатора п-го управляющего узла, а также с вторым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (п-1)-го управляющего узла, первый разрядный вход второй группы входов устройства соединен с вторым входом первого и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ каждого h-го управляющего узла и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ n-fo управляющего узла соединены соответственно с первым входом эле- мента И-НЕ и первым входом второго коммутатора этого же n-го управляющего узла, а выход и второй вход элемента И-НЕ п-го управляющего уЗла соединены соответственно с вторым входом первого коммутатора и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ n-го управляющего узла, причем к выходу третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ n-го управляющего узла подключен первый вход элемента ИЛИ этого же узла, выход переноса одноразрядного сумматора первой ячейки m-й строки матрицы соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (m+1)-ro управляющего узла, а выход переноса одноразрядного сумматора первой ячейки N-и строки матрицы соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соеди- нен с первым входом элемента ИЛИ, а второй вход и выход этого элемента ИЛИ соединены соответственно с вторы входом управления устройства и входо переноса N-ro одноразрядного суммато

ра Группы, первый и второй входы т-го

Q з 0 5 0 5 о 5 о

5

коммутатора группы соединены соот- ветственно с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ та-го управляющего узла и выходом переноса одноразрядного сумматора первой ячейки чп+1)-й строки матрицы, первый и второй входы N-го коммутатора rpvmibi соединены соответственно с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ N-го управляющего узла и выходом элемента ИЛИ, первый и второй входы n-го одноразрядного сумматора группы соединены соответственно с выходами п-го коммутатора и п-го элемента И второй группы, вход переноса одноразрядного сумматора N-й ячейки n-й строки матрицы соединен с выходом n-го элемента И первой группы, а первый и второй входы этого же элемента И соединены соответственно с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом элемента И этой же N-й ячейки п-и строки матрицы, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второй вход элемента И первой ячейки (т+1)-й строки матрицы соединены соответственно с выходом второго коммутатора и выходом элемента ИЛИ (m-M)-ro управляющего узла, выход второго коммутатора и выход элемента ИЛИ первого управляющего узла соединены соответственно с входом элемента НЕ и вторым входом элемента И первой ячейки первой строки матрицы, а выход элемента НЕ соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ этой же ячейки, второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого управляющего узла соединен с выходом первого коммутатора первого управляющего узла, второй вход одноразрядного сумматора гп-й ячейки первой строки матрицы соединен с выходом первого коммутатора (т-И-)то узла, второй вход одноразрядного сумматора N-и ячейки п-и строки матрицы соединен с n-м разрядным входом третьей группы входов устройства, вторые входы, элементов ИЛИ каждого управляющего узла, а также входы управления коммутаторов группы и коммутаторов всех управляющих узлов подключены к первому входу управления устройства, второй вход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ N-го управляющего узла подключен к входу, логического нуля устройства.

tf 7J 9/J

-aa/1

3; -r-

Фиг.

X л

9# / f/ #

si

Фкг. 4.

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-03—Подача