со о:)

а о

Изобретение относится к вычислительной технике и может найти применение для контроля цифровых систем различного назначения.

По основному авт. св. № 894712 известно устройство для контроля цифровых систем, которое содерж)т регистр сдвига блока вызова операции, первый выход которого соединен с входом блока памяти, шифратор, блок селекции, первый управляющий вход которого соединен с первым выходом блока вызова операции, второй вход которого соединен с вторым управляющим входом блока селекции, третий управляющий вход которого соединен с третьим выходом блока вызова операции, четвертый выход которого соединен с информационным входом регистра сдвига, установочный вход которого соединен с первым входом блока вызова операции и является входом признака кода операции устройства, кодовый вход которого соединен с вторым входом блока вызова oneрации, третий вход которого является тактовым входом устройства, группа информационных входов которого соединена с первой группой информационных входов блока селекции, вторая группа информационных входов которого соединена с выходом блока памяти, выход регистра сдвига соединен с четвертым управляющим входом блока селекции, группа выходов которого соединена с входами щифратора, выход которого является выходом устройства.

Кроме того, блок вызова операции устройства содержит дешифратор, элемент ИЛИ, регистр, линию задержки, элемент И первый вход которого является первым входом блока, второй вход которого соединен с входом регистра, выходы которого соединены с входами дешифратора, выход которого является первым выходом блока, второй вход которого соединен с первым выходом линии задержки, второй вход которой является третьим выходом блока, четвертый выход которого соединен с выходом элемента И, второй вход которого соединен с выходом элемента ИЛИ, вход которого соединен с входом линии задержки и является

третьим входом блока.

Кроме того, блок селекции устройства содержит три группы элементов И, группу элементов ИЛИ, входной регистр, выходной регистр, управляющие входы элементов И первой группы являются первым управляющим входом блока, второй управляющий вход которого соединен с управляющими входами элементов И второй группы, первые информационные входы которых соединены соответственно с выходами выходного регистра, информационные входы которого соединены с выходами элементов И третьей группы, первые информационные входы которых соединены соответственно с вторыми информационными входами элементов И второй группы и с соответствующими выходами входного регистра, управляющий вход которого соединен с управляющим входом выходного регистра и является третьим управляющим входом блока, четвертый управляющий вход которого соединен с управляющими входами элементов И третьей группы, вторые информационные входы которых соединены соответственно с вь1ходами элементов ИЛИ, входы которых соединены соответственно с выходами элементов И первой группы, входы которых являются первой группой информационных входов блока, вторые информационные входь которого соединены с информационными входами входного регистра, выходы элементов И второй группы являются группой выходов блока

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности контроля формирования числовой информации.

Поставленная цель достигается тем, что в устройство для контроля цифровых систем введены регистр информации и коммутатор информации, в состав которого входят п групп элементов И (п - количество объектов контроля), группа элементов ИЛИ и группа элементов НЕ, причем первые входы элементов И каждой группы коммутатора информации являются второй группой информационных входов устройства, выходы i-x элементов И каждой группы коммутатора информации соединены с входами i-ro элемента ИЛИ группы коммутатора информации (1 i m), где ш - количество элементов в группе, выходы которых соединены с единичными входами соответствующих разрядов регистра информации и с входами соответствующих элементов НЕ группы, выходы которых соединены с нулевыми входами соответствующих разрядов регистра информации, выход которого является информационным выходом устройства, вторые входы каждой группы элементов И коммутатора информации объединены и соединены с первым выходом блока вызова операции, выход шифратора соединен с третьими входами всех элементов И всех групп коммутатора информации.

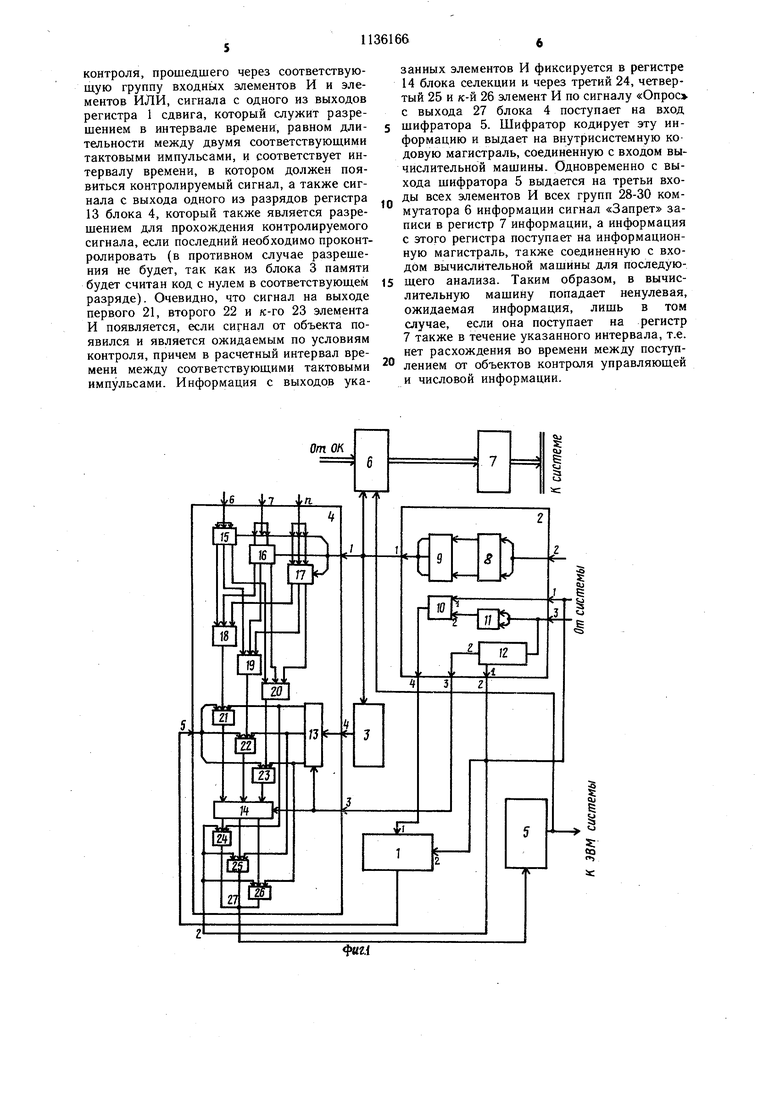

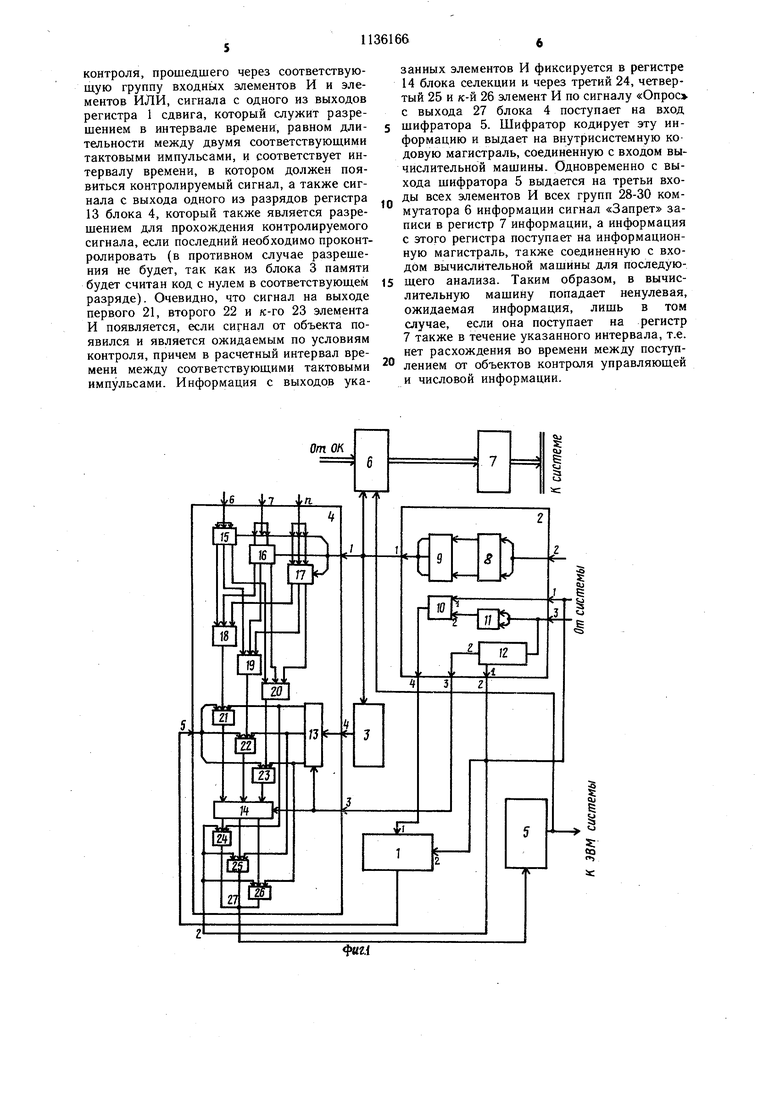

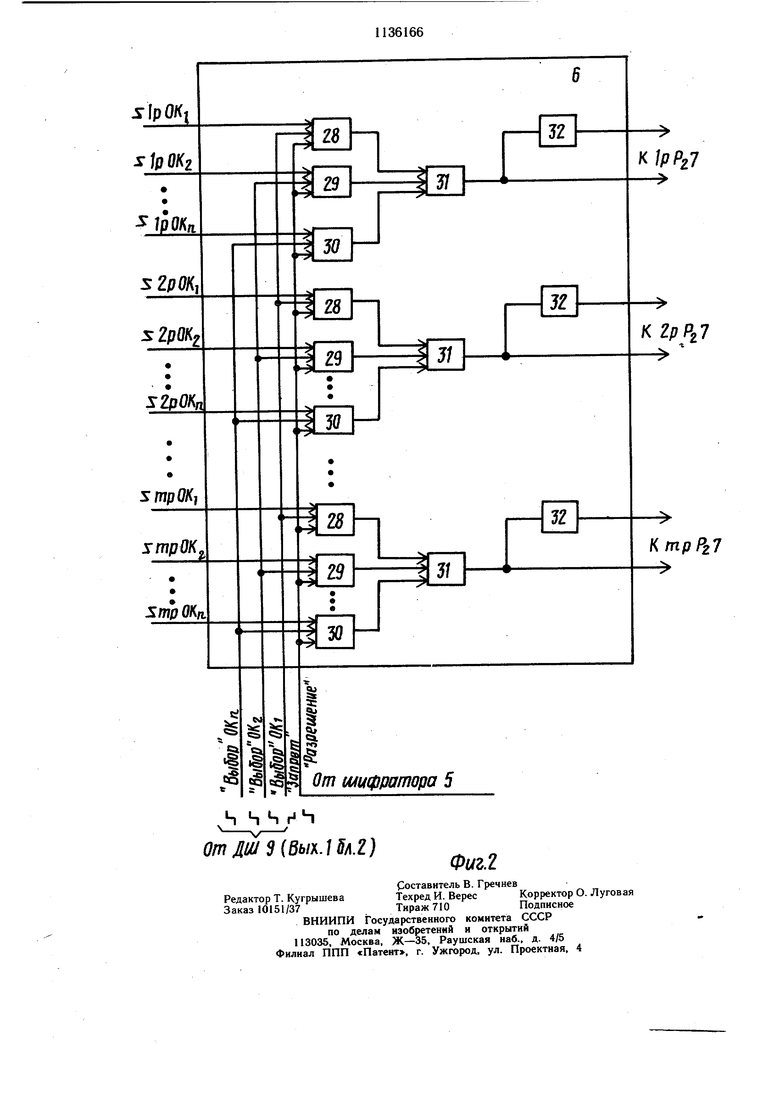

На фиг. 1 приведена функциональная схема устройства для контроля цифровых систем; на фит. 2 - функциональная схема коммутатора информации.

Устройство для контроля цифровых систем содержит регистр 1 сдвига, блок 2 вызова операции, блок 3 памяти, блок 4 селекции, шифратор 5, коммутатор-6 информации и регистр 7 информации. При этом регистр 7 является парафазным. Блок 2 вызова операции содержит регистр 8, дешифратор 9, элемент И 10, элемент ИЛИ 11, линию 12 задержки. Первый вход элемента И 10 является первым входом блока.

второй вход которого соединен с входом регистра 8, выходы которого соединены с входом дешифратора 9, выход которого является первым выходом блока, второй выход Kofoporo соединен с первым выходом линии

12задержки, второй выход которой является третьим выходом блока, четвертый выход которого соединен с выходом элемента И 10, второй вход которого соединен с выходом элемента ИЛИ 11, вход которого соединен с входом линии 12 задержки и является третьим входом блока. Блок 4 селекции содержит входной и выходной регистры

13и 14, группу элементов И 15-17, группу элементов ИЛИ 18-20, группу элементов И 21-23 и 24-26, управляющие входы элементов И 15-17 первой группы являются первым управляющим входом б.тока, второй управляющий вход которого соединен с управляющими входами элементов И 24-26 третьей группы, первые информационные входы которых соединены соответственно с выходами выходного регистра 14, информационные входы которого соединены соответственно с выходами элементов И 21-23 второй группы, первые информационные входы которых соединены соответственно с вторыми информационными входами элементов И третьей группы и соответствующими выходами входного регистра 13, управляющий вход которого соединен с упррвляющим входом выходного регистра 14 и является третьим управляющим входом блока, четвертый управляющий вход которого соединен с входным регистром, соединенным с управляющими входами элементов И второй группы, вторые информационные входы которых соединены соответственно с выходами элементов ИЛИ 18-20, входы которых соединены соответственно с выходами элементов И 15-17 первой группы, входы которых являются первой группой информационных входов блока, вторые информационные входы которого соединены с входами элементов И 24-26 третьей группы, выходы 27 которых являются выходами блока, а входы элементов И 21 - 23 подключены к пятым информационным входам блока.

Коммутатор 6 информации (фиг. 2) содержит группы элементов И 28-30, группу элементов ИЛИ 31 и группу элементов НЕ 32.

Устройство работает следующим образом.

На второй вход блока 2 вызова операции поступает из цифровой системы по кодовой магистрали код операции, выполняемой в системе в данный момент, а на коммутатор 6 информации - соответствующая числовая информация с объектов контроля. Код операции поступает на регистр 8 блока 2 вызова операции и после дещифрации (на дещифраторе 9) на первом выходе блока 2 появляется сигнал, поступающий на соответствующую группу элементов И 15-17 через

первый вход блока 4 селекции. Этот же сигнал поступает на коммутатор 6 информации. Поскольку каждому коду операции соответствует своя щина дешифратора 9, обеспечивается выбор одной из групп элементов И. Объекты контроля, вырабатывающие сигналы и числовую информацию (например, блоки приборов системы или объекты управления), подключаются к информационным входам элементов И через шестой,

седьмой и п-и входы блока 4 селекции. Однако сигналы от объектов контроля пройдут через элементы И лищь при наличии сигнала разрешения на соответствующих шинах дешифратора 9 блока 2, поступающего с

5 первого входа блока 4. Таким образом по коду операции осуществляется выбор одного из объектов контроля. Этот же сигнал с первого выхода блока 2 вызова операции поступает, на вход коммутатора 6 и является разрешающим для записи поступающей

0 от объектов контроля числовой информации в регистр 7 информации. Другим сигналом, разрешающим запись числовой информации в регистр 7 информации, является сигнал, поступающий с выхода шифратора 5. При

5 наличии этих двух сигналов запись информации в парафазный регистр 7 информации разрешается.

Сигнал «Признак кода операции из вычислительной системы поступает на установочный вход регистра 1 сдвига и производит в него запись (Ч-1). Этот же сигнал поступает через nepJBbm -вход блока 2 на первый вход элемента И 10 блока 2 вызова операции, на второй вход которого поступают тактовые импульсы с магистрали, прощедшие через третий вход блока 2 вы зова операции и элемент ИЛИ 11. С выхода элемента И 10 через четвертый выход блока 2 сигналы поступают на первый вход сдвигового регистра 1 и используются как сдвиговые импульсы. Восьмой тактовый импульс

0 с третьего входа блока 2 вызова операции поступает на вход линии 12 задержки и через ее выход, соединенный с вторым выходом блока 2, подается как сигнал «Опрос на второй вход блока 4 селекции, а с входа, соединенного с третьим выходом блока 2

5 операции, снимается сигнал «Уст.«О регистров 13 и 14 блока 4 селекции (сигнал поступает на третий вход этого блока). Выходы . дешифратора 9 блока 2 соединены с входом блока 3 постоянной памяти 3 и обесQ печивают считывание информации параллельного кода в регистре 13 через четвертый вход блока 4 селекции. Параллельный код содержит единицы в тех разрядах, которые будут использоваться как разрешение при выделении контрольных сигналов от объек5 та контроля в блоке 4 селекции.

Таким образом, на первом 21, втором 22 и к-м 23 элементах И проходит совпадение следующих сигналов: сигнала от объекта

контроля, прошедшего через соответствующую группу входных элементов И и элементов ИЛИ, сигнала с одного из выходов регистра 1 сдвига, который служит разрешением в интервале времени, равном длительности между двумя соответствуюш,ими тактовыми импульсами, и соответствует интервалу времени, в котором должен появиться контролируемый сигнал, а также сигнала с выхода одного из разрядов регистра 13 блока 4, который также является разрешением для прохождения контролируемого сигнала, если последний необходимо проконтролировать (в противном случае разрешения не будет, так как из блока 3 памяти будет считан код с нулем в соответствующем разряде). Очевидно, что сигнал на выходе первого 21, второго 22 и к-го 23 элемента И появляется, если сигнал от объекта появился и является ожидаемым по условиям контроля, причем в расчетный интервал времени между соответствующими тактовыми импульсами. Информация с выходов указанных элементов И фиксируется в регистре 14 блока селекции и через третий 24, четвертый 25 и к-й 26 элемент И по сигналу «Опрос с выхода 27 блока 4 поступает на вход

щифратора 5. Шифратор кодирует эту информацию и выдает на внутрисистемную кодовую магистраль, соединенную с входом вычислительной машины. Одновременно с выхода шифратора 5 выдается на третьи входы всех элементов И всех групп 28-30 коммутатора 6 информации сигнал «Запрет записи в регистр 7 информации, а информация с этого регистра поступает на информационную магистраль, также соединенную с входом вычислительной машины для последующего анализа. Таким образом, в вычислительную машину попадает ненулевая, ожидаемая информация, лишь в том случае, если она поступает на регистр 7 также в течение указанного интервала, т.е. нет расхождения во времени между поступлением от объектов контроля управляющей и числовой информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых систем | 1980 |

|

SU894712A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2133500C1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Устройство для формирования лексических массивов | 1980 |

|

SU934487A1 |

| Устройство приема команд телеуправления по каналам телефонной связи | 1991 |

|

SU1808172A3 |

| Устройство для отладки программ | 1980 |

|

SU960828A1 |

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СИСТЕМ по авт. св. № 894712, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности контроля формирования числовой информации, в него введены регистр информации и коммутатор информации, содержащий п групп элементов И (п - количество объектов контроля), группу элементов ИЛИ и группу элементов НЕ, причем первые входы элементов И каждой группы коммутатора информации являются второй группой информационных входов устройства, выходы i-x элементов И каждой груп пы коммутатора информации соединены с входами i-ro элемента ИЛИ группы коммутатора информации (), где количество элементов в группе , выходы которых соединены с единичными входами соответствующих разрядов регистра информации и с входами соответствующих элементов НЕ группы, выходы которых соединены с, нулевыми входами соответствующих разрядов регистра информации, выход которого является информационным выходом устройства, вторые входы каждой группь элементов И коммутатора информации объединены и соединены с первым выходом блока вызова (Л операции, выход шифратора соединен с третьими входами всех элементов И всех групп коммутатора информации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровых систем | 1980 |

|

SU894712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1983-01-11—Подача