(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ

1

Изобретение относится к вычислительной технике и может найти применение для контроля цифровых систем : различного назначения.

Известны устройства, позволяющие проводить контроль цифровых систем 1 и 2 .

Наиболее близким к предлагаемому является устройство для полуавтоматического контроля цифровых управляющих систем, содержащее блок перек.гпочения частоты опроса и сдвигающий регистр, ко входу которого подключен выход блока переключения частоты опроса, вход которого соединен с первым выходом блока управления, второй выход которого подк.гаочен к nepBOJviy входу устройства, ко второму выходу устройства подключен выход блока формирующих усилителей, вход которого соединен с первым выходом матрицы наборов микроопераций, к первому входу которой подключен выход блока вызова операций, ко второму входу - выход сдвигающего регистра, второй вход которого соединен со вторым выходом матрицы, первый выход устройства соединен со входом блока индикации 2.

Недостатки известного устройства ручная инициация выработки набора СИСТЕМ

сигналов для контроля и невозможность использования устройства одйОвре- . . менно с работой системы по прямому назначению. Кроме того, вырабатываемый набор сигналов, соответствукхций контролируемой операции, не используется для сравнения с набором сигна.пов, вырабатываемых в системе,как по количеству, так и по времени их

выработки в объектах контроля. Недостатком устройства является также жесткое внедрение его в контролируемую структуру по специальным технологическим цепям.

15 Цель изобретения - повышение оперативности контроля устройства для контроля цифровых систем.

Поставленная цель достигается тем, что в устройство для контроля

20 цифровых систем, содержащее регистр сдвига блока вызова операции, первый выход которого соединен со входом блока памяти, введен шифратор,. блок селекции, первый управляющий вход

25 которого соединен с первым выходом блока вызова операции, второй вход которого соединен со вторым управляющим входом блока селекции, третий управляющий вход которого соединен

30 .с третьим выходом блока вызова oneрации, четвертый выход которого сов димен с информационным входом регистра сдвига, установочный вход которого соединен с первым входом блока вызова операции и является входом признака кода операции устройства, кодовый-вход которого соединен со вторым входом блока вызова операции, третий вход которого является тактовым входом устройства, группа информационных входов которого соединена с первой группой информационных входов блока селекции, вторая группа информационных входов которого соединена с выходом блока памяти, выход регистра сдвига соединен с четвертым управляющим входом блока селекции, выход которого соединен со входом шифратора, йыход которого является выходом устройства.

При зтом блок вызова операции содержит дешифратор, регистр, элемент ИЛИ, линию задержки, элемент И, первый вход которого является первым входом блока, второй вход которого соединен со входом регистра, выходы которого соединены со входами дешифратора, выход которого является первым выходом блока, второй вход которого соединён с первЕЛМ выходом линии задержки, второй выход которой является третьим выходом блока, четвертый выход которого соединен с выходом элемента И, второй вход которого соединен с выходом элемента ИЛИ, вход которого соединен с входом линии задержки и является третьим вхо дом блока.

Кроме того, блок селекции содержит- три группы- элементов И, группу элементов ИЛИ, входной регистр, выходной регистр, управляющие входы элементов И первой группы являются первым управляющим входом блока, второй управляющий вход которого соединен с управляющими входами элементов И второй группы, первые информационные входы которых соединены соответственно с выходами выходного регистра, информационные входы которого соединены соответственно с выхо дами элементов И третьей группы, первые информационные входы которых соединены соответственно со вторыми информационными входами элементов И второй группы и с соответствующими выходами входного регистра, управляющий вход которого соединен с управляющим входом выходного регистра и является третьим управляющим входом блока, четвертый управляющий вход которого соединен с управляющими входами элементов И третьей группы, вторые информационные входы которых соединены соответственно с выходами элементов ИЛИ, входы которых соединены соответственно с выходами элементов И первой группы, входы которых являются первой группой информационных входов блока, вторые информационные входы которого соединены с информационными входами входного регистра, выходы элементов И второй группы являются группой выходов блока.

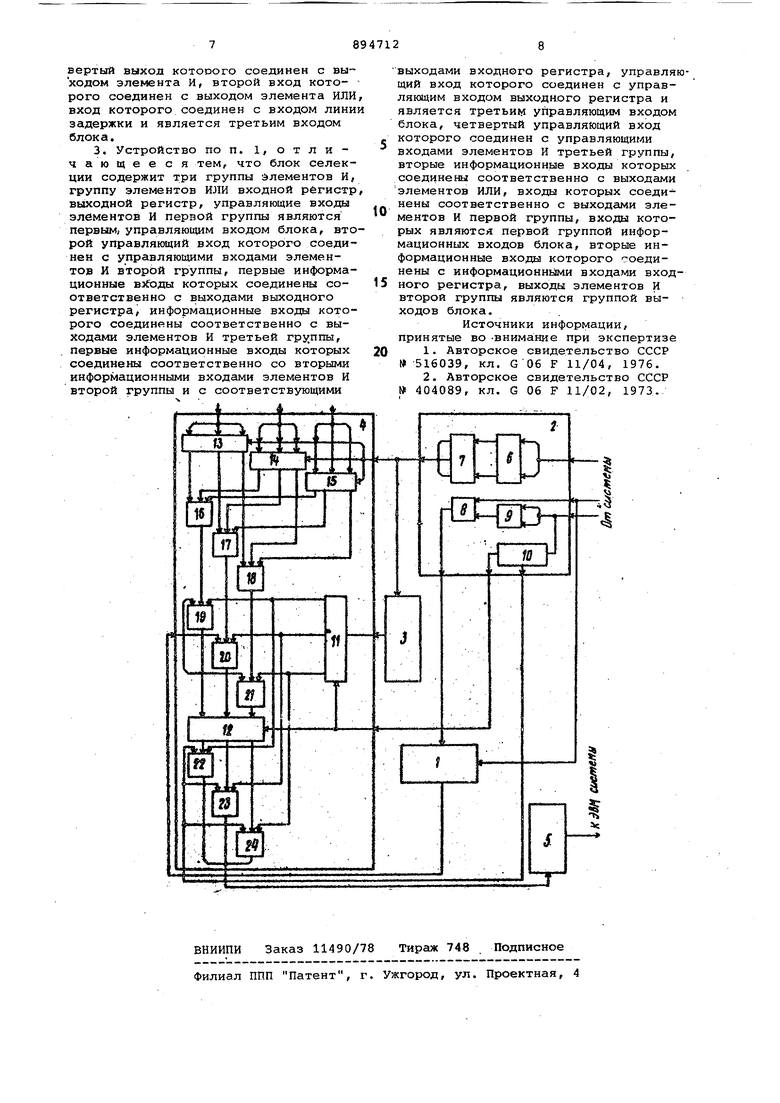

На чертеже йредставлена блок-схема устройства для контроля цифровых систем.

Устройство содержит регистр 1 сдвига, блок 2вызова операции, блок 3 памяти, блок 4 селекции и шифратор 5.

Регистр 1 сдвига, блок 3 памяти и шифратор 5 являются стандартными элементами цифровой вычислительной техники.

Блок 2 вызова операции включает в себя регистр б, дешифратор 7, элемент И 8, элемент ИЛИ 9 и линию 10 задержки.

Блок 4 селекции содержит входной регистр 11, выходной регистр 12, группы элементов И 13 - 15, группу элементов ИЛИ 16-24.

Устройство работает следующим образом.

Второй вход блока 2 вызова операции соединен с кодовой магистралью вычислительной системы, по которой передается код операции, выполняемой в системе в данный момент, Код операции поступает на регистр 6 блока 2 вызова операции и после дешифрации (на дешифраторе 7) на первом выходе блока 2 появляется сигнал, поступающий на соответствующую группу элементов И 13 - 15 через первый вход блока 4 селекции, т.е. каждому коду операции соответствует своя шина дешифратора 7, что обеспечивает выбор одной из групп. Объекты контроля, например блоки приборов системы, подключаются к информационным входам этих элементов через шестой, седьмой и п--ый входы блока 4 селекции. Однако сигналы от объектов контроля пройдут через элементы И лишь при наличии сигнала разрешения на соответствующих ( .Шинах дешифратора 7 блока 2, поступающих с первого входа блока 4. Таким образом, по коду операции осуществляется выбор одного из объектов контроля.

Сигнал Признак кода операции из вычислительной системы поступает на установочный вход блока 2 регистра i сдвига и производит в него запись 4-1. Этот же сигнал поступает через первый вход блока 2 на первый вход элемента 8 блока 2 вызова операции, на второй вход которого поступают тактовые импульсы с магистрали, прошедшие через третий вхо/д блока 2 вызова операции и элемент ИЛИ 9, С выхола элемента 8 через четвертый выход блока 2 сигналы поступают на первый вход сдвигового регистра 1 й используются как сдвиговые импульсы. Восьмой тактовый импульс с третьего входа блока 2 вы- зова операции поступает на вход линии 10 задержки и через ее выход, соединенный со вторым выходом блока 2, подается как сигнал Опрос на второй вход блока 4 селекции, а с выхода, соединенного с третьим выходом блока 2 вызова операции, снимается сигнал Уст. О с регистров 11 и 12, который поступает на третий вход блока 4 селекции. Выходы дешифратора 7 блока 2 соединены со входом блока 3 постоянной памяти и обеспечивают считывание информации параллельного кода в регистр 11 через четвертый вход блока 4 селекции. Параллельный код содержит единицы в тех .разрядах, которые будут использоваться как разрешение при выделении контрольных сигналов от объекта контроля в блоке селекции.

Таким образом, на первом 19, втором 20 и на элементе И 21 происходит совпадение следующих сигналов: сигнала от объекта контроля, прошедшего через соответствующую группу входных элементол.И и ИЛИ, сигнала с одного из выходов регистра 1 сдвига, который служит разрешением в инвервале времени, равном длительности между двумя соответствующими тактовыми импульсами и соответствует интервалу времени, в котором должен появиться контролируемый сигнал, а также сигНсша с выхода одного из разрядов регистра 11 блока 4, который также является разрешением для прохождения контролируемого сигнала, если последний необходимо проконтролировать {в противном случае разрешения не будет, так как из блока 3 памяти будет считан код с нулем в соответствующем разряде. Очевидно, что сигнал на выходе первого 19, второго 20 и элемента И 21 появляется, если сигнал от объекта появился и является ожидаемЕЛм по условиям контроля,пришел в расчетный интервал времени между соответствующими тактовыми импульсами. Информация с выходов указанных элементов И фиксируется в регистре 12 блока селекции и через третий 22,четвертый 2 И К-ый 24 элемент И по сигналу Опрос со входа 24 блока 4 поступает на вход шифратора 5. Шифратор кодирует эту информацию и выдает внутрисистемную кодовую магистраль, соединенную с входом вычислительной машины.

Предлагаемое устройство обеспечивает постоянный автоматический контроль сигналов, вырабатываемых в системе, использует в своей работе сигналы, всегда существующие в магистрсшях, соединяющих приборы, что обеспечивает его использование в широком кругу цифровых систем, имеет простое подключение к объектам контроля, так

как использует сигналы с их разъемов, а не требует введение в объекты контроля специальных контрольных трактов, контролирует не только наличие или отсутствие сигналов, но интервал их выработки, что для ряда приборов является весьма актуальным.

Таким образом, изобретение расширяет функциональные возможности устройства, повышает надежность контроля, сокращает время поиска неисправ0ности, а следовательно, повышает коэффициент готовности системы в целом. Появляется возможность с помощью устройства контроля вести поиск потенциально ненадежных элементов, приво5дящих к задержкам в выработке сигналов.

Формула изобретения.

0

1. Устройство для контроля Цифровых систем, содержащее регистр сдвига блока вызова операции, первый выход которого соединен со входом блока памяти, отличающееся

5 тем, что, с целью повышения оперативности контроля, в устройство введен шифратор, блок селекции, первый управляющий вход которого соединен с первым выходом блока вызова операции,

0 второй вход которого соединен со вторым управляющим входом блока селекции, третий управляющий вход которого соединен с третьим выходом блока вызова операции, четвертый выход которого

5 соединен с информационным входом регистра сдвига, установочный вход которого соединен с первым входом блока вызова операции и является входом признака кода операции устройства, кодовый вход которого соединен со

0 вторым входом блока вызова операцииf третий вход которого является тактовым входом устройства, группа информационных входов которого соединена с первой группой информационных вхо5дов блока селекции, вторая группа информационных входов которого соединена с выходом блока памяти, выход регистра сдвига соединен с четвертым управляющим входом блока селекция,

0 группа выходов которого соединена со входами шифратора, выход которого является выходом устройства.

I...

2. Устройство по п. 1, о т л ич ающе е с я тем, что блок вызова

5 операции содержит дешифратор, элемент ИЛИ, регистр, линию задержки, элемент И, первый вход которого является первым входом блока, второй вход которого соединен со входом регистра,

0 выходы которого соединены со входами дешифратора, выход которого является первым выходом блока, второй вход которого соединен с первым выходом лиНИИ задержки, второй выход которой

5 является третьим выходом блока, чет

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых систем | 1983 |

|

SU1136166A2 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Асинхронное устройство управления | 1979 |

|

SU826351A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для отладки программ | 1985 |

|

SU1251087A1 |

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

| Устройство переадресации накопителя информации системы обработки данных | 1982 |

|

SU1072053A2 |

Авторы

Даты

1981-12-30—Публикация

1980-04-14—Подача