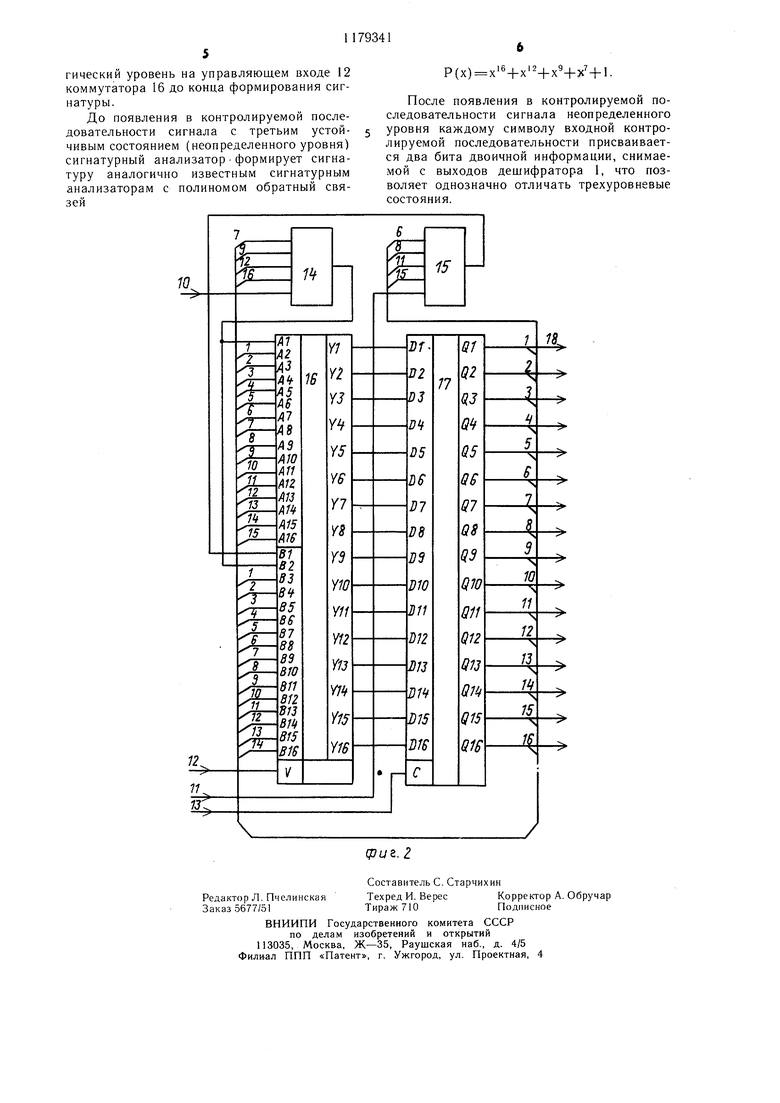

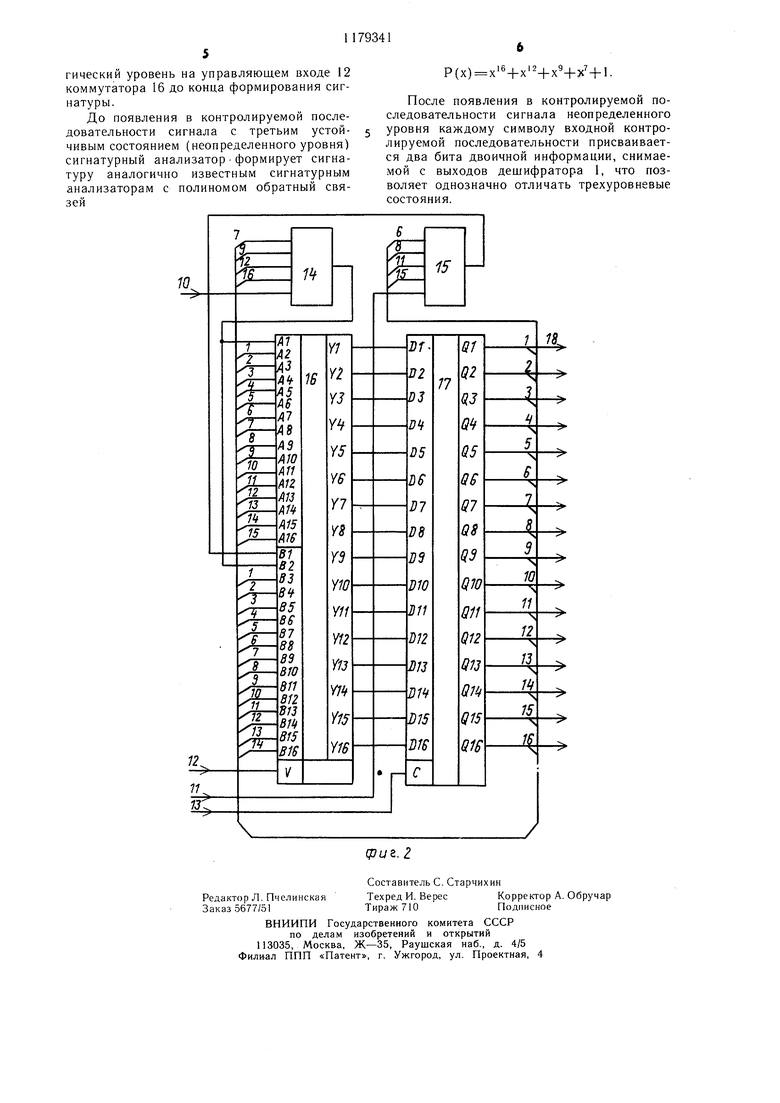

2. Анализатор по п. 1, отличающийся тем, что формирователь сигнатур содержит шестнадцатиразрядный регистр, шестнадцатиразрядный коммутатор и два сумматора по модулю два, причем выходы регистра являются выходами формирователя сигнатур К-и выход регистра (/(1,14) соединен с (/(+1)-м входом первой группы и ()-м входом второй группы информационных входов коммутатора, группа выходов которого соединена с группой информационных входов регистра, синхровход которого является синхровходом формирователя сигнатур, первый вход первой группы информационных входов коммутатора соединен с вторым входом второй группы информационных входов коммутатора и связан с выходом первого сумматора по модулю два, первые четыре входа первого и второго сумматоров по модулю два соединены с выходами соответственно седьмого, девятого, двенадцатого, шестнадцатого и шестого,восьмого, одиннадцатого и пятнадцатого разрядов регистра, пятые входы первого и второго сумматоров по модулю два являются соответственно первым и вторым информационными входами формирователя сигнатур, управляющий вход которого соединен с управляющим входом коммутатора, первый вход второй группы информационных входов которого соединен с выходом второго сумматора по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Сигнатурный анализатор | 1986 |

|

SU1361555A1 |

| Сигнатурный анализатор | 1982 |

|

SU1065857A1 |

| Сигнатурный анализатор | 1989 |

|

SU1624455A1 |

| Устройство для контроля электрических соединений | 1984 |

|

SU1265657A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1990 |

|

SU1748154A1 |

| Сигнатурный анализатор с перестраиваемой структурой | 1983 |

|

SU1120334A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

1. СИГНАТУРНЫЙ АНАЛИЗАТОР, содержащий шифратор, вход которого является информационным входом анализатора, триггер, формирователь сигнатур, выходы которого соединены с входами блока индикации, и элемент ИЛИ, отличающийся тем, что, с целью повышения быстродействия анализатора, в него введены эле8 мент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, первый вход которого соединен с первым входом элемента ИЛИ и выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены с соответствующими выходами шифратора и первым и вторым информационными входами формирователя сигнатур, синхровход которого соединен с вторым входом элемента И и является синхровходом анализатора, выход элемента И соединен с синхровходом триггера, информационный вход которого связан с шиной единичного потенциала, а выход подключен к второму входу элемента ИЛИ, выход которого соединен с управляющим входом формирователя сигнатур. i (Л ;о 00 1

1

Изобретение относится к автоматике, вычислительной и контрольно-измерительной технике и может быть использовано для контроля и диагностики цифровых устройств.

Цель изобретения - повышение быстродействия устройства.

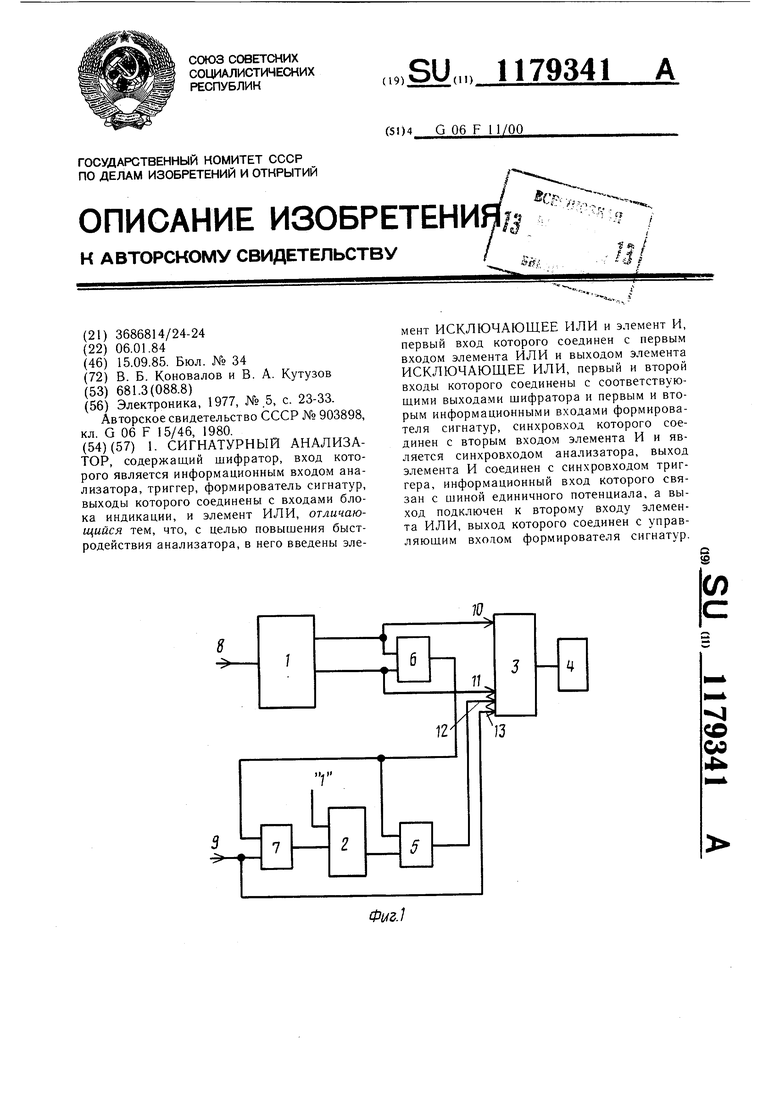

На фиг. 1 представлена структурная схема сигнатурного анализатора; на фиг. 2 - структурная схема формирователя сигнатур.

Сигнатурный анализатор содержит шифратор 1, триггер 2, формирователь 3 сигнатур, блок 4 индикации, элемент ИЛИ 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, элемент И 7, информационный вход 8 и синхровход 9. Формирователь 3 сигнатур содержит информационные входы 10 и 11, управляющий вход 12, синхровход 13, первый 14 и второй 15 сумматоры по модулю два, коммутатор 16 и регистр 17 с информационными выходами 18.

Анализатор работает следующим образом.

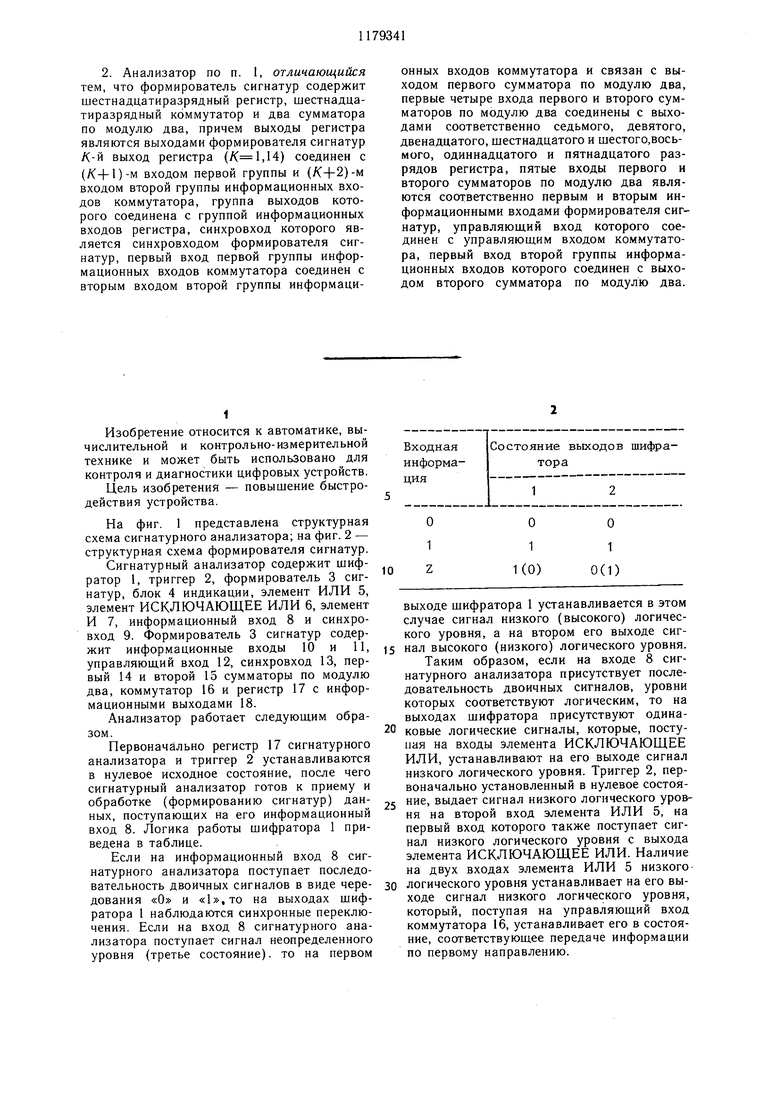

Первоначально регистр 17 сигнатурного анализатора и триггер 2 устанавливаются в нулевое исходное состояние, после чего сигнатурный анализатор готов к приему и обработке (формированию сигнатур) данных, поступающих на его информационный вход 8. Логика работы шифратора 1 приведена в таблице.

Если на информационный вход 8 сигнатурного анализатора поступает последовательность двоичных сигналов в виде чередования «О и «1,то на выходах шифратора 1 наблюдаются синхронные переключения. Если на вход 8 сигнатурного анализатора поступает сигнал неопределенного уровня (третье состояние), то на первом

выходе шифратора 1 устанавливается в этом случае сигнал низкого (высокого) логического уровня, а на втором его выходе сигнал высокого (низкого) логического уровня. Таким образом, если на входе 8 сигнатурного анализатора присутствует последовательность двоичных сигналов, уровни которых соответствуют логическим, то на выходах шифратора присутствуют одинаковые логические сигналы, которые, поступая на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, устанавливают на его выходе сигнал низкого логического уровня. Триггер 2, первоначально установленный в нулевое состояние, выдает сигнал низкого логического уровня на второй вход элемента ИЛИ 5, на первый вход которого также поступает сигнал низкого логического уровня с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Наличие на двух входах элемента ИЛИ 5 низкого логического уровня устанавливает на его выходе сигнал низкого логического уровня, который, поступая на управляющий вход коммутатора 16, устававлив-ает его в состояние, соответствующее передаче информации по первому направлению.

В этом случае на вход первого разряда регистра 17 поступает сигнал с выхода первого сумматора 14 по модулю два, на вход второго разряда - сигнал с выхода первого разряда регистра 17 и т. д.

Таким образом, при установке коммутатора 16 в состояние, соответствующее передаче информации по первому направлению, регистр 17 образует шестнадцатиразрядный сдвиговый регистр, на первый вход которого поступает сигнал с выхода первого сумматора 14 по модулю два. На входы сумматора 14 по модулю два поступают сигналы обратной связи, взятые с 16, 12, 9 и 7 разрядов образовавшегося регистра сдвига. На пятый вхо сумматора 14 по модулю два поступает сигнал с первого выхода шифратора I. Отсюда следует, что сигнатурный анализатор при поступлении на его вход импульсов синхронизации и при условии наличия в контролируемой последовательности сигналов только с определенными логическими уровнями, формирует сигнатуры (сжатые) контролируемой последовательности в соответствии с полиномом обратных связей

р(х)хЧх + .

Если в контролируемой последовательности данных зарегистрирован сигнал третьего состояния или неопределенного логического уровня, шифратор 1 формирует на своем первом выходе сигнал низкого (высокого) логического уровня, а на втором выходе - сигнал высокого (низкого) логического уровня. Эти выходные сигналы шифратора 1, поступая на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, устанавливают на его выходе сигнал высокого логического уровня. Сигнал высокого логического уровня с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 через элемент ИЛИ 5 поступает на управляющий вход 12 коммутатора 16, устанавливая его в состояние передачи информации по второму направлению. В этом случае сигнал с выхода первого сумматора 14 по модулю два поступает во второй разряд регистра 17, на вход первого разряда регистра 17 поступает сигнал с выхода второго сумматора 15 по модулю два, на вход третьего разряда поступает сигнал с выхода первого разряда регистра, на вход четвертого разряда регистра - сигнал с выхода второго разряда регистра и т. д., т. е. регистр 17 образует сдвиговый регистр со сдвигом на два разряда, причем на вход его второго разряда поступает сумма по модулю два сигналов обратной связи 16, 12, 9 и 7 разрядов регистра и входного сигнала с первого выхода шифратора, а на вход первого разряда образовавшегося регистра поступает сумма по модулю два сигналов обратной связи 15, 11, 8 и 6 разрядов регистра и входного сигнала с второго выхода шифратора 1.

Таким образом, сигнатурный анализатор при поступлении на его вход синхронизации импульсов синхронизации и при условии наличия в контролируемой последовательности сигнала с неопределенным уровнем напряжения осуществляет сдвиг в регистре сдвига сразу на два разряда, во второй разряд регистра записывается информация, снимаемая с первого выхода шифратора 1, просуммированная по модулю два с сигналами обратных связей, взятыми с 16, 12, 9 и 7 разрядов регистра сдвига, т. е. в соответствии с полиномом

Р(х) х +хЧхЧхЧ1,

а в первый разряд регистра 17 записывается информация, снимаемая с второго выхода шифратора 1, просуммированная по модулю два с сигналами обратных связей, взятыми с 15, 11, 8 и 6 разрядов регистра сдвига, т. е. в соответствии с полиномом

P(x) x -4-x --fx +x- + l.

Сдвиг в регистре сдвига на два разряда за один такт синхронизирующей последовательности импульсов и суммирование на сумматорах по модулю два с сигналами обратных связей двух последовательностей, снимаемых с выходов шифратора 1, эквивалентны такой обработке этих последовательностей, которую осуществлял бы регистр сдвига с обратными связями с 16, 12, 9 и 7 разрядов, взятыми через сумматор по модулю два при наличии двух импульсов синхронизации в каждом такте синхронизирующей последовательности, и при условии последовательного подключения (перед каждым импульсом синхронизации) пятого входа сумматора по модулю два первоначально к первому выходу шифратора 1, а затем к второму его выходу.

Таким образом, при обнаружении во входной контролируемой последовательности первого сигнала неопределенного уровня сигнатурный анализатор перестраивается на обработку двух последовательностей, снимаемых с выходов шифратора 1, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 устанавливается высокий уровень напряжения, который, поступая на первый вход элемента И 7, разрешает прохождение сигнала синхронизации на вход триггера 2, и при первом импульсе синхронизации уровень «1, поступающий на информационный вход триггера 2, устанавливает его в единичное состояние, в котором он сохраняется до конца формирования сигнатуры. Высокий логический уровень с выхода триггера 2 через элемент ИЛИ 5 поддерживает высокий логический уровень на управляющем входе 12 коммутатора 16 до конца формирования сигнатуры.

До появления в контролируемой последовательности сигнала с третьим устойчивым состоянием (неопределенного уровня) сигнатурный анализатор формирует сигнатуру аналогично известным сигнатурным анализаторам с полиномом обратный связей

p(x) x +xЧx +x +l.

После появления в контролируемой последовательности сигнала неопределенного уровня каждому символу входной контролируемой последовательности присваивается два бита двоичной информации, снимаемой с выходов дешифратора 1, что позволяет однозначно отличать трехуровневые состояния.

| Электроника, 1977, №.5, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-01-06—Подача