Изобретение относится к цифровой ычислительной технике и может быть спользовано при отладке программ пециализированных ЭВМ, содержащих своем составе штатные блоки памяти рабочими программами.

Цель изобретения - сокращение вреени отладки.

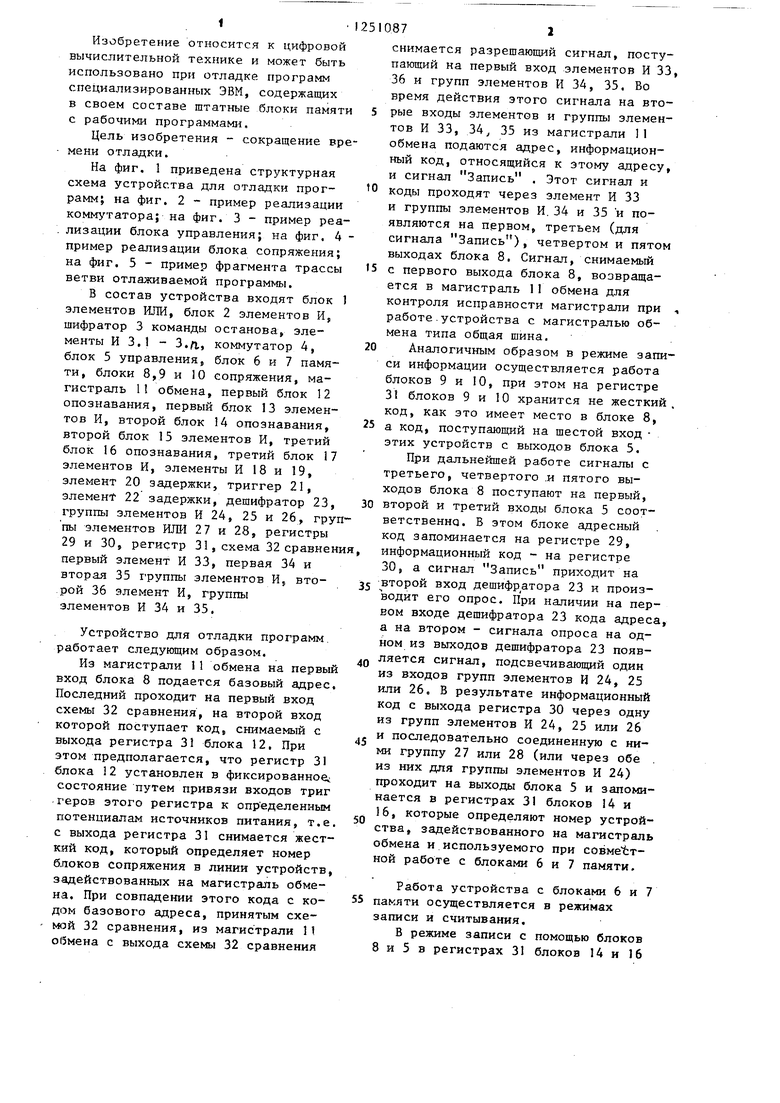

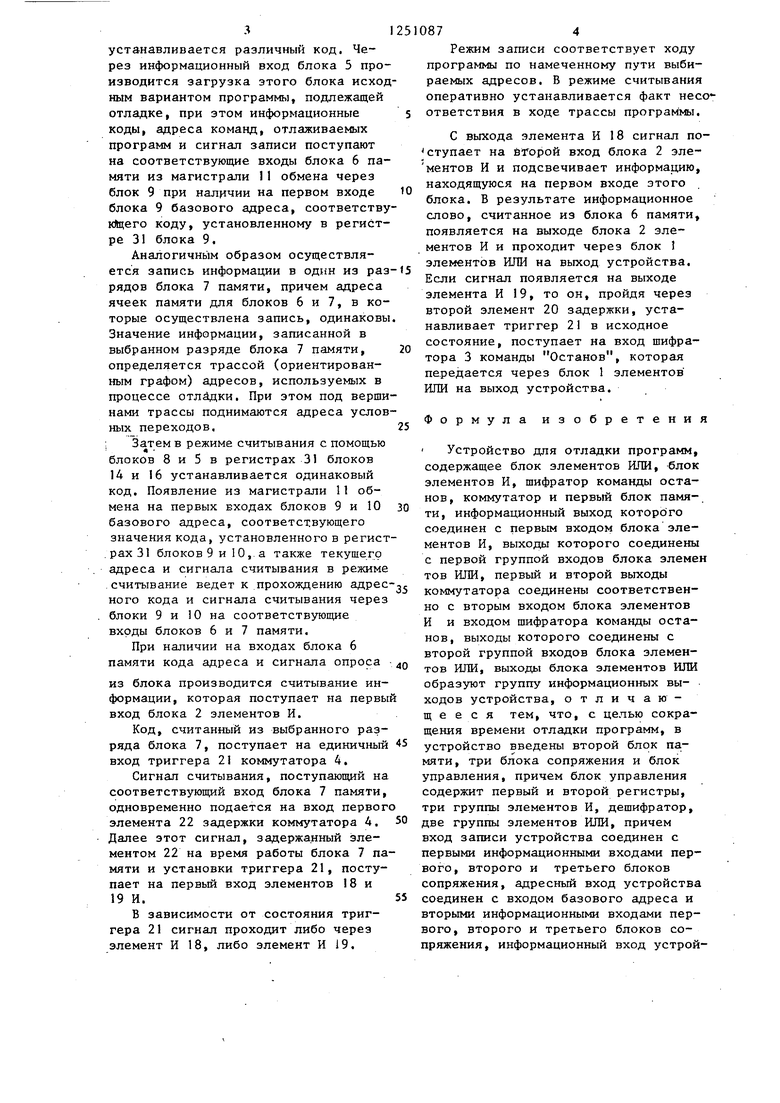

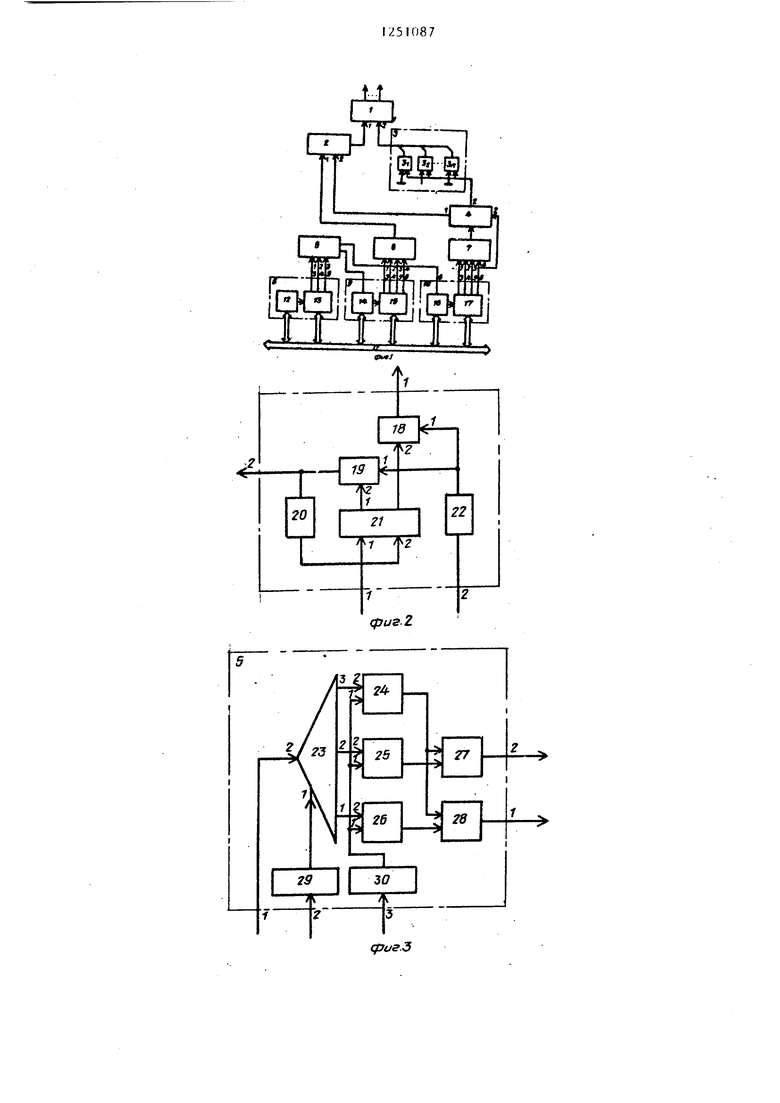

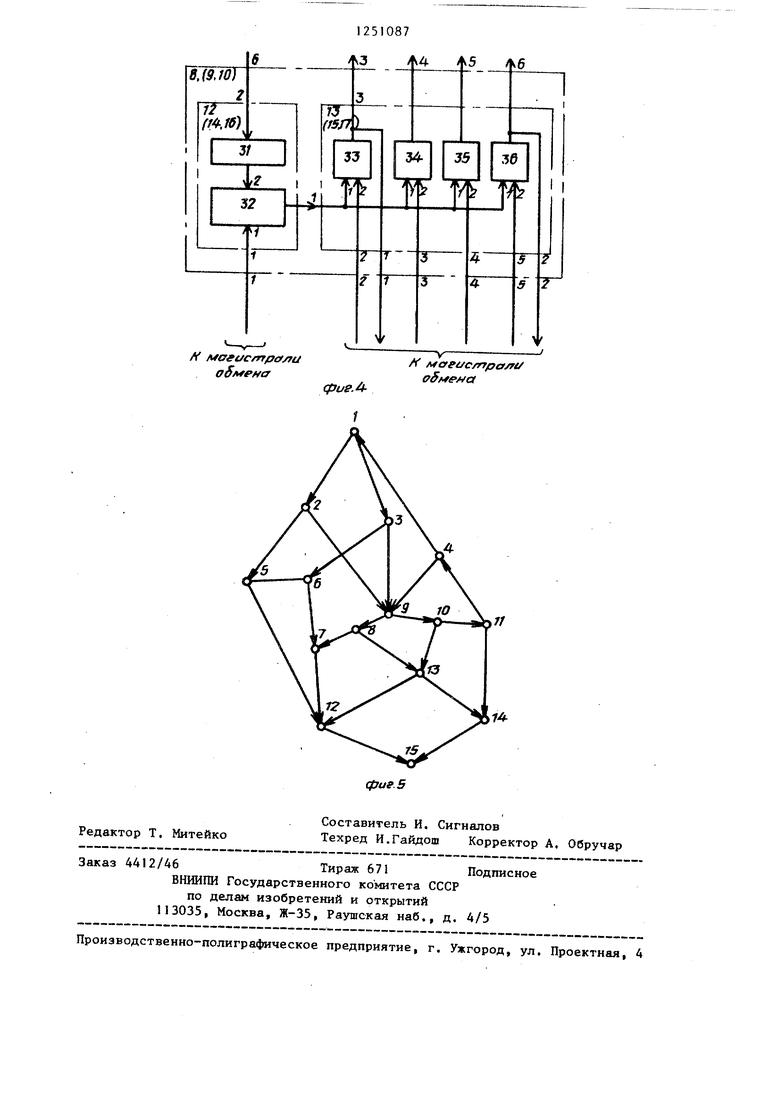

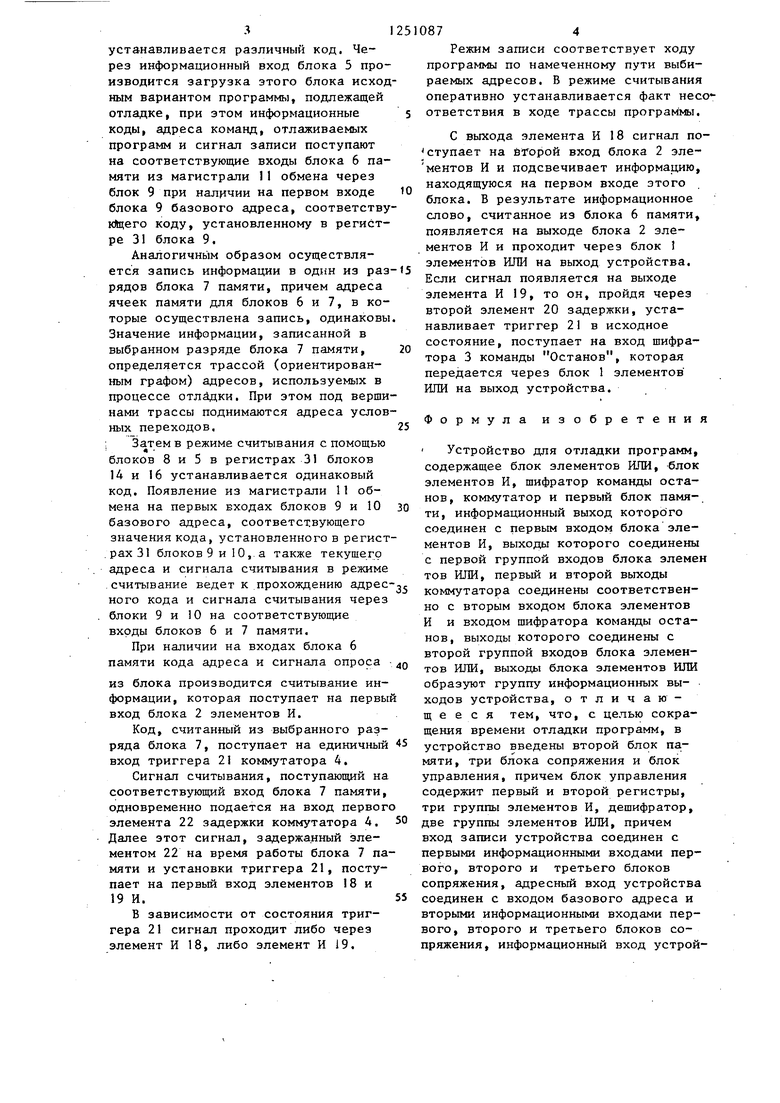

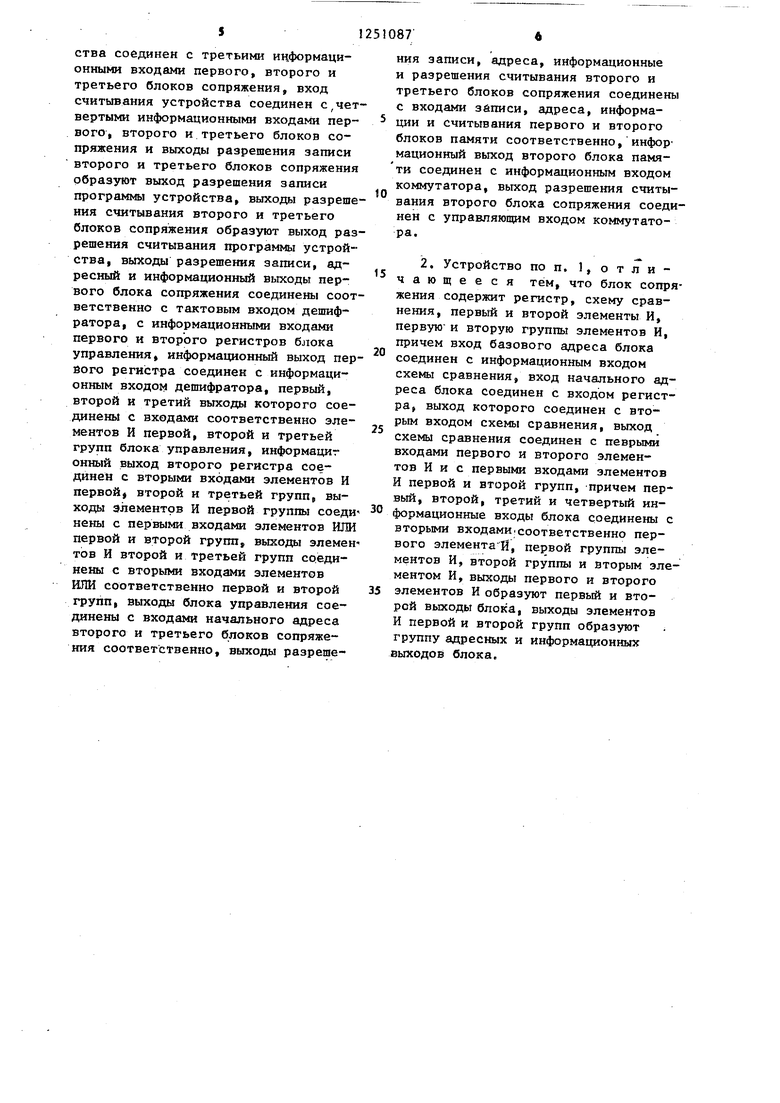

На фиг. 1 приведена структурная схема устройства для отладки прогамм; на фиг. 2 - пример реализации коммутатора; на фиг. 3 - пример реаизации блока управления; на фиг. 4 - пример реализации блока сопряжения; на фиг. 5 - пример фрагмента трассы ветви отлаживаемой программы.

В состав устройства входят блок J элементов ИЛИ, блок 2 элементов И, шифратор 3 команды останова, элементы И 3.1 - З.д, коммутатор 4, блок 5 управления, блок 6 и 7 памяти, блоки 8,9 и 10 сопряжения, магистраль 11 обмена, первый блок 12 опознавания, первый блок 13 элементов И, второй блок 14 опознавания, второй блок 15 элементов И, третий блок 16 опознавания, третий блок 17 элементов И, элементы И 18 и 19, элемент 20 задержки, триггер 21, элeмeнt 22 задержки, дешифратор 23, группы элементов И 24, 25 и 26, груп- пы элементов ИЛИ 27 и 28, регистры 29 и 30, регистр 31, схема 32 сравнения, первый элемент И 33, первая 34 и вторая 35 группы элементов И, второй 36 элемент И, группы элементов И 34 и 35.

Устройство для отладки программ. работает следующим образом.

Из магистрали 11 обмена на первый вход блока 8 подается базовый адрес. Последний проходит на первый вход схемы 32 сравнения, на второй вход которой поступает код, снимаемый с выхода регистра 31 блока 12, При этом предполагается, что регистр 31 блока 12 установлен в фиксированное состояние путем привязи входов триг геров этого регистра к опр еделенным потенциалам источников питания, т.е. с выхода регистра 31 снимается жесткий код, который определяет номер блоков сопряжения в линии устройств, задействованных на магистраль обмена. При совпадении этого кода с кодом базового адреса, принятым схе- мой 32 сравнения, из магистрали П обмена с выхода схемы 32 сравнения

,

to

20

25

510872

снимается разрешающий сигнал, поступающий на первый вход элементов И 33, 36 и групп элементов И 34, 35. Во время действия этого сигнала на вто5 рые входы элементов и группы элементов И 33, 34j 35 из магистрали 11 обмена подаются адрес, информационный код, относящийся к этому адресу, и сигнал Запись . Этот сигнал и коды проходят через элемент И 33 и группы элементов И.34 и 35 и появляются на первом, третьем (для сигнала Запись), четвертом и пятом выходах блока 8. Сигнал, снимаемый

t5 с первого выхода блока 8, возвращается в магистраль 11 обмена для контроля исправности магистрали при , работе.устройства с магистралью обмена типа общая шина.

Аналогичным образом в режиме записи информации осуществляется работа блоков 9 и 10, при этом на регистре 31 блоков 9 и 10 хранится не жесткий, код, как это имеет место в блоке 8, а код, поступающий на шестой вход этих устройств с выходов блока 5.

При дальнейшей работе сигналы с третьего, четвертого .и пятого выходов блока 8 поступают на первый, второй и третий входы блока 5 соответственна. В этом блоке адресный код запоминается на регистре 29, информационный код - на регистре 30, а сигнал Запись приходит на

второй вход дешифр атора 23 и производит его опрос. При наличии на первом входе дешифратора 23 кода адреса, а на втором - сигнала опроса на одном из выходов дешифратора 23 появ Q ляется сигнал, подсвечивающий один из входов групп элементов И 24, 25 или 26. В результате информационный код с выхода регистра 30 через одну из групп элементов И 24, 25 или 26 и последовательно соединенную с ними группу 27 или 28 (или через обе . из них для группы элементов И 24) проходит на выходы блока 5 и запоминается в регистрах 31 блоков 14 и 16, которые определяют номер устройства, задействованного на магистраль обмена и используемого при совме бт- ной работе с блоками 6 и 7 памяти.

30

45

50

Работа устройства с блоками 6 и 7 памяти осуществляется в режимах записи и считывания.

В режиме записи с помощью блоков 8 и 5 в регистрах 31 блоков 14 и 16

3

устанавливается различный код. Через информационный вход блока 5 производится загрузка этого блока исходным вариантом программы, подлежащей отладке, при этом информационные коды, адреса команд, отлаживаемых программ и сигнал записи поступают на соответствующие входы блока 6 памяти из магистрали 11 обмена через блок 9 при наличии на первом входе блока 9 базового адреса, соответству кКцего коду, установленному в регистре 31 блока 9,

Аналогичным образом осуществляется запись информации в одни из раз рядов блока 7 памяти, причем адреса ячеек памяти для блоков 6 и 7, в которые осуществлена запись, одинаковы Значение информации, записанной в выбранном разряде блока 7 памяти, определяется трассой (ориентированным графом) адресов, используемых в процессе отладки. При этом под вершинами трассы поднимаются адреса условных переходов, ; атем в режиме считывания с помощью блоков 8 и 5 в регистрах 31 блоков 14 и 16 устанавливается одинаковый код. Появление из магистрали 11 обмена на первых входах блоков 9 и 10 базового адреса, соответствующего значения кода, установленного в регист .pax 31 блоков 9 и 10, а также текущего адреса и сигнала считывания в режиме считывание ведет к прохождению адрес ного кода и сигнала считывания через блоки 9 и 10 на соответствующие входы блоков 6 и 7 памяти.

При наличии на входах блока 6 памяти кода адреса и сигнала опроса

из блока производится считывание информации, которая поступает на первы вход блока 2 элементов И.

Код, считанный из выбранного разряда блока 7, поступает на единичный вход триггера 21 коммутатора 4.

Сигнал считывания, поступающий на соответствующий вход блока 7 памяти, одновременно подается на вход первого элемента 22 задержки коммутатора 4. Далее этот сигнал, задержанный :эле- ментом 22 на время работы блока 7 памяти и установки триггера 21, поступает на первый вход элементов 18 и 19 И.

В зависимости от состояния триггера 21 сигнал проходит либо через элемент И 18, либо элемент И 19.

874

Режим записи соответствует ходу программы по намеченному пути выбираемых адресов. В режиме считывания оперативно устанавливается факт несоответствия в ходе трассы программы.

С выхода элемента И 18 сигнал по- ступает на йГорой вход блока 2 эле- ментов И и подсвечивает информацию, находящуюся на первом входе этого блока. В результате информационное слово, считанное из блока 6 памяти, появляется на выходе блока 2 элементов И и проходит через блок 1 элементов ИЛИ на выход устройства. Если сигнал появляется на выходе элемента И 19, то он, пройдя через второй элемент 20 задержки, устанавливает триггер 21 в исходное состояние, поступает на вход шифратора 3 команды Останов, которая передается через блок 1 элементов ИЛИ на выход устройства.

Формула изобретения

Устройство для отладки программ, содержащее блок элементов ИЛИ, блок элементов И, шифратор команды останов, коммутатор и первый блок памяти, информационный выход которого соединен с первым входом блока элементов И, выходы которого соединены с первой группой входов блока элемен тов ИЛИ, первый и второй выходы коммутатора соединены соответственно с вторым входом блока элементов И и входом шифратора команды останов, выходы которого соединены с второй группой входов блока элементов ИЛИ, выходы блока элементов ИЛИ образуют группу информационных выходов устройства, отличающееся тем, что, с целью сокращения времени отладки программ, в устройство введены второй блок памяти, три блока сопряжения и блок управления, причем блок управления содержит первый и второй регистры, три группы элементов И, дешифратор, ве группы элементов ИЛИ, причем вход записи устройства соединен с ервыми информационными входами перого, второго и третьего блоков опряжения, адресный вход устройства оединен с входом базового адреса и торыми информационными входами перого, второго и третьего блоков соряжения, информационный вход устройства соединен с третьими информационными входами первого, второго и третьего блоков сопряжения, вход считывания устройства соединен с,четвертыми информационными входами первого, второго и третьего блоков сопряжения и выходы разрешения записи второго и третьего блоков сопряжения образуют выход разрешения записи программы устройства, выходы разрешения считывания второго и третьего блоков сопряжения образуют выход разрешения считывания программы устройства, выходы разрешения записи, адресный и информационный выходы первого блока сопряжения соединены соответственно с тактовым входом дешифратора, с информационными входами первого и второго регистров блока управления, информационный выход первого регистра соединен с информационным ВХОД014 дешифратора, первый, второй и третий выходы которого соединены с входами соответственно элементов И первой, второй и третьей групп блока управления, информациг онный выход второго регистра соединен с вторыми входами элементов И первой второй и третьей групп, выходы элементов И первой группы соеди нены с первыми входами элементов ИЛИ первой и второй групп, выходы элемен тов И второй и третьей групп соединены с вторыми входами элементов ИЛИ соответственно первой и второй групп, выходы блока управления соединены с входами начального адреса второго и третьего блоков сопряжения соответственно, выходы разрешения записи, адреса, информационные и разрешения считывания второго и третьего блоков сопряжения соединены с входами записи, адреса, информа- ции и считывания первого и второго блоков памяти соответственно, информационный выход второго блока памя- ти соединен с информационным входом коммутатора, выход разрешения считывания второго блока сопряжения соединен с управляющим входом коммутатора.

2. Устройство по п. 1, о т л и - чающееся тем, что блок сопряжения содержит регистр, схему сравнения, первый и второй элементы И, первую и вторую группы элементов И, причем вход базового адреса блока соединен с информационным входом схемы сравнения, вход начального адреса блока соединен с входом регистра, выход которого соединен с вторым входом схемы сравнения, выход схемы сравнения соединен с певрыми входами первого и второго элементов И и с первыми входами элементов И первой и второй групп, причем первый, второй, третий и четвертый информационные входы блока соединены с вторыми входами Соответственно первого элемента И, первой группы элементов И, второй группы и вторым элементом И, выходы первого и второго

элементов И образуют первый и второй выходы блока, выходы элементов И первой и второй групп образуют группу адресных и информационных выходов блока.

rjrrr--

S

hi

,1 |i f S i-J

, I r

fmjfflf

Гя I i П-Ы М i

Щ1Игй1ЩЩ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1984 |

|

SU1238086A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1348841A1 |

| Устройство для отладки программ | 1988 |

|

SU1661771A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

30

(ре/г.З

Редактор Т, Митейко

Составитель И, Сигналов

Техред И.Гайдош Корректор А. Обручар

Заказ 4412/46Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фае 5

| Авторское свидетельство СССР № 754419, кп | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1983 |

|

SU1137472A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-02—Подача