12

Изобретение относится к вычислительной технике и может быть использовано для хранения слов переменной длины.

Цель изобретения - упрощение устройства.

Информация о разрядности слов кодируется в дополнительных разрядах ячейки памяти накопителя. Пусть К - Максимальное число байтов, которое может быть размещено в ячейке памяти Будем располагать в ней слова длиной Xj байтов (jlix,). Число способов которыми можно расположить в ячейке памяти накопителя слова данного набора, равно числу способов, которыми можно представить натуральное число К в виде суммы натуральных чисел. Введем в ячейку памяти 1 дополнительных разрядов, в которых зако- дируется номер комбинации групп слов в ячейке. Если на расположение слов наложить такое ограничение, чтобы в одной ячейке слова меньшей разрядности располагались всегда правее слов большей разрядности, то номер комбинации Z, записанный в дополнительных разрядах, в совокупности с адресом младшего байта выбираемого (записываемого) слова однозначно определяет разрядность слова.

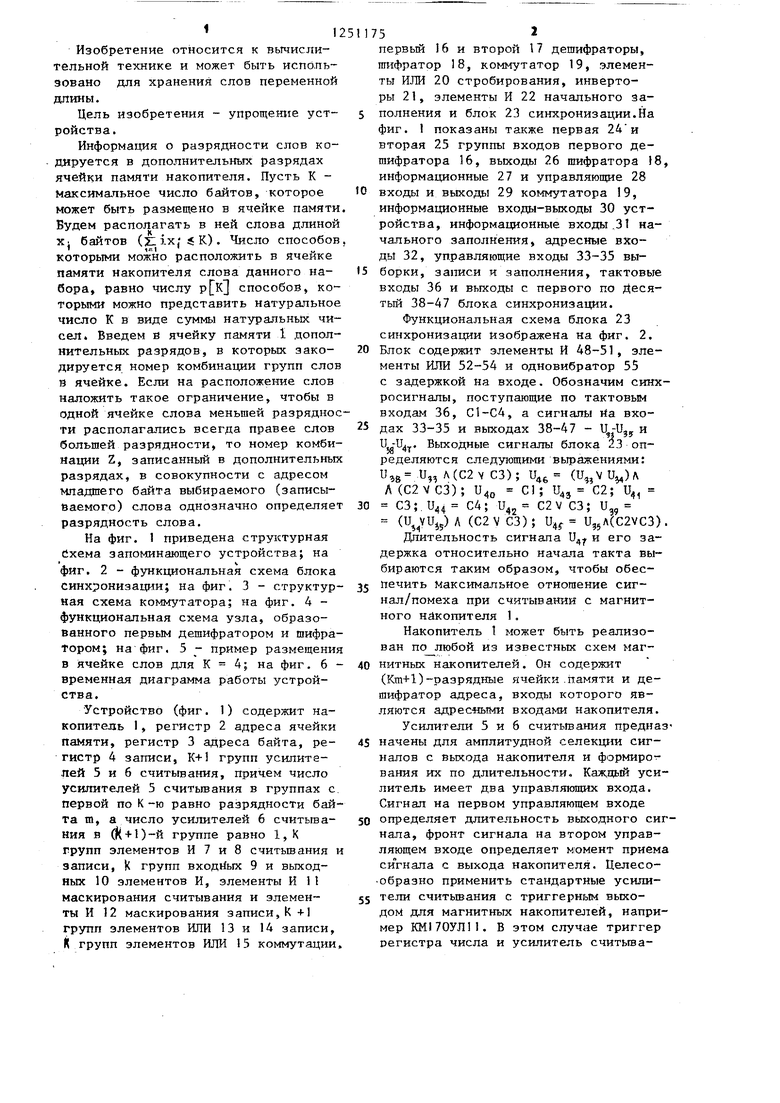

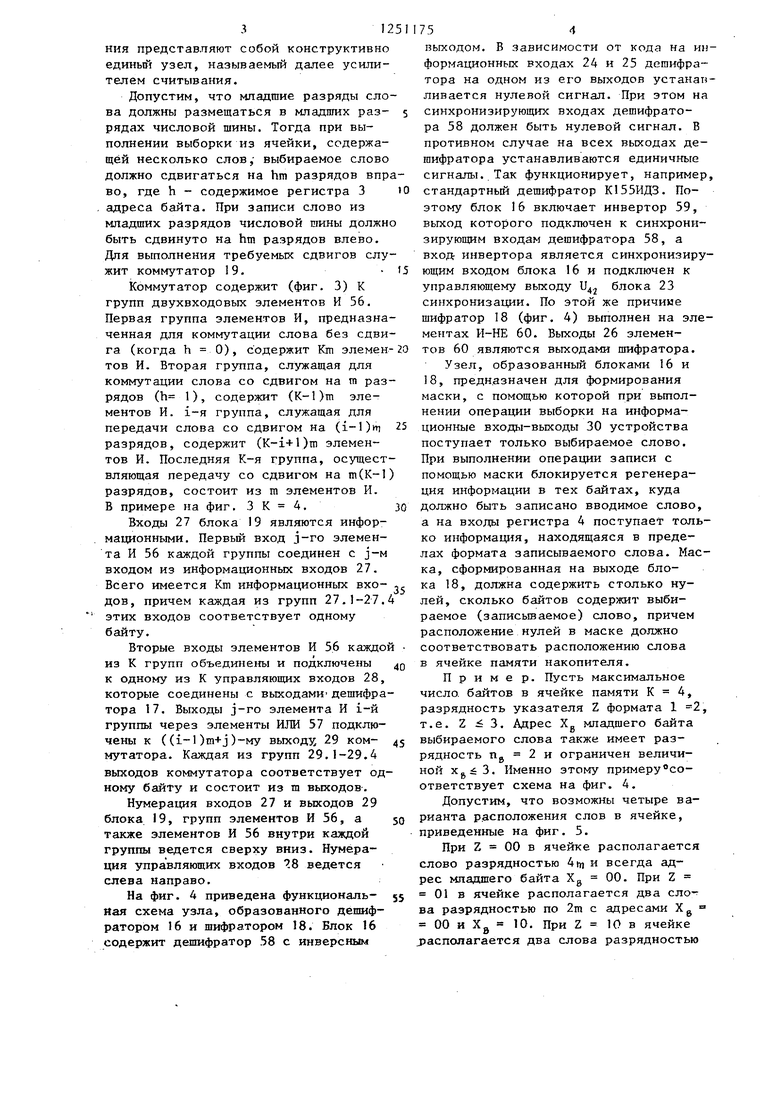

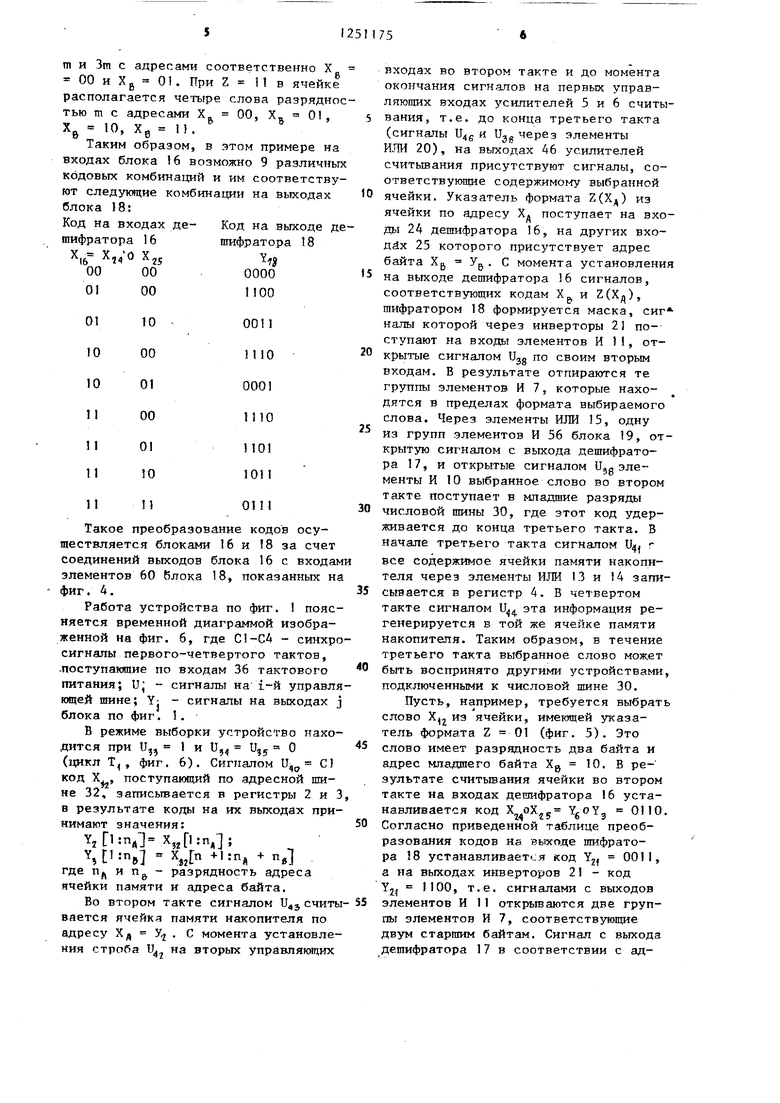

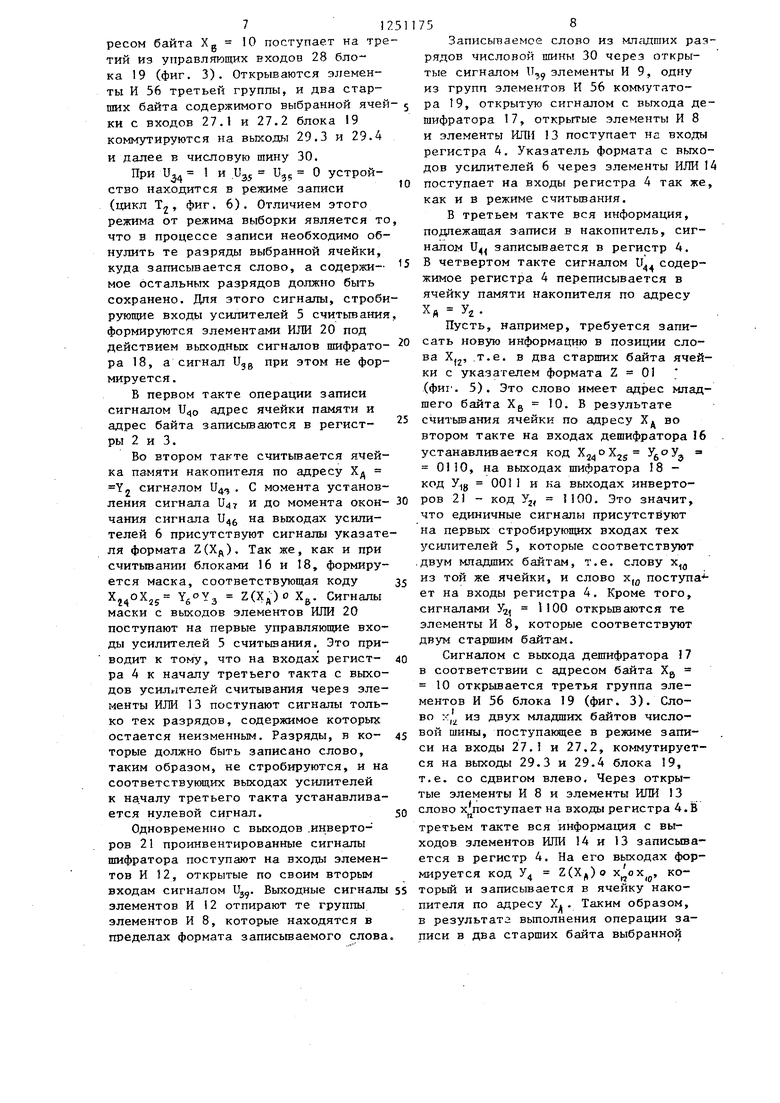

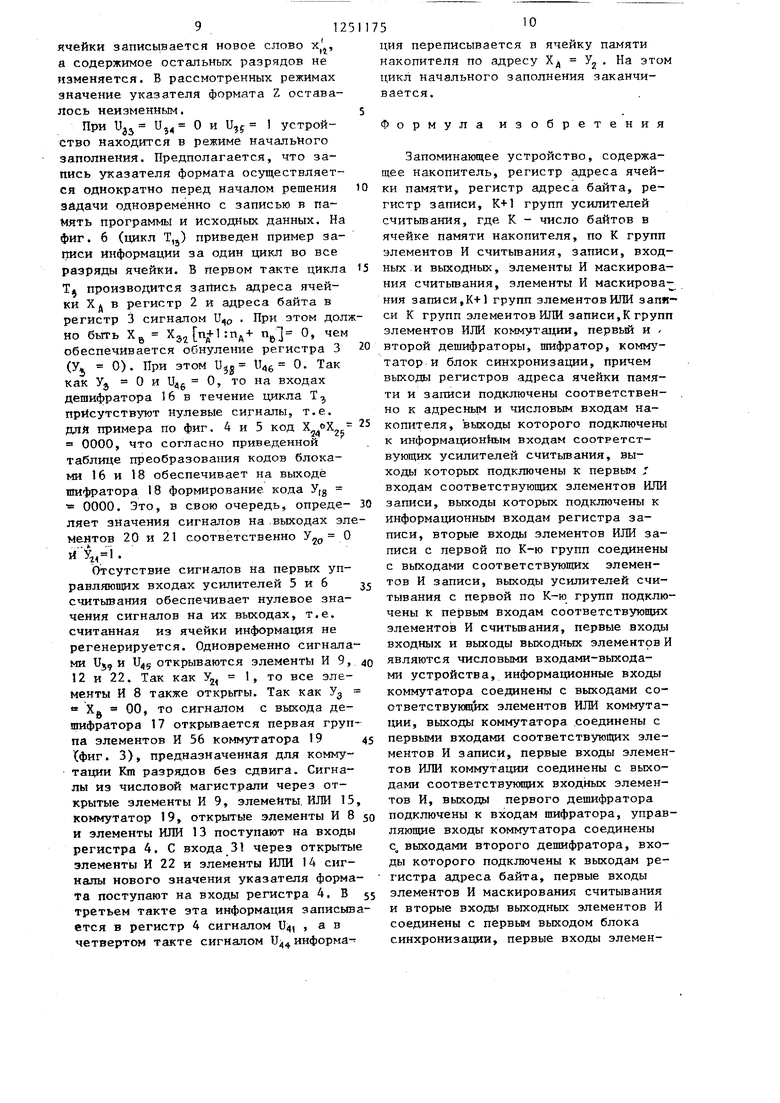

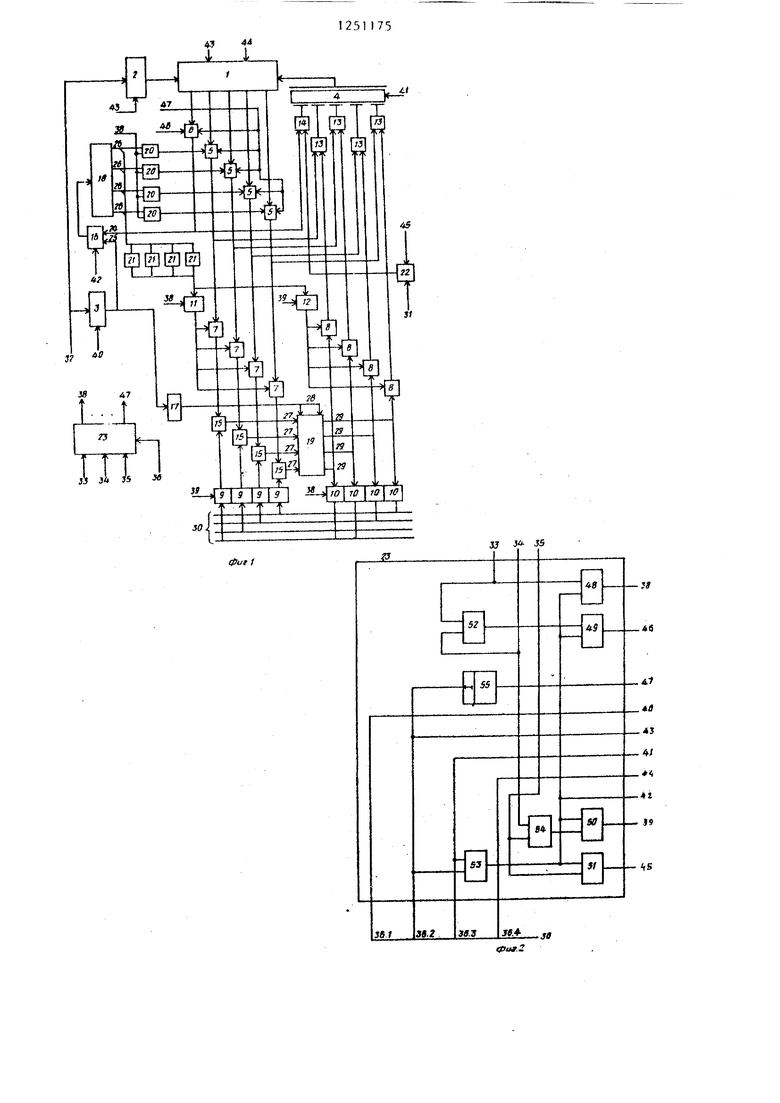

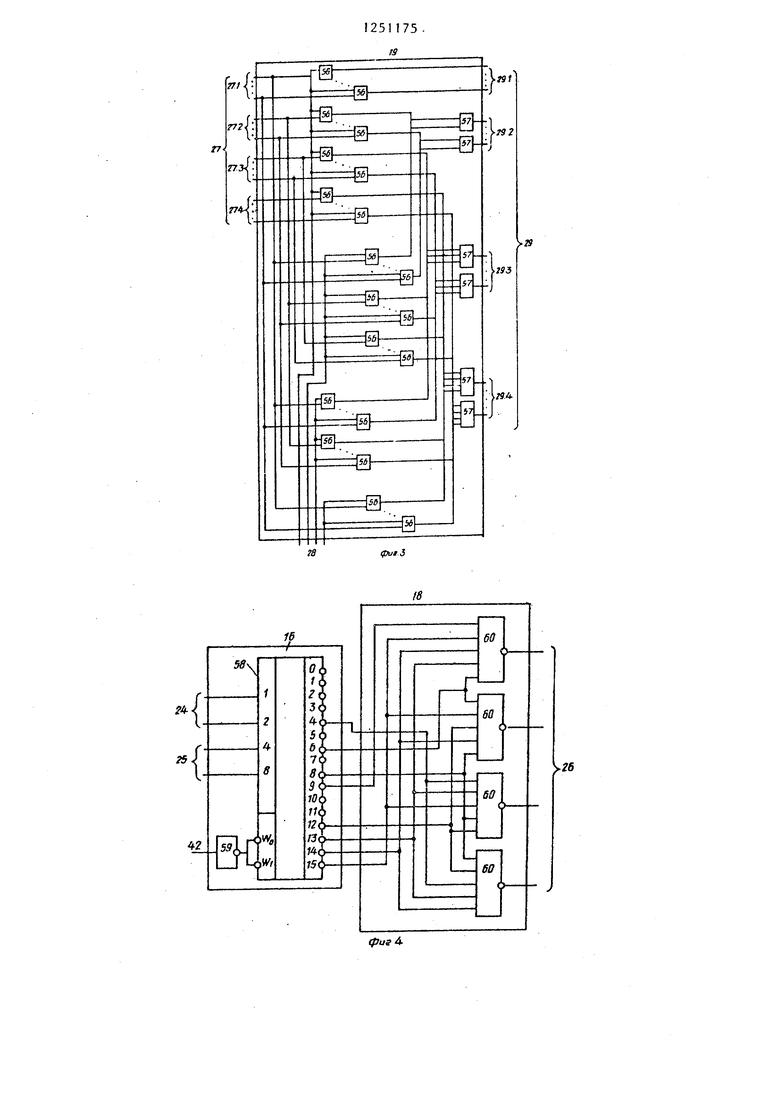

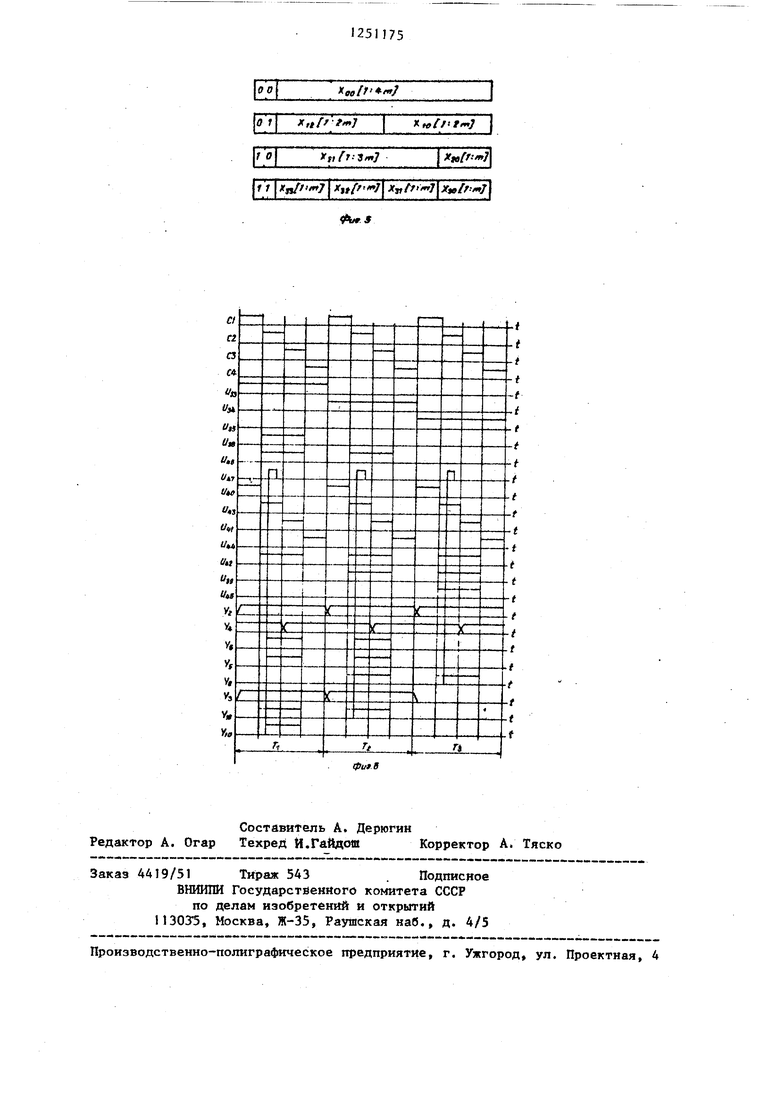

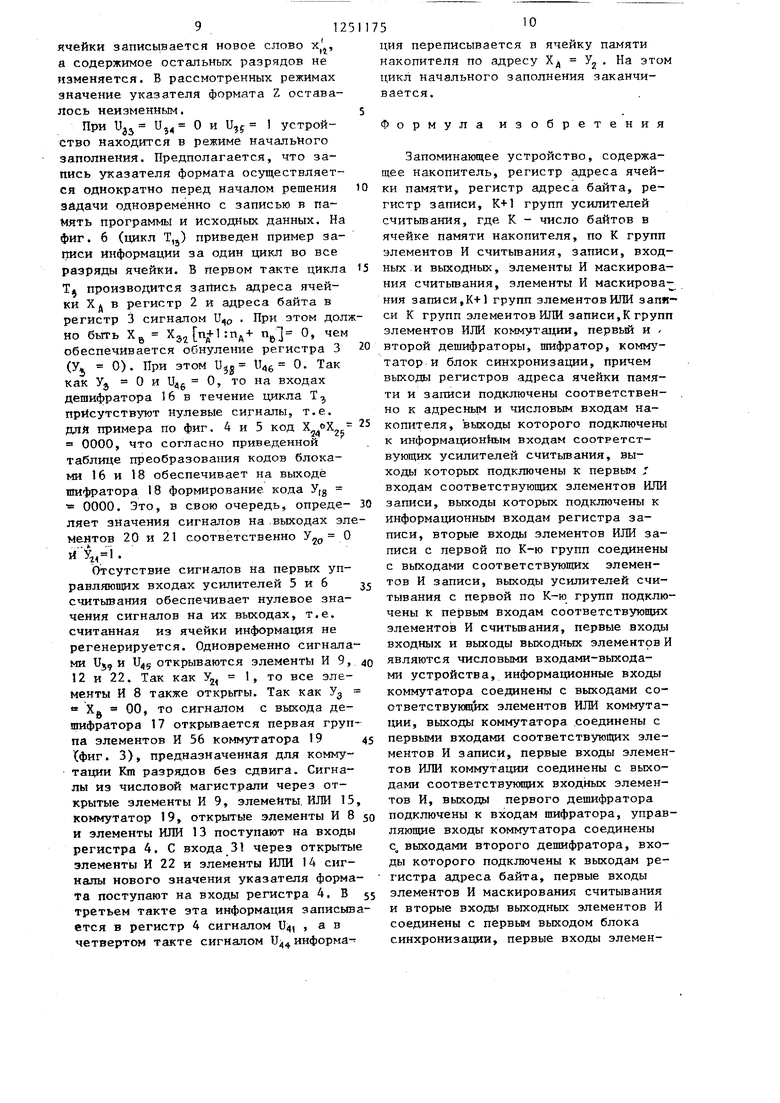

На фиг. 1 приведена структурная Схема запоминающего устройства; на фиг. 2 - функциональная схема блока синхронизации; на фиг. 3 - структурная схема коммутатора; на фиг. 4 - функциональная схема узла, образованного первым дешифратором и шифратором; на фиг, 5 - пример размещения в ячейке слов для К 4; на фиг. 6 - временная диаграмма работы устройства.

Устройство (фиг. 1) содержит накопитель I, регистр 2 адреса ячейки памяти, регистр 3 адреса байта, регистр 4 записи, K-fi групп усилителей 5 и 6 считывания, причем число усилителей 5 считьшания в группах с. первой по К-ю равно разрядности байта тп, а число усилителей 6 считывания в + 1)-й группе равно 1, К групп элементов И 7 и 8 считьшания и записи, k групп входных 9 и выходных 10 элементов И, элементы И 11 маскирования считывания и элементы И 12 маскирования записи,К +1 групп элементов ИЛИ 13 и 14 записи, Р групп элементов ИЛИ 15 коммутации.

52

первый 16 и второй 17 дешифраторы, шифратор 18, коммутатор 19, элементы ИЛИ 20 стробирования, инверторы 21, элементы И 22 начального заполнения и блок 23 синхронизации.На фиг. 1 показаны также первая 24 и вторая 25 группы входов первого дешифратора 16, выходы 26 шифратора 18, информационные 27 и управляюш е 28

входы и выходы 29 коммутатора 19, информационные входы-выходы 30 устройства, информационные входы ,3t начального заполнения, адресные входы 32, управляющие входы 33-35 выборки, записи и заполнения, тактовые входы 36 и выходы с первого по Десятый 38-47 блока синхронизации.

Функциональная схема блока 23 cшixpoнизaции Изображена на фиг. 2.

Блок содержит элементы И 48-51, элементы ИЛИ 52-54 и одновибратор 55 с задержкой на входе. Обозначим синхросигналы, поступающие по тактовым входам 36, С1-С4, а сигналы rta вхо

дах 33-35 и выходах 38-47 - U и и -Ц(. Выходные сигналы блока 23 определяются следующими выражениями: U,g и„ Л(С2у СЗ); (U,,VU)A Л (C2VC3); С1; С2; U, СЗ;. U44 С4 ; U С2 V СЗ; U,,

() Л (C2VC3); U,5A(C2VC3). Дпительность сигнала U и его задержка относительно начала такта выбираются таким образом, чтобы обес- печить Максимальное отношение сигнал/помеха при считывании с магнитного накопителя 1.

Накопитель 1 может быть реализован по любой из известных схем маг- нитных накопителей. Он содержит

(Кт+1)-разрядные ячейки .памяти и дешифратор адреса, входы которого являются адрес«ыми входами накопителя.

Усилители 5 и 6 считывания предназ- начены для амплитудной селекции сигналов с выхода накопителя и формиро- вания их по длительности. Каж,Е(ый усилитель имеет два управляющих входа. Сигнал на первом управляющем входе определяет длительность вькодного сигнала, фронт сигнала на втором управляющем входе определяет момент приема сиЪнала с выхода накопителя. Целесо- образно применить стандартные усили- тели считьюания с триггерным выходом для магнитных накопителей, например КМ170УЛ11. В этом случае триггер регистра числа и усилитель считыва3125

ния представляют собой конструктивно единьп1 узел, называемый далее усилителем считывания.

Допустим, что младшие разряды слова должны размещаться в младших раз- 5 рядах числовой шины. Тогда при выполнении выборки из ячейки, содержащей несколько слов, выбираемое слово должно сдвигаться на hm разрядов вправо, где h - содержимое регистра 3 0 , адреса байта. При записи слово из младших разрядов числовой шины должно быть сдвинуто на htn разрядов влево. Для выполнения требуемых сдвигов служит коммутатор 19.-15

Коммутатор содержит (фиг. 3) К групп двухвходовых злементов И 56, Первая группа элементов И, предназначенная для коммутации слова без сдвига (когда h 0), содержит Km элемен-20 тов И. Вторая группа, служащая для коммутации слова со сдвигом на m разрядов (h 1), содержит (K-l)m элементов И. i-я группа, служащая для передачи слова со сдвигом на (i-l)i 23 разрядов, содержит (K-i+l)m элементов И. Последняя К-я группа, осуществляющая передачу со сдвигом на m(K-l) разрядов, состоит из m элементов И. В примере на фиг. 3 К 4,зо

Входы 27 блока 19 являются информационными. Первый вход j-ro элемента И 56 каждой группы соединен с j-м входом из информационных входов 27. Всего имеется Km информационных вхо- ,, дов, причем каждая из групп 27.1-27.4 этих входов соответствует одному байту.

Вторые входы элементов И 56 каждой из К групп объединены и подключены о к одному из К управляющих входов 28, которые соединены с выходами- дешифратора 17. Выходы j-ro элемента И i-й группы через элементы ИШ 57 подключены к ((L-I)m+j)-му выходх 29 ком- 45 мутатора. Каждая из групп 29.1-29.4 выходов коммутатора соответствует одному байту и состоит из m выходов.

Нумерация входов 27 и выходов 29 блока 19, групп элементов И 56, а 50 также элементов И 56 внутри каждой группы ведется сверху вниз. Нумерация управляющих входов 8 ведется слева Направо.

На фиг. 4 приведена функциональ- 55 Мая схема узла, образованного дешифратором 16 и шифратором 18. Блок 16 содержит дешифратор 58 с инверсным

754

выходом, в Зависимости от кода на иформационных входах 24 и 25 дешифратора на одном из его выходов устаналивается нулевой сигнал. При этом н синхронизирующих входах дешифратора 58 должен быть нулевой сигнал. В противном случае на всех выходах дешифратора устанавливаются единичные сигналы. Так функционирует, например стандартный дешифратор К155ИДЗ. Поэтому блок 16 включает инвертор 59, выход которого подключен к синхрони- зируюшим входам дешифратора 58, а вход инвертора является синхронизирующим входом блока 16 и подключен к управляющему выходу U,, блока 23 синхронизации. По этой же причине шифратор 18 (фиг. 4) выполнен на элементах И-НЕ 60. Выходы 26 злементов 60 являются выходами шифратора. Узел, образованный блоками 16 и 18, предназначен для формирования маски, с помощью которой при выполнении операции выборки на информационные входы-выходы 30 устройства поступает только выбираемое слово. При выполнении операции записи с помощью маски блокируется регенерация информации в тех байтах, куда должно быть записано вводимое слово, а на входы регистра 4 поступает только информация, находящаяся в пределах формата записываемого слова. Маска, сформированная на выходе блока 18, должна содержить столько нулей, сколько байтов содержит выбираемое (записываемое) слово, причем расположение нулей в маске должно соответствовать расположению слова в ячейке памяти накопителя.

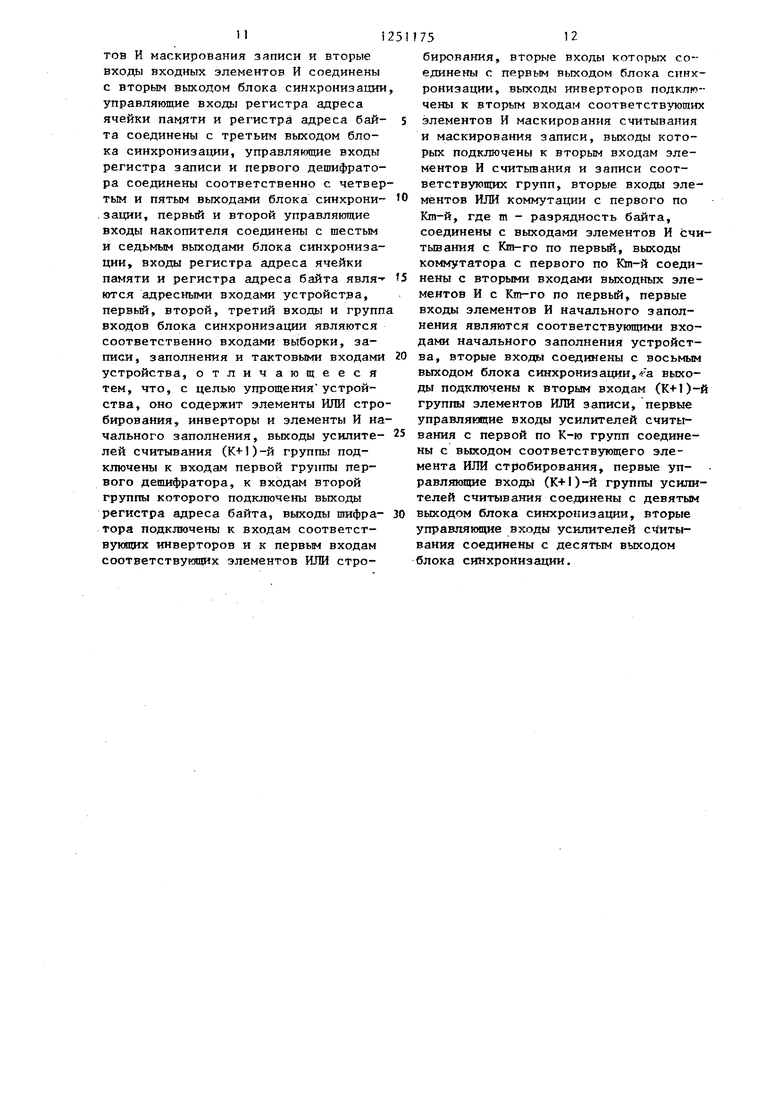

Пример. Пусть максимальное число, байтов в ячейке памяти К 4, разрядность указателя Z формата 1 2 т.е. Z i 3. Адрес Xg мпадшего байта выбираемого слова также имеет разрядность Пц 2 и ограничен величиной Xgi3. Именно этому примеру соответствует схема на фиг, 4.

Допустим, что возможны четыре варианта расположения слов в ячейке, приведенные на фиг. 5.

При Z 00 в ячейке располагается слово разрядностью 4irj и всегда адрес младшего байта Х 00. При Z 01 в ячейке располагается два сло-г ва разрядностью по 2т с адресами Xg 00 и Xg 10. При Z 10 в ячейке JЭacпoлaгaeтcя два слова разрядностью

m и 3m с адресами соответственно X 00 и Xg 01. При Z 1 1 в ячейке располагается четыре слова разрядностью m с адресами X 00, X - 01, 10, Хд П.

Таким образом, в этом примере на входах блока 16 возможно 9 различных кодовых комбинаций и им соответствуют следующие комбинации на выходах блока 18:

Код на входах де- Код на выходе дешифратора 16 шифратора 18

X

0000 1 100

и

ООП 1 10 000 1110

П01 1011

01 М

Такое преобразование кодов осуществляется блоками 16 и 8 за счет соединений выходов блока 16 с входами элементов 60 блока 18, показанных на фиг. 4.

Работа устройства по фиг. поясняется временной диаграммой изображенной на фиг. 6, где С1-С4 - синхросигналы первого-четвертого тактов, -поступающие по входам 36 тактового питания; Uj - сигналы на i-й управляющей шине; Y- - сигналы на выходах j блока по фиг. 5.

В режиме выборки устройство нахо

дится при Uj, 1 и и, и,5 О (цикл Т., фиг. 6). Сигналом Uu С1

код X., поступающий по адресной шине 32, записывается в регистры 2 и 3, в результате коды на их выходах принимают значения:

Y7ri:nJ X,Jl:nJ;

Y, 5fJ fll где Пд и п - разрядность адреса

ячейки памяти и адреса байта.

Во втором такте сигналом считы- вается ячейка памяти накопителя по адресу Хд У . С момента установления строба Ц|, на вторых управляющих

входах во втором такте и до момента окончания сигнапов на первых управляющих входах усилителей 5 и 6 считывания, т.е. до конца третьего такта (сигналы U4g и Ugg через элементы ИЖ 20), на выходах 46 усилителей считьгоания присутствуют сигналы, соответствующие содержимому выбранной ячейки. Указатель формата Z(X) из ячейки по адресу X поступает на входы 24 дешифратора 16, на других вхо- дйх 25 которого присутствует адрес

байта X

В

Ур. С момента установления

на выходе дешифратора 16 сигналов, соответствующих кодам X и Z(X), шифратором 18 формируется маска, сиг налы которой через инверторы 21 поступают на входы элементов И 1I, открытые сигналом Ujg по своим вторым входам. В результате отпираются те группы элементов И 7, которые находятся в пределах формата выбираемого слова. Через элементы ИЛИ 15, одну из групп элементов И 56 блока 19, открытую сигналом с выхода дешифратора 17, и открытые сигналом U,g элементы И 10 выбранное слово во втором такте поступает в младшие разряды числовой щины 30, где этот код удерживается до конца третьего такта. В начале третьего такта сигналом U все содержимое ячейки памяти накопителя через элементы ИЛИ 3 и 14 записывается в регистр 4. В четвертом такте сигналом U эта информация регенерируется в той же ячейке памяти накопителя. Таким образом, в течение третьего такта выбранное слово может быть воспринято другими устройствами, подключенными к числовой шине 30.

Пусть, например, требуется выбрать слово Х,2 из ячейки, имеющей указатель формата Z 01 (фиг. 5). Это слово имеет разрядность два байта и адрес младшего байта Xg 10. В результате считьгоания ячейки во втором такте иа входах дешифратора 16 устанавливается код X YgOYg ОНО. Согласно приведенной таблице преобразования кодов на выходе шифратора 18 устанавливает :. код Y, 0011, а на выходах инверторов 21 - код YJ., 1100, т.е. сигналами с выходов элементов И 11 открьтаются две группы элементов И 7, соответствующие двум старшим байтам. Сигнал с выхода дешифратора 17 в соответствии с ад

71

ресом байта Xg 10 поступает на третий из управляющих входов 28 блока 19 (фиг. 3). Открываются элементы И 56 третьей группы, и два старших байта содержимого выбранной ячей ки с входов 27.1 и 27.2 блока 19 коммутируются на вькоды 29.3 и 29.4 и далее в числовую тину 30.

При 1 и Ь зз и,,; О устройство находится в режиме записи (цикл Т2, фиг. 6). Отличием этого режима от режима выборки является то что в процессе записи необходимо обнулить те разряды выбранной ячейки, куда записывается слово, а содержи- мое остальных разрядов должно быть сохранено. Дпя этого сигналы, строби рующие входы усилителей 5 считывания формируются элементами ИЛИ 20 под действием выходных сигналов шифрато- ра 18, а сигнал при этом не формируется .

В первом такте операции записи сигналом адрес ячейки памяти и адрес байта записьшаются в регист- ры 2 и 3.

Во втором такте считьюается ячейка памяти накопителя по адресу Хд Y2 сигналом 114., . С момента установления сигнала и до момента окон- чания сигнала U на выходах усилителей 6 присутствуют сигналы указателя формата Z(X). Так же, как и при считьгоании блоками 16 и 18, формируется маска, соответствующая коду ,,5 YgOYa г(Хд)о Х. Сигналы маски с выходов элементов ИЛИ 20 поступают на первые управляющие входы усилителей 5 считьшания. Это приводит к тому, что на входах регист- ра 4 к началу третьего такта с выходов усилителей считывания через элементы ИЛИ 13 поступают сигналы только тех разрядов, содержимое которых остается неизменным. Разряды, в ко- торые должно быть записано слово, таким образом, не стробируются, и на соответствующих выходах усилителей к началу третьего такта устанавливается нулевой сигнал.

Одновременно с выходов .инверторов 21 проинвентированные сигналы шифратора поступают на входы элементов И 12, открытые по своим вторым входам сигналом Uj. Выходные сигналы элементов И I2 отпирают те группы элементов И 8, которые находятся в пределах формата записьшаемого слова

0

1

1753

Записываемое слово из млсщших разрядов числовой шины 30 через открытые сигналом и, элементы И 9, одну из групп элементов И 56 коммутатора 19, открытую сигналом с выхода дешифратора 17, открытые элементы И 8 и элементы ИЛИ 13 поступает на входы регистра 4. Указатель формата с выходов усилителей 6 через элементы ИЛИ 14 поступает на входы регистра 4 так же, как и в режиме считьгоания.

В третьем такте вся информация, подлежащая записи в накопитель, сигналом и записывается в регистр 4. В четвертом такте сигналом U. содержимое регистра 4 переписывается в ячейку памяти накопителя по адресу Хд Уг .

Пусть, например, требуется записать новую информацию в позиции слова Х,2, .т.е. в два старших байта ячейки с указателем формата Z 01 (фи1 . 5). Это слово имеет адрес младшего байта Xg 10. В результате считывания ячейки по адресу Х. во втором такте на входах дешифратора 16 устанавливается код 0110, на выходах шифратора 18 - код y,g 001 1 и на выходах инверторов 21 - код У, 1100. Это значит, что единичные сигналы присутствуют на первых стробирующих входах тех усилителей 5, которые соответствуют .двум младших байтам, т.е. слову х, из той же ячейки, и слово х, поступа- - ет на входы регистра 4. Кроме того, сигналами УЗ, 1100 открьшаются те элементы И 8, которые соответствуют двум старшим байтам.

Сигналом с выхода дешифратора 17 в соответствии с адресом байта Хц 10 открывается третья группа элементов И 56 блока 19 (фиг. 3). Слово Xj . из двух младших байтов числовой шины, поступакяцее в режиме записи на входы 27.1 и 27.2, коммутируется на выходы 29.3 и 29.4 блока 19, т.е. со сдвигом влево. Через открытые элементы И 8 и элементы ИЛИ 13 слово х поступает на входы регистра 4.В третьем такте вся информация с выходов элементов ИПИ 14 и 13 записывается в регистр 4. На его выходах формируется код У4 Z(X)o , который и записывается в ячейку накопителя по адресу Х. Таким образом, в результата вьтолнения операции записи в два старших байта выбранной

9125

ячейки записывается новое слово , а содержимое остальных разрядов не изменяется. В рассмотренных режимах значение указателя формата Z оставалось неизменным.

При Uj О и U,f устройство Находится в режиме началь юго заполнения. Предполагается, что запись указателя формата осуществляется однократно перед началом решения задачи одновременно с записью в память программы и исходных данных. На фиг. 6 (цикл T,j) приведен пример записи информации за один цикл во все разряды ячейки. В первом такте цикла Т производится запись адреса ячейки Хд в регистр 2 и адреса байта в регистр 3 сигналом U . При этом должно быть Хц Хз, О, чем обеспечивается обнуление регистра 3 (y,j 0). При этом Ujg 0. Так как УЗ О и U(,g О, то на входах дешифратора 16 в течение цикла Т присутствуют нулевые сигналы, т.е. дли примера по фиг. 4 и 5 код 0000, что согласно приведенной таблице преобразования кодов блоками 16 и 18 обеспечивает на выходе шифратора 18 формирование кода Vjg 0000. Это, в свою очередь, опредв- ляет значения сигналов на .выходах элементов 20 и 21 соответственно rf y,, l.

Отсутствие сигналов на первых управляющих входах усилителей 5 и 6 считывания обеспечивает нулевое значения сигналов на их выходах, т.е. считанная из ячейки информация не регенерируется. Одновременно сигнала ми Uj, и открываются элементы И 9, 12 и 22. Так как У элементы И 8 также открыты. Так как Уд в Xg 00, то сигналом с выхода дешифратора 17 открывается первая группа элементов И 56 коммутатора 19 Хфиг. 3), предназначенная для коммутации Km разрядов без сдвига. Сигналы из числовой магистрали через открытые элементы И 9, элементы. ИЛИ 15 коммутатор 19, открытые элементы И 8 и элементы ИЛИ 13 поступают на входы регистра 4. С входа 3 через открыты элементы И 22 и элементы ИЛИ 14 сигналы нового значения указателя формата поступают на входы регистра 4, В третьем такте эта информация записывется в регистр 4 сигналом U4( , а в четвертом такте сигналом информа75

10

ция переписывается в ячейку памяти накопителя по адресу Хд У . На это цикл начального заполнения заканчивается.

Формула изобретения

Запоминающее устройство, содержащее накопитель, регистр адреса ячейки памяти, регистр адреса байта, регистр записи, К+1 групп усилителей считьгоания, где К - число байтов в ячейке памяти накопителя, по К групп элементов И считьшания, записи, входных и выходных, :элементы И маскирования считьгоания, элементы И маскирования записи,К+1 групп элементов ИЛИ записи К групп элементов ИЛИ записи,К груп элементов ИЛИ коммутации, первый и / второй дешифраторы, шифратор, коммутатор и блок синхронизации, причем выходы регистров адреса ячейки памяти и записи подключены соответственно к адресньгм и числовым входам накопителя, выходы которого подключены к информационным входам соответствующих усилителей считывания, выходы которых подключены к первым / входам соответствующих элементов ИЛИ записи, вьпсоды которых подключены к информационным входам регистра записи, вторые входы элементов ИЛИ записи с первой по К-ю групп соединены с выходами соответствующих элементов И записи, вькоды усилителей считывания с первой по К-ю групп подключены к первым входам соответствующих элементозв И считьшания, первые входы входных и выходы выходных элементов И являются числовыми входами-выходами устройства, информационные входы коммутатора соединены с выходами соответствующих элементов ИЛИ коммутации, выходы коммутатора соединены с первыми входами соответствующих элементов И записи, первые входы элементов ИЛИ коммутации соединены с выходами соответствукяцих входных элементов И, выходы первого дешифратора подключены к входам шифратора, управляющие входы коммутатора соединены с, выходами второго дешифратора, входы которого подключены к выходам регистра адреса байта, первые входы элементов И маскирования считывания и вторые входы выходных элементов И соединены с первым выходом блока синхронизации, первые входы элеменП

тов и маскирования записи и вторые входы входных элементов И соединены с вторым выходом блока синхронизации управляющие входы регистра адреса ячейки памяти и регистра адреса бай- та соединены с третьим выходом блока синхрониза1дии, управляющие входы регистра записи и первого дешифратора соединены соответственно с четвертым и пятым выходами блока синхрони- .зации, первый и второй управляющие входы накопителя соединены с щестым и седьмым выходами блока синхронизации, входы регистра адреса ячейки памяти и регистра адреса байта явля- ются адресными входами устройства, первый, второй, третий входы и группа входов блока синхронизации являются соответственно входами выборки, записи, заполнения и тактовыьт входами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит элементы ИЛИ стро- бирования, инверторы и элементы И начального заполнения, выходы усилите- лей считывания (К-И)-й группы подключены к входам первой группы первого дешифратора, к входам второй группы которого подключены выходы регистра адреса байта, выходы шифра- тора подключены к входам соответст- вукяцих инверторов и к первым входам соответствующих элементов ИЛИ стро175

12

бирования, вторые входы которых соединены с первым выходом блока синхронизации, выходы инверторов подключены к вторым входам соответствующих элементов И маскирования считывания и маскирования записи, выходы которых подключены к вторым входам элементов И считьшаЯия и записи соответствующих групп, вторые входы элементов ИЛИ коммутации с первого по Кт-й, где m - разрядность байта, соединены с выходами элементов И считывания с Кга-го по первый, выходы коммутатора с первого по Кш-й соединены с вторыми входами выходных элементов И с Кт-го по первый, первые входы элементов И начального заполнения являются соответствующими входами начального заполнения устройства, вторые входы соединены с восьмым выходом блока синхронизации, -а выходы подключены к вторым входам (К+1)группы элементов ИЛИ записи, первые управляющие входы усилителей считывания с первой по К-ю групп соединены с выходом соответствующего элемента ИЛИ стробирования, первые управляющие входы (К+1)-й группы усилителей считывания соединены с девятым выходом блока синхронизации, вторые управляющие входы усилителей считывания соединены с десятым выходом блока синхронизации.

4344

АL

-W-J il

4J

3i0Ti

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1984 |

|

SU1185394A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Запоминающее устройство | 1978 |

|

SU769622A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Логическое запоминающее устройство | 1987 |

|

SU1566411A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

Изобретение относится к вычислительной технике и может быть использовано для хранения слов переменной длины, но не большей, чем разрядность ячейки памяти. Целью изобретения является упрощение устройства. Ограничивается число вариантов расположения слов различной разрядности в ячейке памяти. Вид варианта устанавливается заранее, кодируется и записывается в дополнительных разрядах ячейки памяти. Этот код в совокупности с адресом младшего байта считьша- емого или записываемого слова однозначно определяет разрядность этого слова. Устройство содержит накопитель, регистры адреса записи и считьгаания, два дешифратора, шифратор, коммутатор , четыре группы элементов И, три группы элементов ИЛИ, инверторы. 6 ил. (Л с INO ел VI СП

r-i

/

Я

-И5

«

.;

/ Л г/ г/

«

5

1г

31

47

J

«ГЯ

fs Л

8

7Т.

/5Р-

7

г

;

2

Ц8

Л-ц I g I 1Т1

-ж

i 30

33 3 35

4

00

«,

V 0

{JfuA /) Jfff// 7{ |g/A- /j Фи99

CocTuBHtenb A. Дерюгин Редактор A. Orap Техред И.ГаЙдош Корректор A. Тяско

Заказ ДА 19/51 Тираж 543 . Подписное ВНИИПИ ГоеударстйеиНого комитета СССР

по делам изобретений и открытий 113033, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Xt,,

Авторы

Даты

1986-08-15—Публикация

1984-07-16—Подача