Изобретение относится к области вычислительной техники, в частности к организации контроля функционирования СУ спецназначения.

Известно устройство, содержащее главную память, блок команд, блок контроля памяти, блок канала, блок исполнения и пульт управления, устройство, состоящее из коммутатора, регистра верхней границы адресов регистра нижней границы адресов, регистра нижнего адреса программы, регистра количества адресов, используемых в системе, блоков сравнения, логической схемы, вырабатывающей сигнал записи программных событий и распределителя импульсов 1.

Недостаток данного устройства заключается в его недостаточных функциональных возможностях, так как устройство не обеспечивает контроль полноты использования программного изделия, т.е. не обеспечивает проверку полноты использования команд программы во время выполнения ее ЭВМ.

Известно устройство для контроля программ, содержащее блок выделения граничных команд, блок сравнения, блок управления, счетчик, коммутатор, первый и второй блоки памяти, четыре регистра и три группы элементов И 2.

Однако с помощью этого устройства можно зафиксировать лишь факт использования каждой команды программного изделия, при этом устройство не позволяет получать адреса неиспользованных команд, что особенно важно в том случае, если программное изделие расположено не единым массивом, а в нескольких разрозненных областях памяти.

Наиболее близким по технической сущности к предлагаемому являefcя устройство для контроля выполнения программы, состоящее из блока считывания, расположенного в ЭВМ, регистра выборки, входящего в состав блока выборки, блока памяти, блока управления, генератора импульсов и имеющее входы информационный и управляющий, на которые поступают сигналы с контролируемой ЭВМ, причем информационные входы блока считывания являются информационными входами устройства, выход блока считывания связан с информационным входом регистра выборки, выход генератора импульсов связан с первым входом блока управления, второй вход которого связан с управляющим входом устройства, который связан также с управляющими входами блока считывания и регистра выборки, первый выход блока управления связан с управляющим входом блока памяти 3.

Известное устройство не обеспечивает контроля полноты использования программного изделия. Оно фиксирует текущее состояние выполняемой программы для последующего отображения хода программы в индикаторном блоке, однако не позволяет получить адреса команд, ни ра,зу не использовавщихся за весь прогон программного изделия.

Целью изобретения является расщирение функциональных возможностей путем обеспечения полноты контроля использования команд программного изделия.

Поставленная цель достигается тем, что в устройство для контроля программ, содержащее блок считывания, регистр выборки,

0 блок памяти, блок микропрограммного управления и генератор импульсов, информационный вход устройства соединен с информационным входом регистра выборки, выход генератора импульсов связан с тактовым входом блока микропрограммного управле5ния, вход конца операции устройства соединен с управляющим входом регистра выборки и входом запуска блока микропрограммного управления, первый выход которого соединен с входом записи блока памяти вве0дены счетчик слов, счетчик разрядов, регистр сдвига, дещифратор, коммутатор, группа элементов И, элемент ИЛИ, первый и второй элементы И, причем первый информационный вход коммутатора является адресным входом устройства, второй инфор5мационный вход коммутатора соединен с выходом регистра выборки, выходы старщих и младщих разрядов коммутатора соединены с информационными входами соответственно счетчика слов и счетчика разря0дов, выход переполнения которого соединен со счетным входом счетчика слов, информационные выходы счетчика слов и счетчика разрядов являются информационным выходом устройства, информационный выход счетчика разрядов соединен также с входом дещифратора, выход которого соединен с первыми входами элементов И группы и входом информации блока памяти, адресный вход которого соединен с информационным выходом счетчика слов, информационный выход блока памяти соединен с вторыми входами элементов И группы, выходы которых соединены с соответствующими входами элемента ИЛИ, выход элемента ИЛИ соединен с информационным входом регистра сдвига, инверсный выход первого раз5ряда, прямой выход второго разряда, прямой выход первого разряда и инверсный выход второго разряда регистра сдвига соединены соответственно с первым, вторым входами первого элемента И, с первым и вторым входами второго элемента И, выходы

0 первого и второго элементов И соединены соответственно с первым и вторым входами модификации адреса блока микропрограммного управления, выход переполнения счетчика слов соединен с входом останова бло5ка микропрограммного управления, вход режима устройства соединен с входом установки блока микропрограммного управления, второй, третий, четвертый и пятый выходы блока микропрограммного управления соединены соответственно с управляющим входом коммутатора, входами записи счетчиков слов и разрядов, счетным входом счетчика разрядов, входом, сдвига регистра сдвига.

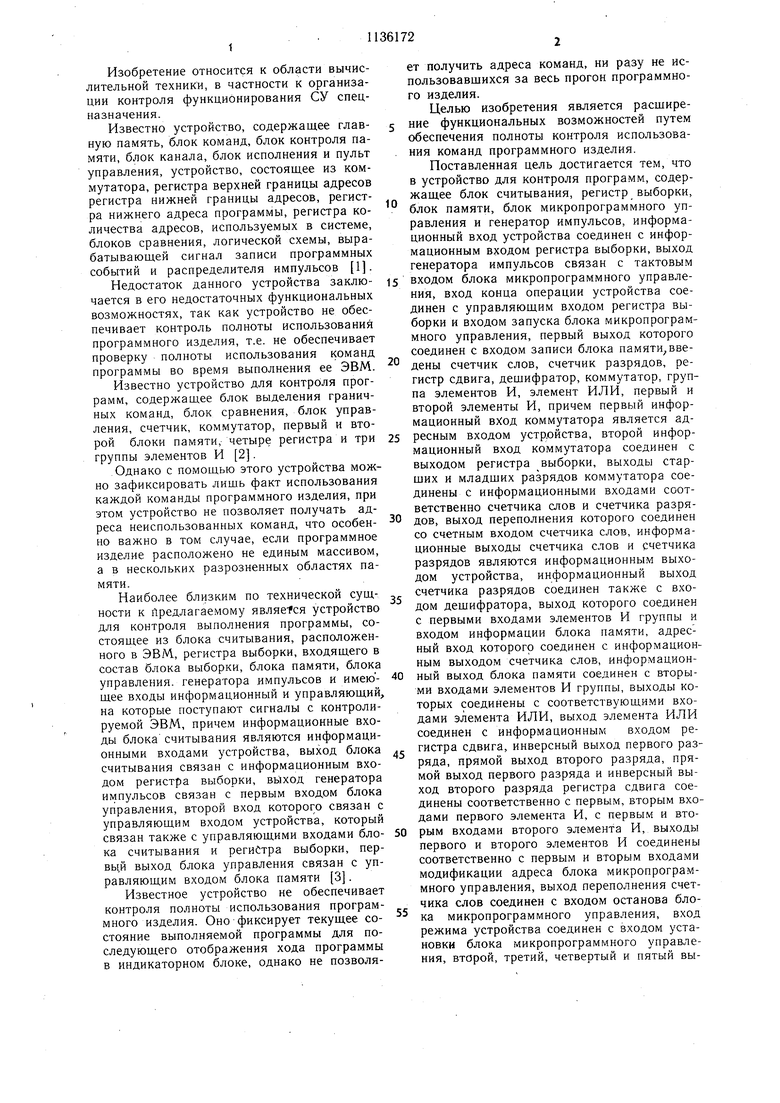

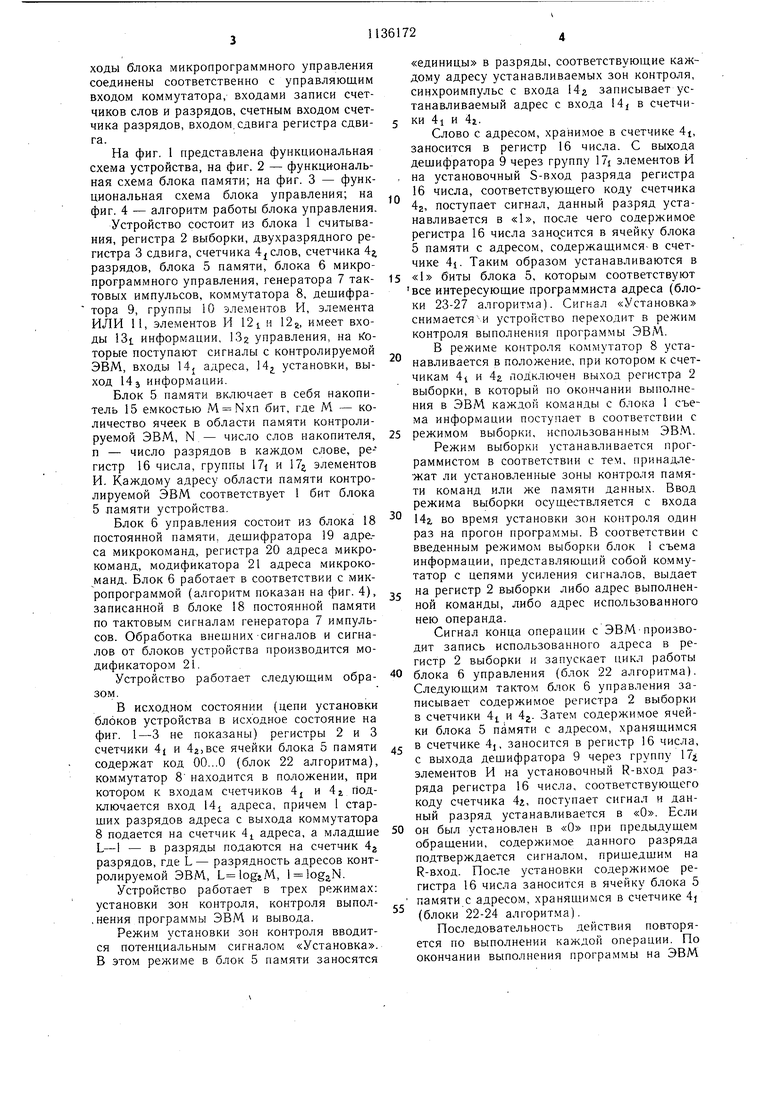

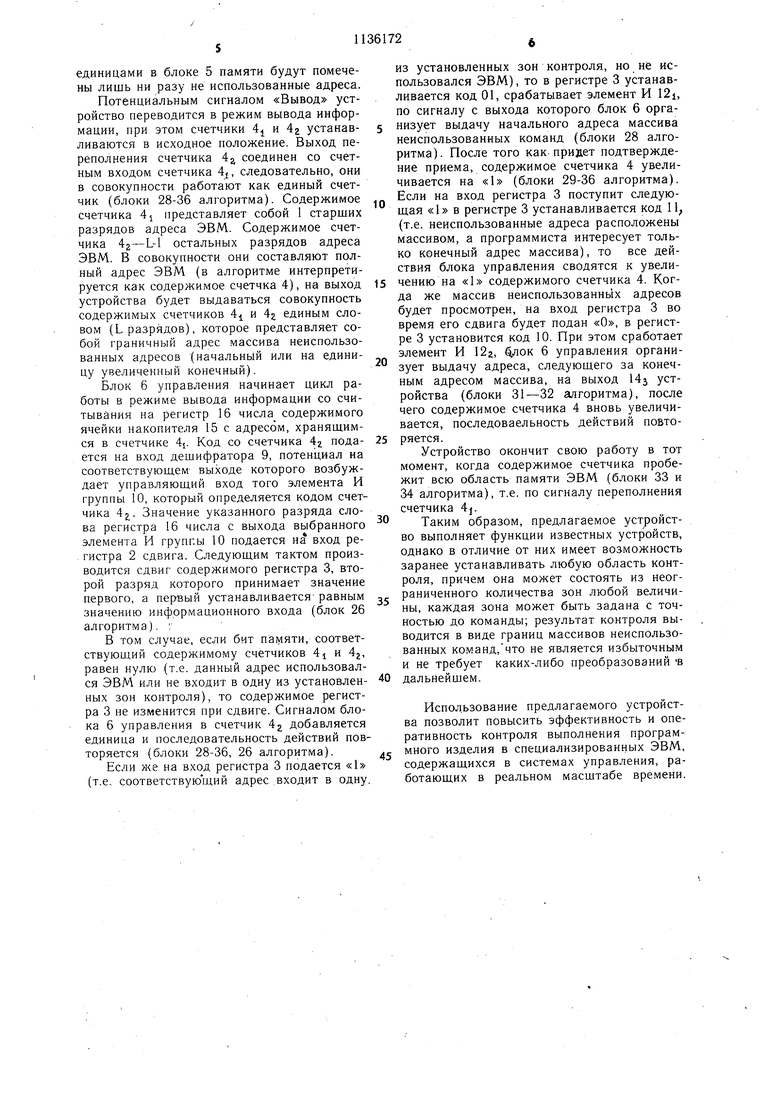

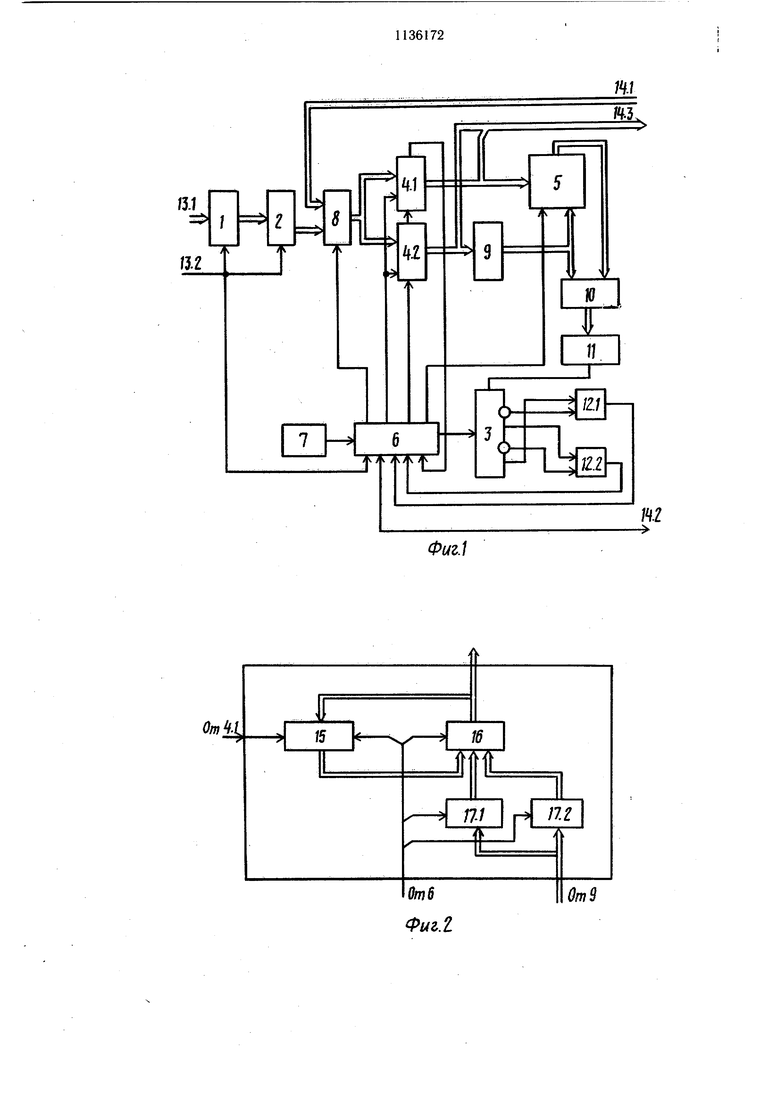

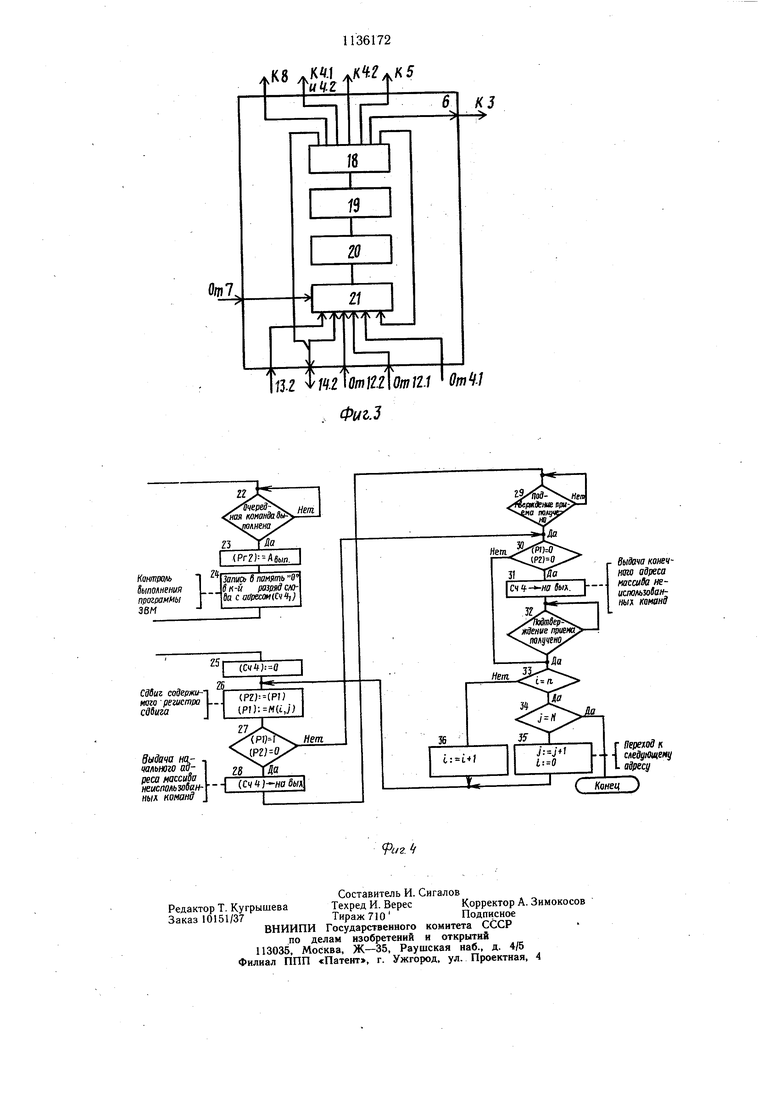

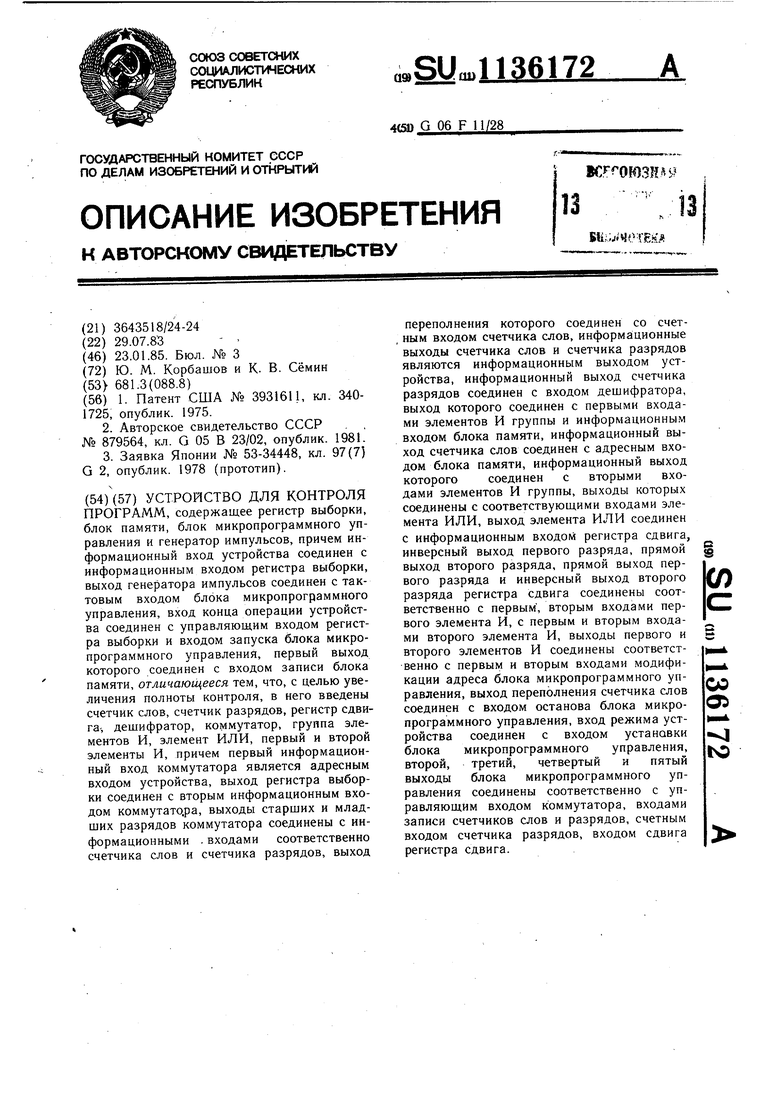

На фиг. 1 представлена функциональная схема устройства, на фиг. 2 - функциональная схема блока памяти; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - алгоритм работы блока управления.

Устройство состоит из блока 1 считывания, регистра 2 выборки, двухразрядного регистра 3 сдвига,счетчика , счетчика 4 разрядов, блока 5 памяти, блока 6 микропрограммного управления, генератора 7 тактовых импульсов, коммутатора 8, дешифратора 9, группы 10 элементов И, элемента ИЛИ И, элементов И 12 и 12g, имеет входы 13i информации, 13г управления, на Которые поступают сигналы с контролируемой ЭВМ, входы 14, адреса, 14j установки, выход Mj информации.

Блок 5 памяти включает в себя накопитель 15 емкостью M Nxn бит, где М - количество ячеек в области памяти контролируемой ЭВМ, N.- число слов накопителя, п - число разрядов в каждом слове, регистр 16 числа, группы 17i и 17 элементов И. Каждому адресу области памяти контролируемой ЭВМ соответствует 1 бит блока 5 ламяти устройства.

Блок 6 управления состоит из блока 18 постоянной памяти, дешифратора 19 адреса микрокоманд, регистра 20 адреса микрокоманд, модификатора 21 адреса микрокоманд. Блок 6 работает в соответствии с микропрограммой (алгоритм показан на фиг. 4), записанной 8 блоке 18 постоянной памяти по тактовым сигналам генератора 7 импульсов. Обработка внешних-сигналов и сигналов от блоков устройства производится модификатором 21.

Устройство работает следующим образом.

В исходном состоянии (цепи установки блоков устройства в исходное состояние на фиг. 1-3 не показаны) регистры 2 и 3 счетчики 4{ и 4г,все ячейки блока 5 памяти содержат код 00...О (блок 22 алгоритма), коммутатор 8 находится в положении, при котором к входам счетчиков 4j и 4j. подключается вход 14i адреса, причем 1 старших разрядов адреса с выхода коммутатора 8 подается на счетчик 4 адреса, а младшие L-1 - в разряды подаются на счетчик 4j разрядов, где L- разрядность адресов контролируемой ЭВМ, L logiM, l logjN.

Устройство работает в трех режимах: установки зон контроля, контроля выпол, нения программы ЭВМ и вывода.

Режим установки зон контроля вводится потенциальным сигналом «Установка. В этом режиме в блок 5 памяти заносятся

«единицы в разряды, соответствующие каждому адресу устанавливаемых зон контроля, синхроимпульс с входа 14 записывает устанавливаемый адрес с входа 14j в счетчи5 ки 4i и 4j..

Слово с адресом, хранимое в счетчике 4t, заносится в регистр 16 числа. С выхода дешифратора 9 через группу 17j элементов И , на установочный S-вход разряда регистра 16 числа, соответствующего коду счетчика

0 42, поступает сигнал, данный разряд устанавливается в «1, после чего содержимое регистра 16 числа заносится в ячейку блока 5 памяти с адресом, содержащимся- в счетчике 4i. Таким образом устанавливаются в 5 «1 биты блока 5, которым соответствуют все интересующие программиста адреса (блоки 23-27 алгоритма). Сигнал «Установка снимается-и устройство переходит в режим контроля выполнения программы ЭВМ.

В режиме контроля коммутатор 8 устанавливается в положение, при котором к счетчикам 4i и 4 подключен выход регистра 2 выборки, в который по окончании выполнения в ЭВМ каждой команды с блока 1 съема информации поступает в соответствии с 5 режимом выборки, использованным ЭВМ.

Режим выборки устанавливается программистом в соответствии с тем, принадлежат ли установленные зоны контроля памяти команд или же памяти данных. Ввод режима выборки осуществляется с входа

14г, во время установки зон контроля один раз на прогон программы. В соответствии с введенным режимом выборки блок 1 съема информации, представляющий собой коммутатор с цепями усиления сигналов, выдает

, на регистр 2 выборки либо адрес выполненной команды, либо адрес использованного нею операнда.

Сигнал конца операции с ЭВМ-производит запись использованного адреса в регистр 2 выборки и запускает 1икл работы

блока 6 управления (блок 22 алгоритма). Следующим тактом блок 6 управления записывает содержимое регистра 2 выборки S счетчики 4j и 4j. Затем содержимое ячейки блока 5 памяти с адресом, хранящимся

r в счетчике 4j, заносится в регистр 16 числа, с выхода дешифратора 9 через группу 17г элементов И на установочный R-вход разряда регистра 16 числа, соответствующего коду счетчика 4j, поступает сигнал и данный разряд устанавливается в «О. Если

0 он был установлен в «О при предыдущем обращении, содержимое данного разряда подтверждается сигналом, пришедшим на R-вход. После установки содержимое регистра 16 числа заносится в ячейку блока 5 памяти с адресом, хранящимся в счетчике 4} (блоки 22-24 алгоритма).

Последовательность действия повторяется по выполнении каждой операции. По окончании выполнения программы на ЭВМ

единицами в блоке 5 памяти будут помечены лишь ни разу не использованные адреса.

Потенциальным сигналом «Вывод устройство переводится в режим вывода информации, при этом счетчики 4 и 4г устанавливаются в исходное положение. Выход переполнения счетчика 4 соединен со счетным входом счетчика 4j, следовательно, они в совокупности работают как единый счетчик (блоки 28-36 алгоритма). Содержимое счетчика 4 представляет собой 1 старших разрядов адреса ЭВМ. Содержимое счетчика 42-L-1 остальных разрядов адреса ЭВМ. В совокупности они составляют полный адрес ЭВМ (в алгоритме интерпретируется как содержимое счетчка 4), на выход устройства будет выдаваться совокупность содержимых счетчиков 4 и 4 единым словом {L разрядов), которое представляет собой граничный адрес массива неиспользованных адресов (начальный или на единицу увеличенный конечный).

Блок 6 управления начинает цикл работы в режиме вывода информации со считывания на регистр 16 числа содержимого ячейки накопителя 15 с адресом, храняшимся в счетчике 4j. Код со счетчика 4 подается на вход дешифратора 9, потенциал на соответствуюш,ем выходе которого возбуждает управляющий вход того элемента И группы 10, который определяется кодом счетчика 42. Значение указанного разряда слова регистра 16 числа с выхода выбранного элемента И группы 10 подается на вход регистра 2 сдвига. Следующим тактом производится сдвиг содержимого регистра 3, второй разряд которого принимает значение первого, а первый устанавливается- равным значению информационного входа (блок 26 алгоритма). ;

В том случае, если бит памяти, соответствуюший содержимому счетчиков 4 и 4j, равен нулю (т.е. данный адрес использовался ЭВМ или не входит в одну из установленных зон контроля), то содержимое регистра 3 не изменится при сдвиге. Сигналом блока 6 управления в счетчик 4j добавляется единица и последовательность действий повторяется (блоки 28-36, 26 алгоритма).

Если же на вход регистра 3 подается «1 (т.е. соответствующий адрес .входит в одну.

из установленных зон контроля, но не использовался ЭВМ), то в регистре 3 устанавливается код 01, срабатывает элемент И 12i, по сигналу с выхода которого блок 6 организует выдачу начального адреса массива неиспользованных команд (блоки 28 алгоритма). После того как придет подтверждение приема, содержимое счетчика 4 увеличивается на «1 (блоки 29-36 алгоритма). Если на вход регистра 3 поступит следуюшая «1 в регистре 3 устанавливается код 11, (т.е. неиспользованные адреса расположены массивом, а программиста интересует только конечный адрес массива), то все действия блока управления сводятся к увеличению на «1 содержимого счетчика 4. Когда же массив неиспользованнь1х адресов будет просмотрен, на вход регистра 3 во время его сдвига будет подан «О, в регистре 3 установится код 10. При этом сработает элемент И 122, йлок 6 управления организует выдачу адреса, следующего за конечным адресом массива, на выход 14з устройства (блоки 31-32 алгоритма), после чего содержимое счетчика 4 вновь увеличивается, последоваельность действий повто5 ряется.

Устройство окончит свою работу в тот момент, когда содержимое счетчика пробежит всю область памяти ЭВМ (блоки 33 и 34 алгоритма), т.е. по сигналу переполнения счетчика 4j.

0 Таким образом, предлагаемое устройство выполняет функции известных устройств, однако в отличие от них имеет возможность заранее устанавливать любую область контроля, причем она может состоять из неограниченного количества зон любой величины, каждая зона может быть задана с точностью до команды; результат контроля выводится в виде границ массивов неиспользованных команд,что не является избыточным и не требует каких-либо преобразований в

0 дальнейшем.

Использование предлагаемого устройства позволит повысить эффективность и оперативность контроля выполнения програмг много изделия в специализированных ЭВМ, содержащихся в системах управления, работающих в реальном масштабе времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для взаимного установления подлинности абонентов | 1986 |

|

SU1442993A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОГРАММ, содержащее регистр выборки, блок памяти, блок микропрограммного управления и генератор импульсов, причем информационный вход устройства соединен с информационным входом регистра выборки, выход генератора импульсов соединен с тактовым входом блока микропрограммного управления, вход конца операции устройства соединен с управляющим входом регистра выборки и входом запуска блока микропрограммного управления, первый выход которого соединен с входом записи блока памяти, отличающееся тем, что, с целью увеличения полноты контроля, в него введены счетчик слов, счетчик разрядов, регистр сдвига-, дешифратор, коммутатор, группа элементов И, элемент ИЛИ, первый и второй элементы И, причем первый информационный вход коммутатора является адресным входом устройства, выход регистра выборки соединен с вторым информационным входом коммутатора, выходы старших и младших разрядов коммутатора соединены с информационными . входами соответственно счетчика слов и счетчика разрядов, выход переполнения которого соединен со счет, ным входом счетчика слов, информа ционные выходы счетчика слов и счетчика разрядов являются информационным выходом устройства, информационный выход счетчика разрядов соединен с входом дешифратора, выход которого соединен с первыми входами элементов И группы и информационным входом блока памяти, информационный выход счетчика слов соединен с адресным входом блока памяти, информационный выход которого соединен с вторыми входами элементов И группы, выходы которых соединены с соответствующими входами элемента ИЛИ, выход элемента ИЛИ соединен с информационным входом регистра сдвига, инверсный выход первого разряда, прямой 9 выход второго разряда, прямой выход пер вого разряда и инверсный выход второго разряда регистра сдвига соединены соответственно с первым , вторым входами первого элемента И, с первым и вторым входами второго элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами модификации адреса блока микропрограммного уп00 О) равления, выход переполнения счетчика слов соединен с входом останова блока микропрограммного управления, вход режима устройства соединен с входом установки блока микропрограммного управления, Ю второй, третий, четвертый и пятый выходы блока микропрограммного управления соединены соответственно с управляющим входом коммутатора, входами записи счетчиков слов и разрядов, счетным входом счетчика разрядов, входом сдвига регистра сдвига.

vK8 .,KJl2.

ОтШ Qm4.1

Фиг.З С f Выдача конечного адреса массива неucnoftbwluHш/х канона г nepeiujd к - -J следднипену Конец J)

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3931611, кл | |||

| 3401725, опублик | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

1985-01-23—Публикация

1983-07-29—Подача