СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| УСТРОЙСТВО ДЛЯ ВИЗУАЛЬНОГО КОНТРОЛЯ ИСПОЛНЕНИЯ ПРОГРАММ | 1991 |

|

RU2012044C1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1439605A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

Изобретение может быть использовано в вычислительной технике для контроля выполнения программ в цифровых вычислительных машинах и программируемых контроллерах, построенных по принципу "общей магистрали". Цель изобретения - повышение быстродействия устройства. Правильность выполнения рабочей программы контролируется путем одновремен-22 г9 ^^27

VJ

О Ю СО

ю

ного с выборкой из основной памяти начальной команды некоторого линейного участка рабочей программы извлечения из памяти устройства для контроля выполнения программ команды проверки правильности выполнения каждой команды линейного участка. Команда проверки содержит информацию, определяющую ожидаемое число импульсов синхронизации машинных циклов. Эта информация помещается в блок счета количества импульсов синхронизации, содержимое которого в дальнейшем уменьшается по мере прохождения линейного участка. Одновременно в ходе выполнения линейного участка программы производится контроль прохождения программы по адресам выборки команд путем сравнения текущего адреса программы и адреса-копии, вырабатываемого устройстИзобретение относится к вычислительной технике и может быть использовано для контроля выполнения программ в цифровых вычислительных машинах и программируемых контроллерах, построенных по принципу общей магистрали,

Цель изобретения - повышение быстродействия устройства.

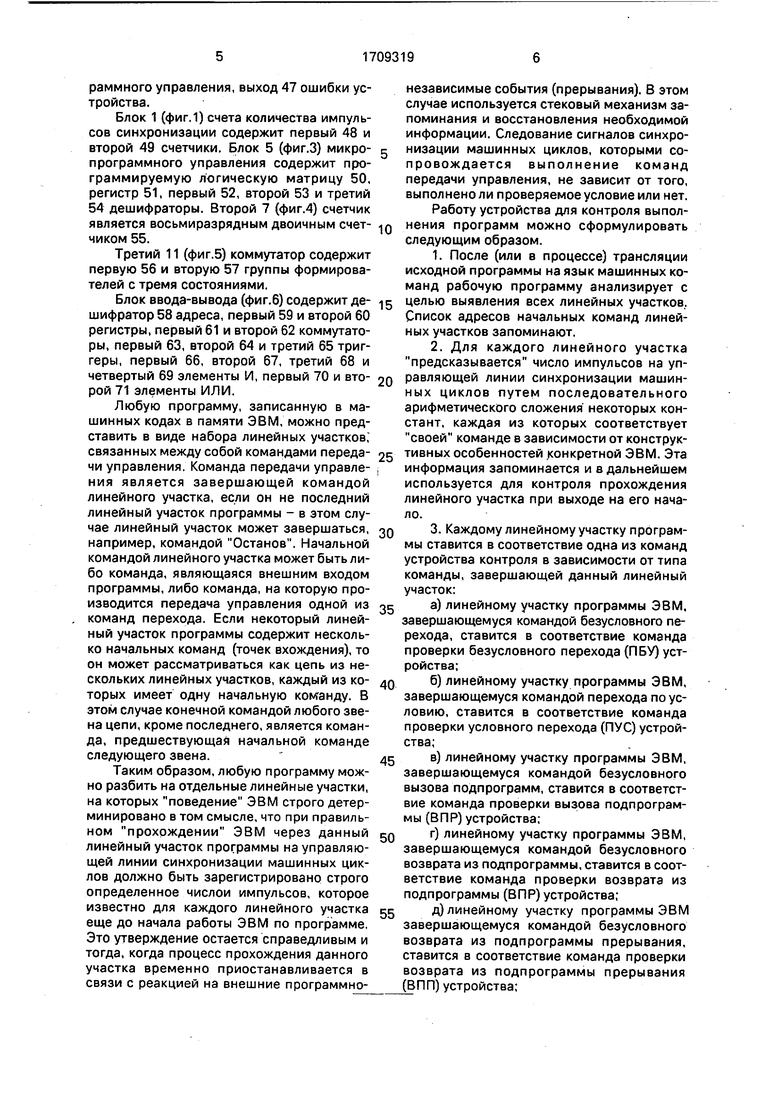

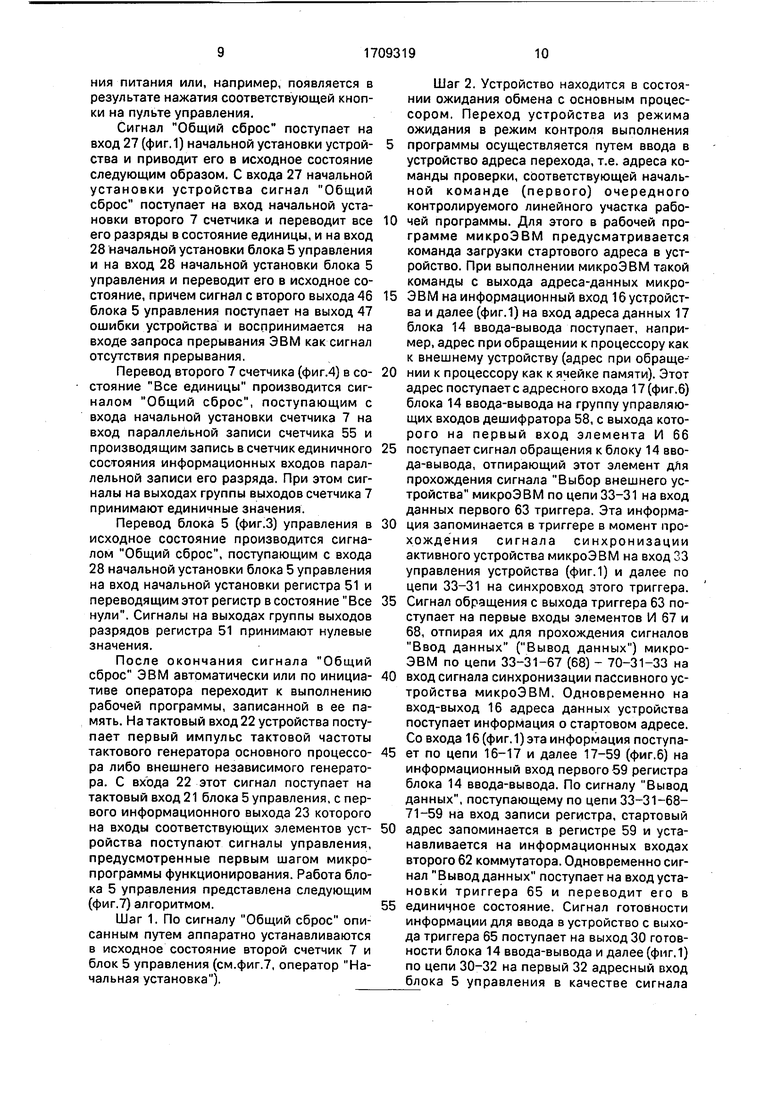

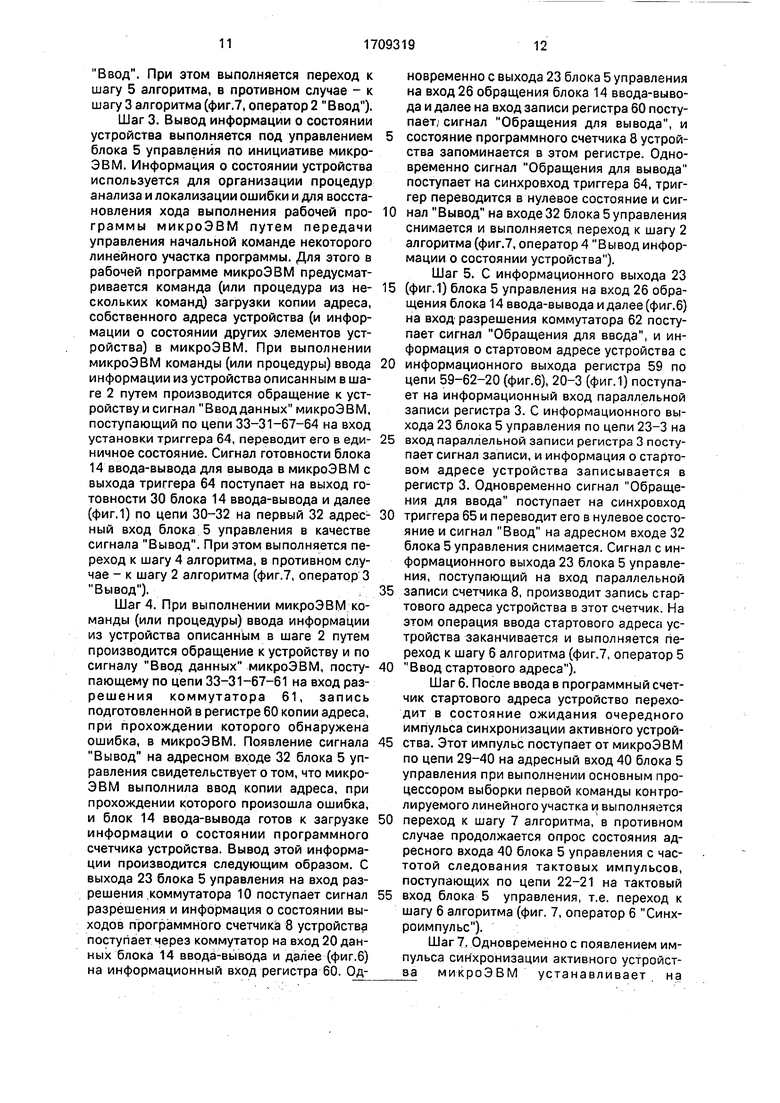

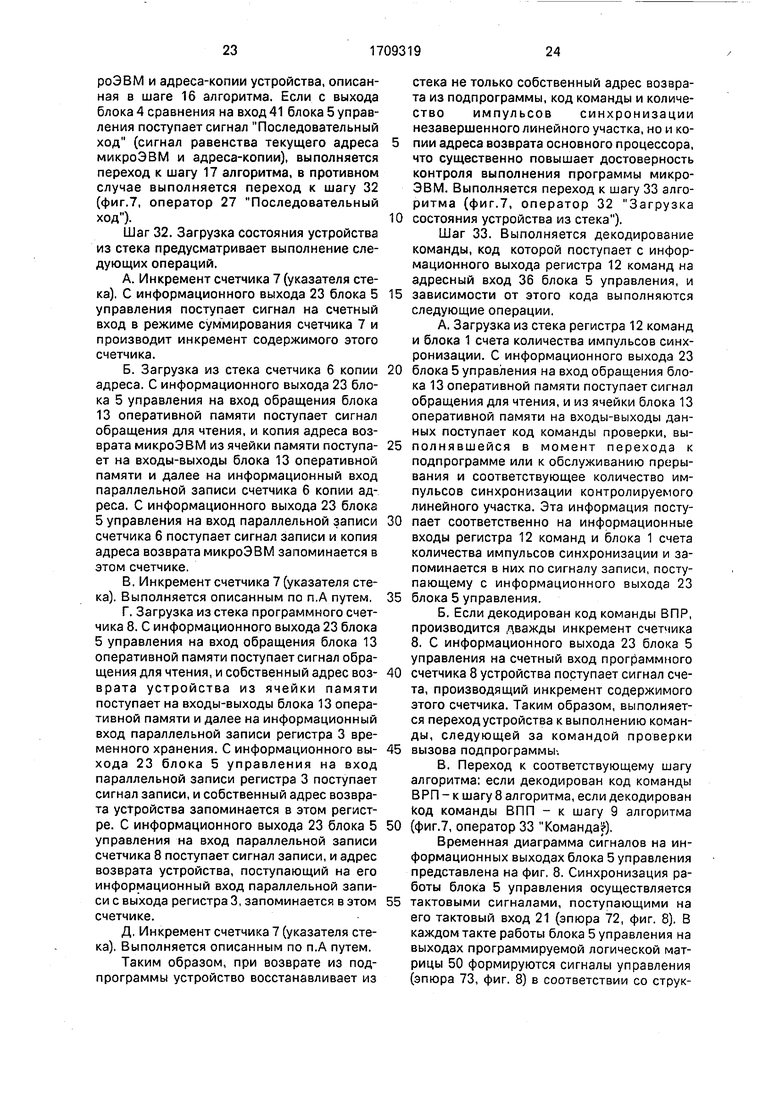

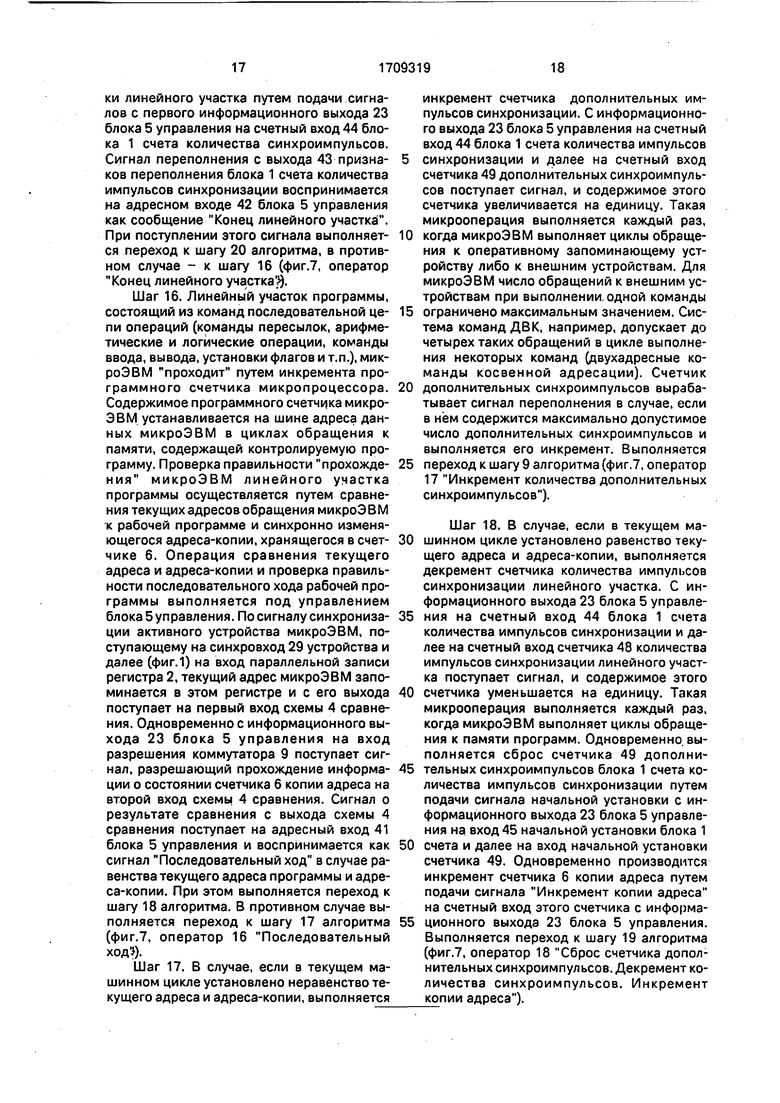

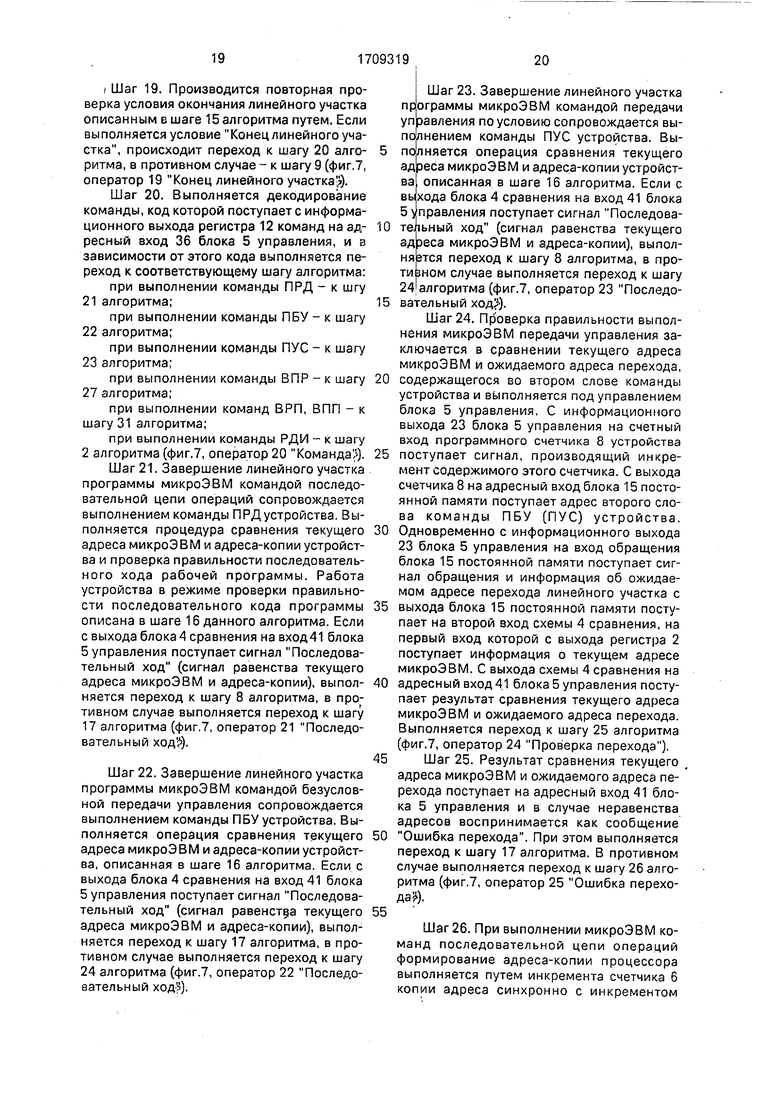

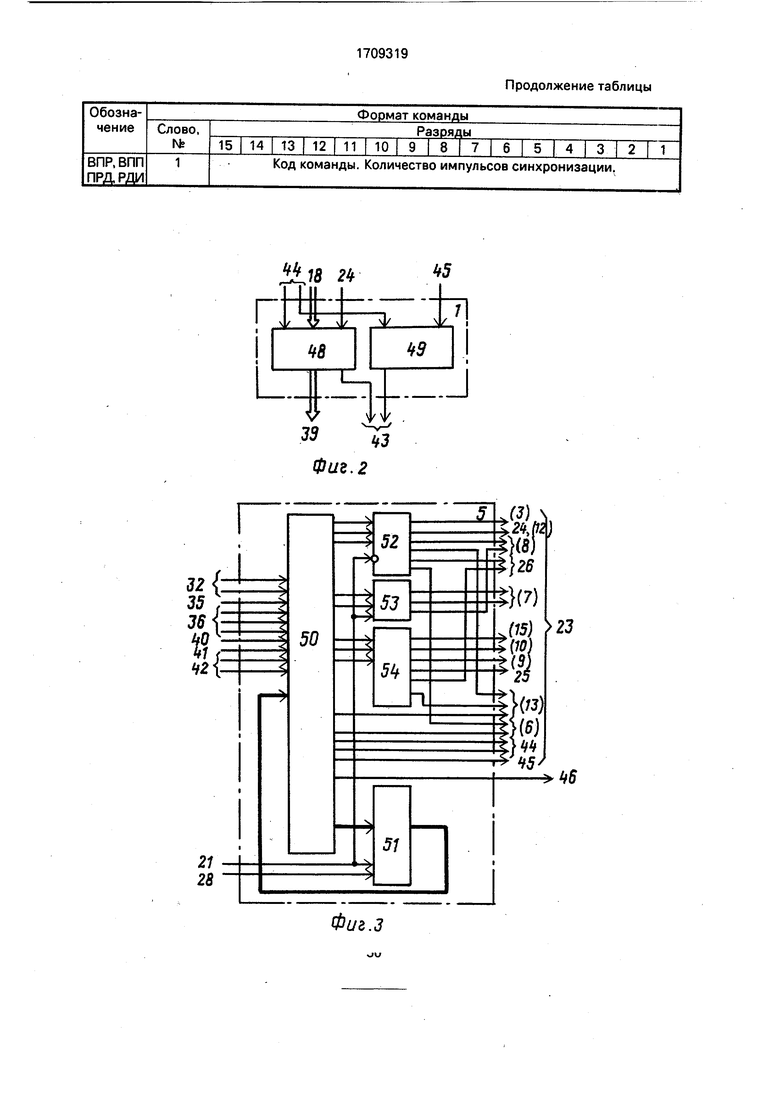

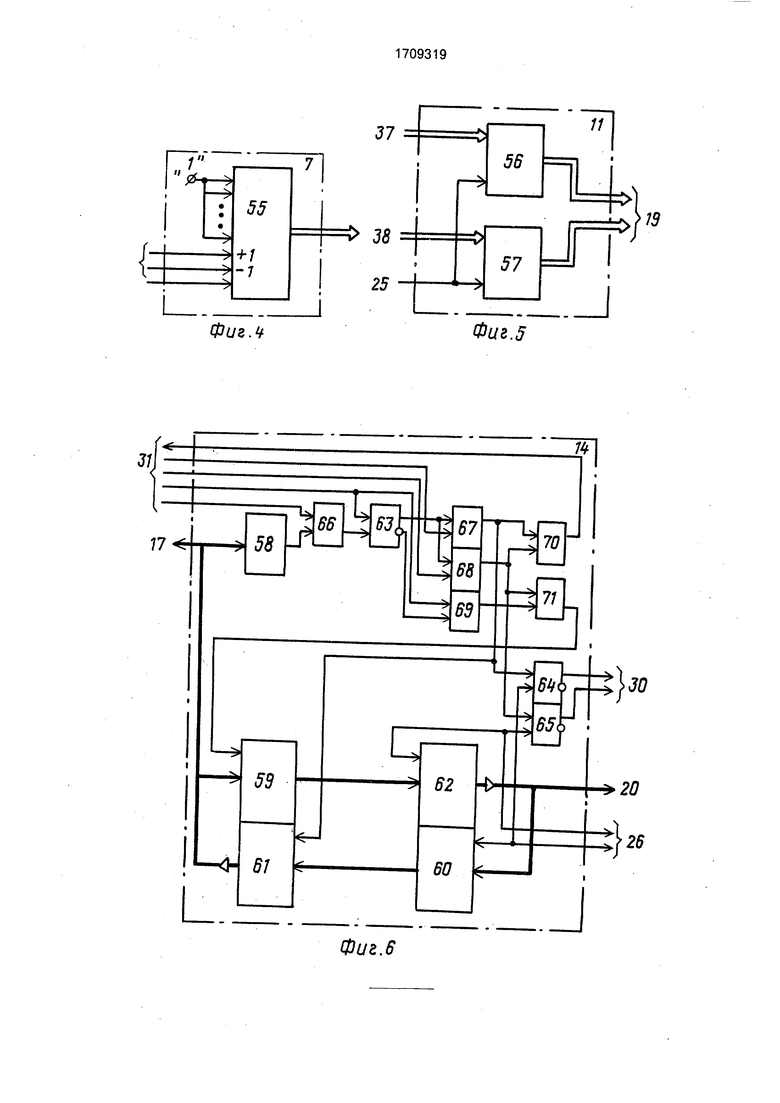

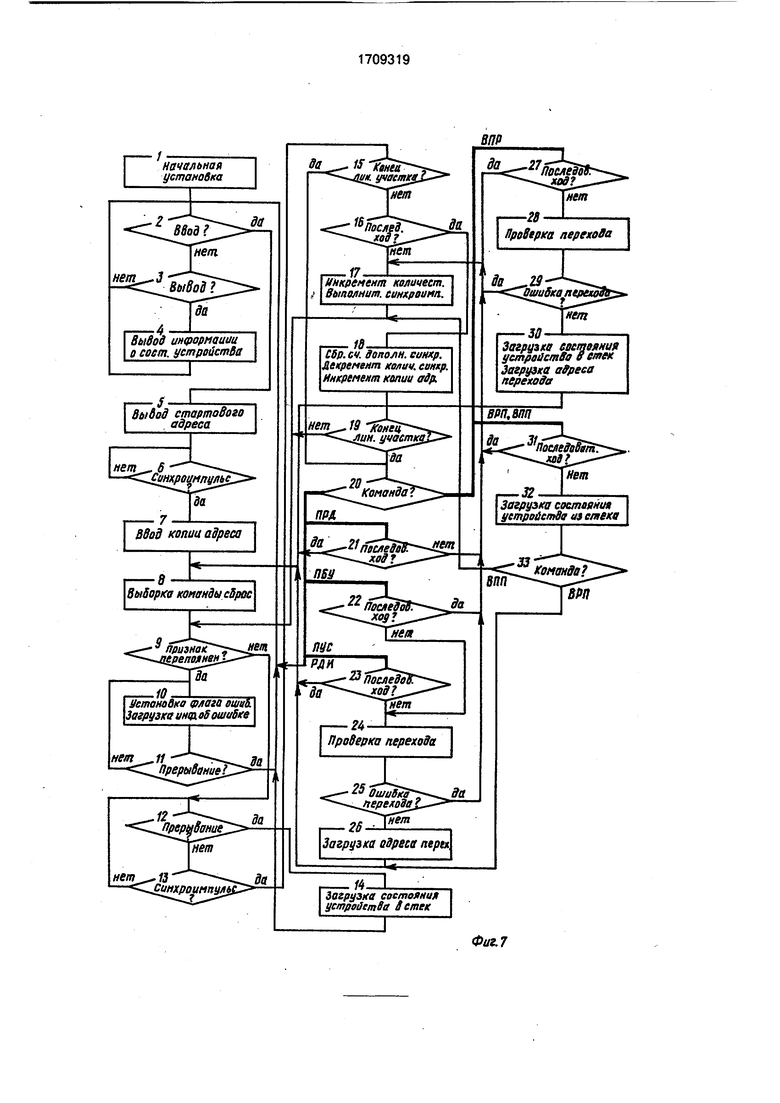

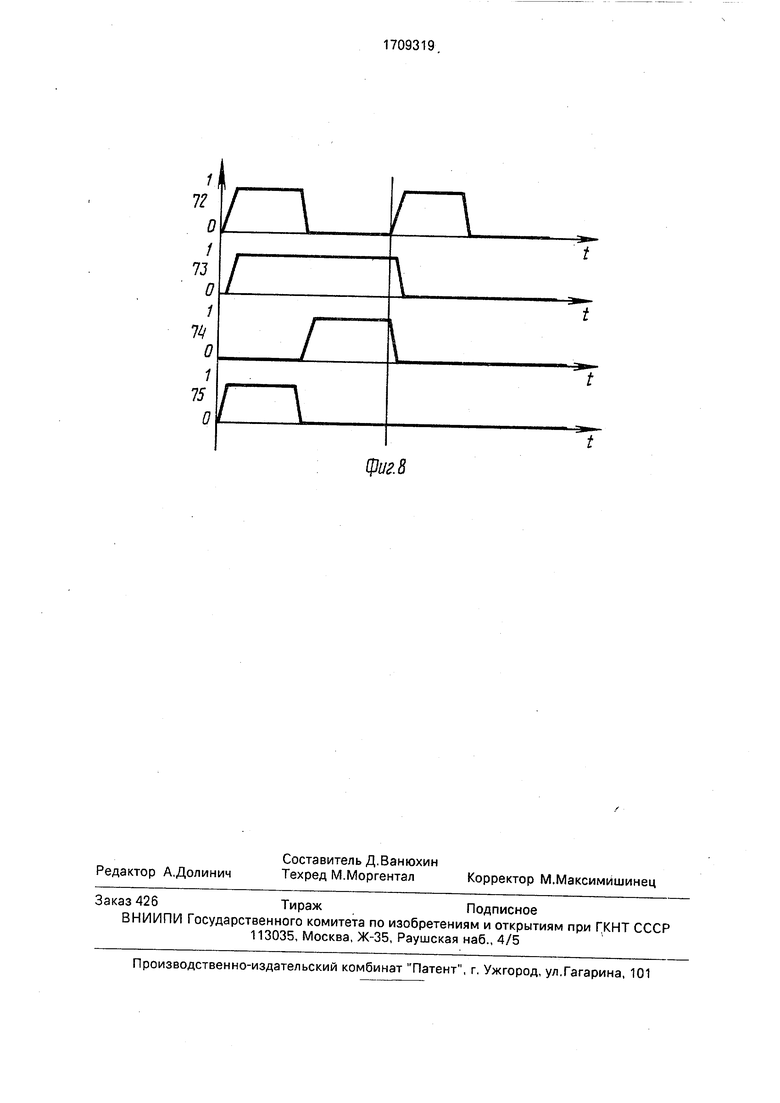

На фиг. 1 представлена функциональная схема устройства для контроля выпол-, нения программ; на фиг. 2-6 - примеры реализации функциональных узлов устройства для контроля вьшолнения программ микропроцессорной системы; на фиг. 2 функциональная схема блока счета количества импульсов синхронизации; на фиг. 3 функциональная схема второго счетчика; на фиг. 5 - функциональная схема третьего коммутатора; на фиг. 6 - функциональная схема блока ввода-вывода; на фиг. 7 - схема алгоритма функционирования блока микропрогрммного управления устройства; на фиг. 8 - временная диаграмма сигналов на информационных выходах блока микропрограммного управления устройства.

Устройство для контроля выполнения программ (фиг. 1) содержит блок 1 счета количества импульсов синхронизации, первый 2 и второй 3 блоки регистров, схему 4 сравнения, блок 5 микропрограммного управления, первый б, второй 7 и третий 8 счетчики, первый 9, второй 10 и третий 11 коммутаторы, регистр 12 команд, блок 13 оперативной памяти, блок 14 ввода-вывода

вом на каждом шаге выполнения программы. К моменту перехода на начало нового линейного участка содержимое блока счетчиков обнуляется, выполняется проверка поведения ЭВМ в соответствии с командой проверки устройства и, если это соответствие выполняется, производится формирование новой копии текущего адреса путем извлечения адреса перехода из команды устройства и выборка команды нового линейного участка. Устройство для контроля выполнения программ содержит блок 1 счета количества импульсов синхронизации, блоки регистров 2, 3, схему сравнения 4, блок 5 микропрограммного управления, счетчики 6, 7 и 11, регистр 12 команд, блок 13 оперативной памяти, блок 14 ввода-вывода и блок 15 постоянной памяти. 2 з.п.ф-лы, 8 ил., 1 табл.

и блок 15 постоянной памяти, информационный 16 вход устройства, вход-выход адреса данных 17 блока ввода-вывода, информационный 18 вход блока счета количества импульсов синхронизации, выход 19 третьего коммутатора, информационный вход-выход 20 блока ввода-вывода, тактовый вход 21 блока микропрограммного управления, тактовый вход 22 устройства,

группу выходов 23 блока микропрограммного управления, вход записи 24 блока счета количества импульсов синхронизации, вход разрешения 25 третьего коммутатора, вход 26 обращения блока ввода-вывода, входы

начальной установки 27 устройства и 28 блока микропрограммного управления, синхровход 29 устройства, выход 30 готовности и управляющий вход-выход 31 блока вводавывода, первый 32 вход условий блока микропрограммного управления, управляющий вход-выход 33 устройства, вход 34 подтверждения прерывания устройства, второй 35 вход условий блока микропрограммного управления, вход 36 кода операций блока микропрограм ного управления, первый 37 и второй 38 информационные входы третьего коммутатора, информационный выход 39 блока счета количества импульсов синхронизации, третий 40, четвертый 41 и пятый 42

входы условий блока микропрограммного управления, выход 43 переполнения блока счета количества импульсов синхронизации, вход 44 начальной установки и счетный 45 вход блока счета количества импульсов

синхронизации, выход 46 блока микропрограммного управления, выход 47 ошибки устройства.

Блок 1 (фиг.1) счета количества импульсов синхронизации содержит первый 48 и второй 49 счетчики. Блок 5 (фиг.З) микропрограммного управления содержит программируемую логическую матрицу 50, регистр 51, первый 52, второй 53 и третий 54 дешифраторы. Второй 7 (фиг.4) счетчик является восьмиразрядным двоичным счетчиком 55.

Третий 11 (фиг.5) коммутатор содержит первую 56 и вторую 57 группы формирователей с тремя состояниями.

Блок ввода-вывода (фиг.б) содержит дешифратор 58 адреса, первый 59 и второй 60 регистры, первый 61 и второй 62 коммутаторы, первый 63, второй 64 и третий 65 триггеры, первый 66, второй 67, третий 68 и четвертый 69 элементы И, первый 70 и второй 71 элементы ИЛИ.

Любую программу, записанную в машинных кодах в памяти ЭВМ, можно представить в виде набора линейных участков; связанных между собой командами передачи управления. Команда передачи управления является завершающей командой линейного участка, если он не последний линейный участок программы - в этом случае линейный участок может завершаться, например, командой Останов. Начальной командой линейного участка может быть либо команда, являющаяся внешним входом программы, либо команда, на которую производится передача управления одной из команд перехода. Если некоторый линейный участок программы содержит несколько начальных команд (точек вхождения), то он может рассматриваться как цепь из нескольких линейных участков, каждый из которых имеет одну начальную команду. В этом случае конечной командой любого звена цепи, кроме последнего, является команда, предшествующа начальной команде следующего звена.

Таким образом, любую программу можно разбить на отдельные линейные участки, на которых поведение ЭВМ строго детерминировано в том смысле, что при правильном прохождении ЭВМ через данный линейный участок программы на управляющей линии синхронизации машинных циклов должно быть зарегистрировано строго определенное числои импульсов, которое известно для каждого линейного участка еще до начала работы ЭВМ по программе. Это утверждение остается справедливым и тогда, когда процесс прохождения данного участка временно приостанавливается в связи с реакцией на внешние программнонезависимые события (прерывания). В этом случае используется стековый механизм запоминания и восстановления необходимой информации. Следование сигналов синхронизации машинных циклов, которыми сопровождается выполнение команд передачи управления, не зависит от того, выполнено ли проверяемое условие или нет. Работу устройства для контроля выполQ нения программ можно сформулировать следующим образом.

5 целью выявления всех линейных участков. Список адресов начальных команд линейных участков запоминают.

Q 3. Каждому линейному участку программы ставится в соответствие одна из команд устройства контроля в зависимости от типа команды, завершающей данный линейный участок:

5 а) линейному участку программы ЭВМ. завершающемуся командой безусловного перехода, ставится в соответствие команда проверки безусловного перехода (ПБУ) устройства;

0 б) линейному участку программы ЭВМ, завершающемуся командой перехода по условию, ставится в соответствие команда проверки условного перехода (ПУС) устройства;

5 в) линейному участку программы ЭВМ, завершающемуся командой безусловного вызова подпрограмм, ставится в соответствие команда проверки вызова подпрограммы (ВПР) устройства;

0 г) линейному участку программы ЭВМ, завершающемуся командой безусловного возврата из подпрограммы, ставится в соответствие команда проверки возврата из подпрограммы (ВПР) устройства:

5 д) линейному участку программы ЭВМ завершающемуся командой безусловного возврата из подпрограммы прерывания, ставится в соответствие команда проверки возврата из подпрограммы прерывания (ВПП) устройства;

е)линейному участку программы ЭВМ, завершающемуся командой последовательной цепи операций, ставится в соответствие команда проверки продолжения последовательных операций (ПРД) устройства;

ж)линейному участку программы ЭВМ, завершающемуся командой передачи управления по вычисленному адресу (командой, реализующей программный переключатель не более чем два адреса, или командой передачи управления в неконтролируемую область памяти), ставится в соответствие команда перехода в режим диалога в ЭВМ (РДИ) устройства.

К моменту перехода ча начало нового линейного участка содержимое счетчиков количества импульсов синхронизации становится равным нулю. В момент обнуления счетчиков выполняется проверка поведения ЭВМ в соответствии с командой проверкой устройства для контроля выполнения программ И, если это соответствие выполняется, производится формирование копии адреса первой команды очередного линейного участка с использованием информации, содержащейся в завершенной команде и выборка команды проверки этого линейного участка.

Память программ контролируемых ЭВМ

и программируемых контроллеров выполняется в виде постоянного или полупостоянного запоминающего устройства. Вводимая в память рабочая программа представлена в

0 виде последовательности машинных кодов. Ее ввод в память ЭВМ должен сопровождаться вводом в блок памяти процессора заранее подготовленной программы контроля выполнения рабочей программы. Программа контроля также должна быть представлена в виде последовательности машинных кодов. Форматы команд проверки, конструктивные особенности элементов схемы устройства и алгоритм работы блока

0 управления определяются конструктивными особенностями, интерфейсом и форматом команд конкретной микроЭВМ.

Рассмотрим построение системы контроля выполнения программ для программируемого контроллера, построенного на базе микроэвм МС1201.

Форматы команд проверки линейных участков представлены в таблице.

По своему формату команды устройства

0 разделяются на две группы. Команды устройства первой группы, включающей команды проверки ПБУ, ПУС и ВПР, состоят из трех слов. Первое слово команд этой группы состоит из двух частей: кода операции и количества импульсов синхронизации машинных циклов соответствующего линейного участка. Второе и третье слова команд этой группы являются соответственно адресом перехода соответствующего линейного

0 участка программы основного процессора и адресом перехода устройства при завершении проверки этого линейного участка, т.е. адресом команды проверки программы контроля, на которую передается управление

5 при переходе к новому линейному участку рабочей программы.

Команды устройства второй группы, включающей команды проверки ВРП, ВПП, ПРД и РДИ, состоят из одного слова, содержащего две части: код операции и количество импульсов синхронизации машинных циклов соответствующего линейного участка.

Устройство работает следующим обра5 зом.

Э&М приводится в исходное состояние путем подачи соответствующего сигнала на линию Общий сброс, входящую в состав интерфейсных шин. Сигнал на этой линии формируется автоматически после включения питания или, например, появляется в результате нажатия соответствующей кнопки на пульте управления.

Сигнал Общий сброс поступает на вход 27 (фиг.1) начальной установки устройства и приводит его в исходное состояние следующим образом. С входа 27 начальной установки устройства сигнал Общий сброс поступает на вход начальной установки второго 7 счетчика и переводит все его разряды в состояние единицы, и на вход 28 начальной установки блока 5 управления и на вход 28 начальной установки блока 5 управления и переводит его в исходное состояние, причем сигнал с второго выхода 46 блока 5 управления поступает на выход 47 ошибки устройства и воспринимается на входе запроса прерывания ЭВМ как сигнал отсутствия прерывания.

Перевод второго 7 счетчика (фиг.4) в состояние Все единицы производится сигналом Общий сброс, поступающим с входа начальной установки счетчика 7 на вход параллельной записи счетчика 55 и производящим запись в счетчик единичного состояния информационных входов параллельной записи его разряда. При этом сигналы на выходах группы выходов счетчика 7 принимают единичные значения.

Перевод блока 5 (фиг.З) управления в исходное состояние производится сигналом Общий сброс, поступающим с входа 28 начальной установки блока 5 управления на вход начальной установки регистра 51 и переводящим этот регистр в состояние Все нули. Сигналы на выходах группы выходов разрядов регистра 51 принимают нулевые значения.

После окончания сигнала Общий сброс ЭВМ автоматически или по инициативе оператора переходит к выполнению рабочей программы, записанной в ее память. На тактовый вход 22 устройства поступает первый импульс тактовой частоты тактового генератора основного процессора либо внешнего независимого генератора. С входа 22 этот сигнал поступает на тактовый вход 21 блока 5 управления, с первого информационного выхода 23 которого на входы соответствующих элементов устройства поступают сигналы управления, предусмотренные первым шагом микропрограммы функционирования. Работа блока 5 управления представлена следующим (фиг.7) алгоритмом.

Шаг 1. По сигналу Общий сброс описанным путем аппаратно устанавливаются в исходное состояние второй счетчик 7 и блок 5 управления (см.фиг.7, оператор Начальная установка).

Шаг 2. Устройство находится в состоянии ожидания обмена с основным процессором. Переход устройства из режима ожидания в режим контроля выполнения

программы осуществляется путем ввода в устройство адреса перехода, т.е. адреса команды проверки, соответствующей начальной команде (первого) очередного контролируемого линейного участка рабочей программы. Для этого в рабочей программе микроэвм предусматривается команда загрузки стартового адреса в устройство. При выполнении микроЭВМ такой команды с выхода адреса-данных микро5 ЭВМ на информационный вход 16 устройства и далее (фиг.1) на вход адреса данных 17 блока 14 ввода-вывода поступает, например, адрес при обращении к процессору как к внешнему устройству (адрес при обраще0 НИИ к процессору как к ячейке памяти). Этот адрес поступаете адресного входа 17 (фиг.6) блока 14 ввода-вывода на группу управляющих входов дешифратора 58, с выхода которого на первый вход элемента И 66

5 поступает сигнал обращения к блоку 14 ввода-вывода, отпирающий этот элемент дЛя прохождения сигнала Выбор внешнего устройства микроэвм по цепи 33-31 на вход данных первого 63 триггера. Эта информация запоминается в триггере в момент про хождения сигнала синхронизации активного устройства микроЭВМ на вход 33 управления устройства (фиг.1) и далее по цепи 33-31 на синхровход этого триггера.

5 Сигнал обращения с выхода триггера 63 поступает на первые входы элементов И 67 и 68, отпирая их для прохождения сигналов Ввод данных (Вывод данных) микроЭВМ по цепи 33-31-67 (68) - 70-31-33 на

0 вход сигнала синхронизации пассивного устройства микроэвм. Одновременно на вход-выход 16 адреса данных устройства поступает информация о стартовом адресе. Со входа 16 (фиг. 1) эта информация поступает по цепи 16-17 и далее 17-59 (фиг.6) на информационный вход первого 59 регистра блока 14 ввода-вывода. По сигналу Вывод данных, поступающему по цепи 33-31-6871-59 на вход записи регистра, стартовый

0 адрес запоминается в регистре 59 и устанавливается на информационных входах второго 62 коммутатора. Одновременно сигнал Вывод данных поступает на вход установки триггера 65 и переводит его в

5 едини1 ное состояние. Сигнал готовности информации для ввода в устройство с выхода триггера 65 поступает на выход 30 готовности блока 14 ввода-вывода и далее (фиг.1) по цепи 30-32 на первый 32 адресный вход блока 5 управления в качестве сигнала

Ввод. При этом выполняется переход к шагу 5 алгоритма, в противном случае - к шагу 3 алгоритма (фиг,7, оператор 2 Ввод).

Шаг 3. Вывод информации о состоянии устройства выполняется под управлением блока 5 управления по инициативе микррЭВМ. Информация о состоянии устройства используется для организации процедур анализа и локализации ошибки и для восстановления хода выполнения рабочей программы микроэвм путем передачи управления начальной команде некоторого линейного участка программы. Для этого в рабочей программе микроЭВМ предусматривается команда (или процедура из нескольких коман/0 загрузки копии адреса, собственного адреса устройства (и информации о состоянии других элементов устройства) в микроэвм. При выполнении микроэвм команды (или процедуры) ввода информации из устройства описанным в шаге 2 путем производится обращение к устройству и сигнал Вводданных микроЭВМ, поступающий по цепи 33-31-67-64 на вход установки триггера 64, переводит его в единичное состояние. Сигнал готовности блока 14 ввода-вывода для вывода в микроЭВМ с выхода триггера 64 поступает на выход готовности 30 блока 14 ввода-вывода и далее (фиг.1) по цепи 30-32 на первый 32 адресный вход блока 5 управления в качестве сигнала Вывод. При этом выполняется переход к шагу 4 алгоритма, в противном случае - к шагу 2 алгоритма (фиг.7, оператор 3 Вывод).Л

Шаг 4. При выполнении микроЭВМ команды (или процедуры) ввода информации из устройства описанным в шаге 2 путем производится обращение к устройству и по сигналу Ввод данных микроЭВМ, поступающему по цепи 33-31-67-61 на вход разрешения коммутатора 61, запись подготовленной в регистре 60 копии адреса, при прохождении которого обнаружена ошибка, в микроэвм. Появление сигнала Вывод на адресном входе 32 блока 5 управления свидетельствует о том, что микроЭВМ выполнила ввод копии адреса, при прохождении которого произошла ошибка, и блок 14 ввода-вывода готов к загрузке информации о состоянии программного счетчика устройства. Вывод этой информации производится следующим образом. С выхода 23 блока 5 управления на вход разрешения .коммутатора 10 поступает сигнал разрешения и информация о состоянии выходов программного счетчика 8 устройства поступает через коммутатор на вход 20 данных блока 14 ввода-вывода и далее (фиг.6) на информационный вход регистра 60. Одновременно с выхода 23 блока 5 управления на вход 26 обращения блока 14 ввода-вывода и далее на вход записи регистра 60 поступает; сигнал Обращения для вывода, и состояние программного счетчика 8 устройства запоминается в этом регистре. Одновременно сигнал Обращения для вывода поступает на синхровход триггера 64, триггер переводится в нулевое состояние и сигнал Вывод на входе 32 блока 5 управления снимается и выполняется, переход к шагу 2 алгоритма (фиг.7, оператор 4 Вывод информации о состоянии устройства).

Шаг 5. С информационного выхода 23 (фиг.1) блока 5 управления на вход 26 обращения блока 14 ввода-вывода и далее (фиг.6) на вход разрешения коммутатора 62 поступает сигнал Обращения для ввода, и информация о стартовом адресе устройства с информационного выхода регистра 59 по цепи 59-62-20 (фиг.6), 20-3 (фиг.1) поступает на информационный вход параллельной записи регистра 3. С информационного выхода 23 блока 5 управления по цепи 23-3 на вход параллельной записи регистра 3 поступает сигнал записи, и информация о стартовом адресе устройства записывается в регистр 3. Одновременно сигнал Обращения для ввода поступает на синхровход триггера 65 и переводит его в нулевое состояние и сигнал Ввод на адресном входе 32 блока 5 управления снимается. Сигнал с информационного выхода 23 блока 5 управления, поступающий на вход параллельной записи счетчика 8, производит запись стартового адреса устройства в этот счетчик. На этом операция ввода стартового адреса устройства заканчивается и выполняется переход к шагу 6 алгоритма (фиг.7, оператор 5 Ввод стартового адреса).

Шаг 6. После ввода в программный счетчик стартового адреса устройство переходит в состояние ожидания очередного импульса синхронизации активного устройства. Этот импульс поступает от микроЭВМ по цепи 29-40 на адресный вход 40 блока 5 управления при выполнении основным процессором выборки первой команды контролируемого линейного участка и выполняется переход к шагу 7 алгоритма, в противном случае продолжается опрос состояния адресного входа 40 блока 5 управления с частотой следования тактовых импульсов, поступающих по цепи 22-21 на тактовый вход блока 5 управления, т.е. переход к шагу 6 алгоритма (фиг. 7, оператор 6 Синхроимпульс).

Шаг 7. Одновременно с появлением импульса синхронизации активного устройства микроэвм устанавливает на

входе-выходе 16 адреса данных.устройства адрес первой команды контролируемого линейного участка. Этот адрес поступает по цепи 16-17 на вход-выход 17 адреса данных блока 14 ввода-вывода и далее на группу управляющих входов дешифратора 58 и сигнал на его выходе принимает нулевое значение. Этот сигнал запирает элемент И 66 для прохождения сигнала выбора внешнего устройства по цепи 33-31-66-63 на вход данных триггера 63, и по сигналу синхронизации активного устройства этот триггер переходит в нулевое состояние. Единичный сигнал с инверсного выхода триггера 63 поступает по цепи 63-69-71-59 на вход параллельной записи регистра 59 и адрес первой команды контролируемого линейного участка, поступивший с входа 17 на информационные входы этого регистра, запоминается в нем. С информационного выхода 23 блока 5 управления по цепи 23-26 и далее на вход разрешения коммутатора 62 поступает сигнал разрешения и информация об адресе первой команды контролируемого линейного участка поступает по цепи 59-62-20 (фиг.б) и далее (фиг.1) по цепи 20-6 на вход параллельной записи регистра 6. С информационного выхода 23 блока 5 управления по цепи 23-6 на вход параллельной записи регистра 6 поступает сигнал записи, и информация об адресе первой команды контролируемого линейного участка запоминается в этом регистре. Выполняется переход к шагу 8 алгоритма (фиг.7, оператор 7 Ввод копии адреса).

Шаг 8. По стартовому адресу, определяемому выходныК1и сигналами счетчика 8, из блока 15 постоянной памяти выбирается первое слово очередной команды устройства и загружается соответственно первая часть, определяющая код команды проверки в регистр 12 команд и вторая часть, определяющая количество импульсов синхронизации машинных циклов выборки команд очередного линейного участка, - в блок 1 счета количества импульсов синхронизации. Выборка команды обеспечивается путем подачи сигналов с первого 23 информационного выхода блока 5 управления на вход обращения блока 15 постоянной памяти, вход 24 записи блока 1 счета количества импульсов синхронизации и вход записи регистра 12 команд. Одновременно с первого 23 информационного выхода блока 5 управления на вход 45 начальной установки блока 1 счета количества импульсов синхронизации и далее (фиг.2) на вход начальной установки счетчика 49 дополнительных синхроимпульсов поступает сигнал начальной установки и переводит его в нулевое

состояние. Выполняется переход к шагу 9 алгоритма (фиг.7, оператор 8 Выборка команды. Сброс счетчика дополнительных синхроимпульсов).V

Шаг 9. После начальной установки блока 1 счета количества импульсов синхронизации сигнал об отсутствии переполнения счетчика 49 дополнительных синхроимпульсов этого блока с выхода 43 признаков переполнения поступает на адресный вход 42 блока 5 управления. Счетчик 49 дополнительных синхроимпульсов производит подсчет количества импульсов синхронизации машинных циклов каждой команды микро5 ЭВМ, в течение которых производится обращение к оперативной памяти либо внешним устройством микроэвм. При превышении максимального допустимого количества обращений к внешним устройствам в ходе выполнения команды микроЭВМ с выхода признаков переполнения блока 1 счета количества импульсов синхронизации поступает Признак переполнения счетчика дополнительных синхроимпульсов, свидетельствующий о неправильном прохождении текущей команды микроЭВМ, и выполняется переход к шагу 10 алгоритма, в противном случае - к шагу 12 (фиг.7, оператор 9 Признак переполнения).

0 Шаг 10. На втором 46 информационном выходе блоха 5 управления устанавливается сигнал Флаг ошибки. Этот сигнал постугэет на выход 47 ошибки устройства и воспринимается на входе запроса прерывания

5 микроэвм как сигнал запроса прерывания на обслуживание устройства. Одновременно выполняется загрузка информации о копии адреса, при прохождении которого обнаружена ошибка, vts регистра 6 копии

0 адреса в блок 14 ввода- вывода. Загрузка копии адреса обеспечивается путем подачи сигналов с первого 23 информационного выхода блока 5 управления на вход разрешения коммутатора 9 и вход 26 обращения

5 блока 14 ввода-вывода. Информация о копии адреса поступает по цепи 6-9-20 на вход данных блока 14 ввода-вывода и далее (фиг.б) по цепи 20-60 на информационный вход регистра 60, где запоминается по сигналу обращения, поступающему с входа 26 обращения на вход параллельной записи этого регистра. Выполняется переход к шагу 11 алгоритма (фиг.7, оператор 10 Установка флага ошибки. Загрузка информации

5 об ошибке).

Шаг 11. В ответ на запрос прерывания, поступивший в микроэвм с выхода 47 ошибки устройства, с выхода подтверждения прерывания микроЭВМ на вход 34 подтверждения прерывания устройства и далее

(фиг.1) на адресный вход 35 блока 5 управления поступает сигнал подтверждения прерывания на обслуживание устройства. В ответ на этот сигнал выполняется переход к шагу 2 алгоритма, т.е. устройство переходит в режим ожидания обмена с микроЭВМ для вывода информации об ошибке и ввода нового стартового адреса, в противном случае выполняется переход к шагу 10 алгоритма, т.е. устройство подтверждает установку флага ошибки до выхода микроЭВМ на его обслуживание (фиг.7, оператор 11 Прерываниер.

Шаг 12. Если с соответствующего выхода микроэвм на вход 34 подтверждения прерывания устройства и далее (фиг.1) на адресный вход 35 блока 5управления поступает сигнал Подтверждение прерывания на обслуживание внешних устройств и микроЭВМ переходит к выполнению подпрограмм прерывания, выполняется переход к шагу 14 алгоритма, в противном случае - к шагу 13 (фиг.7, оператор 12 Прерывание ).

Шаг 13. После ввода копии адреса начальной команды первого контролируемого линейного участка и выборки команды собственной программы контроля устройство переходит в режим контроля прохождения команд микроэвм. В ответ на каждый синхроимпульс устройство проверяет правильность следования адресов программы микроэвм на входе-выходе 16 адреса данных. При появлении очередного синхроимпульса выполняется переход к шагу 15 алгоритма, в противном случае - к шагу 12 (фиг.7, оператор Синхроимпульс).

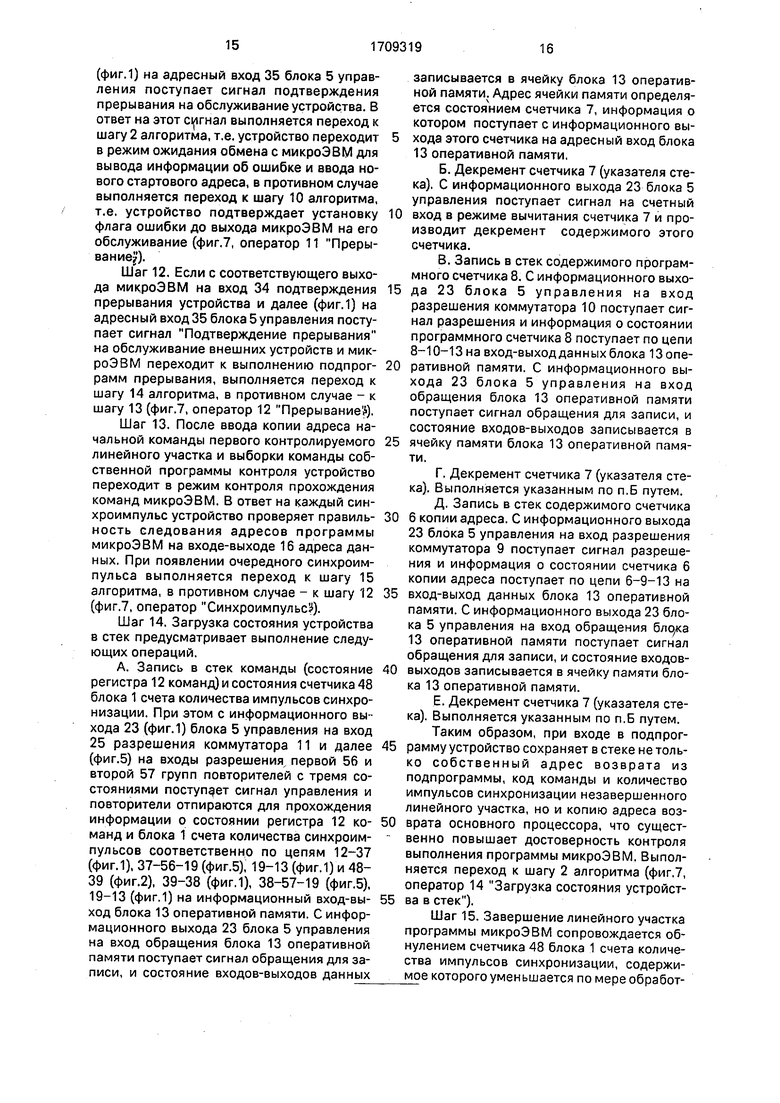

Шаг 14. Загрузка состояния устройства в стек предусматривает выполнение следующих операций.

А. Запись в стек команды (состояние регистра 12 команд) и состояния счетчика 48 блока 1 счета количества импульсов синхронизации. При этом с информационного выхода 23 (фиг.1) блока 5 управления на вход 25 разрешения коммутатора 11 и далее (фиг.5) на входы разрешения первой 56 и второй 57 групп повторителей с тремя состояниями поступает сигнал управления и повторители отпираются для прохождения информации о состоянии регистра 12 команд и блока 1 счета количества синхроимпульсов соответственно по цепям 12-37 (фиг.1), 37-56-19 (фиг.5), 19-13 (фиг.1) и 4839 (фиг.2), 39-38 (фиг.1), 38-57-19 (фиг.5), 19-13 (фиг.1) на информационный вход-выход блока 13 оперативной памяти. С информационного выхода 23 блока 5 управления на вход обращения блока 13 оперативной памяти поступает сигнал обращения для записи, и состояние входов-выходов данных

записывается в ячейку блока 13 оперативной памяти. Адрес ячейки памяти определяется состоянием счетчика 7, информация о котором поступает с информационного выхода этого счетчика на адресный вход блока 13 оперативной памяти.

Б. Декремент счетчика 7 (указателя стека). С информационного выхода 23 блока 5 управления поступает сигнал на счетный вход в режиме вычитания счетчика 7 и производит декремент содержимого этого счетчика.

В. Запись в стек содержимого программного счетчика 8. С информационного выхода 23 блока 5 управления на вход разрешения коммутатора 10 поступает сигнал разрешения и информация о состоянии программного счетчика 8 поступает по цепи 8-10-13 на вход-выходданных блока 13 оперативной памяти. С информационного выхода 23 блока 5 управления на вход обращения блока 13 оперативной памяти поступает сигнал обращения для записи, и состояние входов-выходов записывается в ячейку памяти блока 13 оперативной памяти.

Г. Декремент счетчика 7 (указателя стека). Выполняется указанным по п.Б путем.

Д. Запись в стек содержимого счетчика 6 копии адреса. С информационного выхода 23 блока 5 управления на вход разрешения коммутатора 9 поступает сигнал разрешения и информация о состоянии счетчика 6 копии адреса поступает по цепи 6-9-13 на вход-выход данных блока 13 оперативной памяти. С информационного выхода 23 блока 5 управления на вход обращения 13 оперативной памяти поступает сигнал обращения для записи, и состояние входоввыходов записывается в ячейку памяти блока 13 оперативной памяти.

Е. Декремент счетчика 7 (указателя стека). Выполняется указанным по п.Б путем.

Таким образом, при входе в подпрограмму устройство сохраняет в стеке не только собственный адрес возврата из подпрограммы, код команды и количество импульсов синхронизации незавершенного Линейного участка, но и копию адреса возврата основного процессора, что существенно повышает достоверность контроля выполнения программы микроЭВМ. Выполняется переход к шагу 2 алгоритма (фиг.7, оператор 14 Загрузка состояния устройства в стек).

Шаг 15. Завершение линейного участка программы микроэвм сопровождается обнулением счетчика 48 блока 1 счета количества импульсов синхронизации, содержимое которого уменьшается по мере обработпрограммного счетчика микроЭВМ. При выполнении микроэвм команд переходов формирование адреса копии устройства производится путем записи в счетчик 6 копии адреса содержимого второго слова команды устройства после подтверждения правильности их выполнения микроЭВМ. Запись адреса перехода в счетчик 6 выполняется под управлением блока 5 управления. С информационного выхода 23 блока 5 управления на вход обращения блока 15 постоянной памяти поступает сигнал обращения и информация об адресе перехода с выхода блока 15 постоянной памяти поступает на информационный вход параллельной записи счетчика 6 копии адреса. Одновременно с информационного выхода 23 блока 5 управления на вход записи счетчика б поступает сигнал записи и адрес перехода запоминается в зтом счетчике. С информационного выхода 23 блока 5 управления на счетный вход счетчика 8 поступает сигнал счета и производит инкремент его содержимого. С информационного выхода счетчика 8 на адресный вход блока 15 постоянной памяти поступает адрес третьего слова команды проверки перехода (адрес информации о собственном адресе перехода устройства). Одновременно с информационного выхода 23 блока 5 управления на вход обращения блока 15 постоянной памяти поступает сигнал обращения и информация о собственном адресе перехода устройства поступает с выхода блока 15 постоянной памяти на информационный вход параллельной записи регистра 3. С информационного выхода 23 блока 5 управления на вход параллельной записи регистра 3 поступает сигнал записи, и информация о собственном адресе перехода записывается в регистр 3. С информационного выхода 23 блока 5 управления на вход параллельной записи счетчика 8 поступает сигнал записи, и информация о собственном адресе перехода запоминается в счетчике 8. С выхода счетчика 8 адрес команды проверки очередного линейного участка поступает на адресный вход блока 15 постоянной памяти, и выполняется переход к шагу 8 алгоритма (фиг.7, оператор 26 Запуска адреса перехода).

Шаг 27. Завершение линейного участка программы микроэвм командой вызова подпрограммы сопровождается выполнением команды ВПР устройства. Выполняется операция сравнения текущего адреса микроэвм и адреса-копии устройства, описанная в шаге 16 алгоритма. Если с выхода блока 4 сравнения на вход 41 блока 5 управления поступает сигнал Последовательный

ход (сигнал равенства текущего адреса микроэвм и адреса-копии), выполняется переход к шагу 17 алгоритма, в противном случае выполняется переход к шагу 28 алгоритма (фиг.7, оператор 27 Последовательный ход).

Шаг 28. Проверка правильности выполнения микроэвм передачи управления при выполнении команд вызова подпрограмм

0 заключается в сравнении текущего адреса микроэвм и ожидаемого адреса перехода, содержащегося во втором слове команды устройства, и выполняется описанным в шаге 24 данного алгоритма путем. С выхода

5 схемы 4 сравнения на адресный вход 41 блока 5 управления поступает результат сравнения текущего адреса микроЭВМ и ожидаемого адреса передачи управления при вызове подпрограммы. Выполняется

0 переход к шагу 29 алгоритма (фиг.7, оператор 28 Проверка перехода).

Шаг 29. Результат сравнения текущего адреса микроЭВМ и ожидаемого адреса передачи управления подпрограмме поступает на адресный вход 41 блока 5 управления и в случае неравенства адресов воспринимается как сообщение Ошибка перехода. При зтом выполняется переход к шагу 17 алгоритма. В противном случае выполняется переход к шагу 30 алгоритма (фиг.7, оператор 29 Ошибка перехода).

Шаг 30. Загрузка состояния устройства в стек предусматривает выполнение процедур: а) запись в стек команды из регистра 12

5 команд и состояния блока 1 счета количества импульсов синхронизации; б)декремент счетчика 7 (указателя стека); в) запись в стек содержимого программного счетчика 8; г) декремент указателя стека; д) запись в стек

0 содержимого счетчика б копии адреса; е) декремент указателя стека, описанных в шаге 14 алгоритма.

Затем выполняется загрузка счетчика 6 копии адреса вторым словом команды ВПР,

5 т.е. адресом рабочей программы, на который произведена передача управления при вызове подпрограммы, и программного счетчика 8 устройства третьим словом команды ВПР, т.е. собственным адресом передачи управления устройства, описанным в шаге 26 данного алгоритма путем. Выполняется переход к шагу 8 алгоритма (фиг.7, оператор 30 Загрузка состояния устройства в стек. Загрузка адреса перехода).

5 Шаг 31. Завершение линейного участка программы микроэвм командой возврата из подпрограммы и прерывания сопровождается выполнением соответственно команд ВПР и ВПП устройства. Выполняется операция сравнения текущего адреса микроЭВМ и адреса-копии устройства, описанная в шаге 16 алгоритма. Если с выхода блока 4 сравнения на вход 41 блока 5 управления поступает сигнал Последовательный ход (сигнал равенства текущего адреса микроэвм и адреса-копии), выполняется переход к шагу 17 алгоритма, в противном случае выполняется переход к шагу 32 (фиг.7, оператор 27 Последовательный ход).

Шаг 32. Загрузка состояния устройства из стека предусматривает выполнение следующих операций.

A.Инкремент счетчика 7 (указателя стека). С информационного выхода 23 блока 5 управления поступает сигнал на счетный вход в режиме суммирования счетчика 7 и производит инкремент содержимого этого счетчика.

Б. Загрузка из стека счетчика б копии адреса. С информационного выхода 23 блока 5 управления на вход обращения блока 13 оперативной памяти поступает сигнал обращения для чтения, и копия адреса возврата микроэвм из ячейки памяти поступает на входы-выходы блока 13 оперативной памяти и далее на информационный вход параллельной записи счетчика 6 копии адреса. С информационного выхода 23 блока 5 управления на вход параллельной записи счетчика 6 поступает сигнал записи и копия адреса возврата микроЭВМ запоминается в этом счетчике.

B.Инкремент счетчика 7 (указателя стека). Выполняется описанным по п.А путем.

Г. Загрузка из стека программного счетчика 8. С информационного выхода 23 блока 5 управления на вход обращения блока 13 оперативной памяти поступает сигнал обращения для чтения, и собственный адрес возврата устройства из ячейки памяти поступает на входы-выходы блока 13 оперативной памяти и далее на информационный вход параллельной записи регистра 3 временного хранения. С информационного выхода 23 блока 5 управления на вход параллельной записи регистра 3 поступает сигнал записи, и собственный адрес возврата устройства запоминается в этом регистре. С информационного выхода 23 блока 5 управления на вход параллельной записи счетчика 8 поступает сигнал записи, и адрес возврата устройства, поступающий на его информационный вход параллельной записи с выхода регистра 3, запоминается в этом счетчике.

Д. Инкремент счетчика 7 (указателя стека). Выполняется описанным по п.А путем.

Таким образом, при возврате из подпрограммы устройство восстанавливает из

стека не только собственный адрес возврата из подпрограммы, код команды и количество импульсов синхронизации незавершенного линейного участка, но и коПИИ адреса возврата основного процессора, что существенно повышает достоверность контроля выполнения программы микроЭВМ. Выполняется переход к шагу 33 алгоритма (фиг.7, оператор 32 Загрузка

0 состояния устройства из стека).

Шаг 33. Выполняется декодирование команды, код которой поступает с информационного выхода регистра 12 команд на адресный вход 36 блока 5 управления, и

5 зависимости от этого кода выполняются следующие операции.

A.Загрузка из стека регистра 12 команд и блока 1 счета количества импульсов синхронизации. С информационного выхода 23

0 блока 5 управления на вход обращения блока 13 оперативной памяти поступает сигнал обращения для чтения, и из ячейки блока 13 оперативной памяти на входы-выходы данных поступает код команды проверки, выполнявшейся в момент перехода к подпрограмме или к обслуживанию прерывания и соответствующее количество импульсов синхронизации контролируемого линейного участка. Эта информация поступает соответственно на информационные входы регистра 12 команд и блока 1 счета количества импульсов синхронизации и запоминается в них по сигналу записи, поступающему с информационного выхода 23

5 блока 5 управления.

Б. Если декодирован код команды ВПР, производится дважды инкремент счетчика 8. С информационного выхода 23 блока 5 управления на счетный вход программного

0 счетчика 8 устройства поступает сигнал счета, производящий инкремент содержимого этого счетчика. Таким образом, выполняется переход устройства к выполнению команды, следующей за командой проверки

5 вызова подпрограммы-.

B.Переход к соответствующему шагу алгоритма: если декодирован код команды ВРП - к шагу 8 алгоритма, если декодирован Код команды ВПП - к шагу 9 алгоритма

0 (фиг.7, оператор 33 Команда).

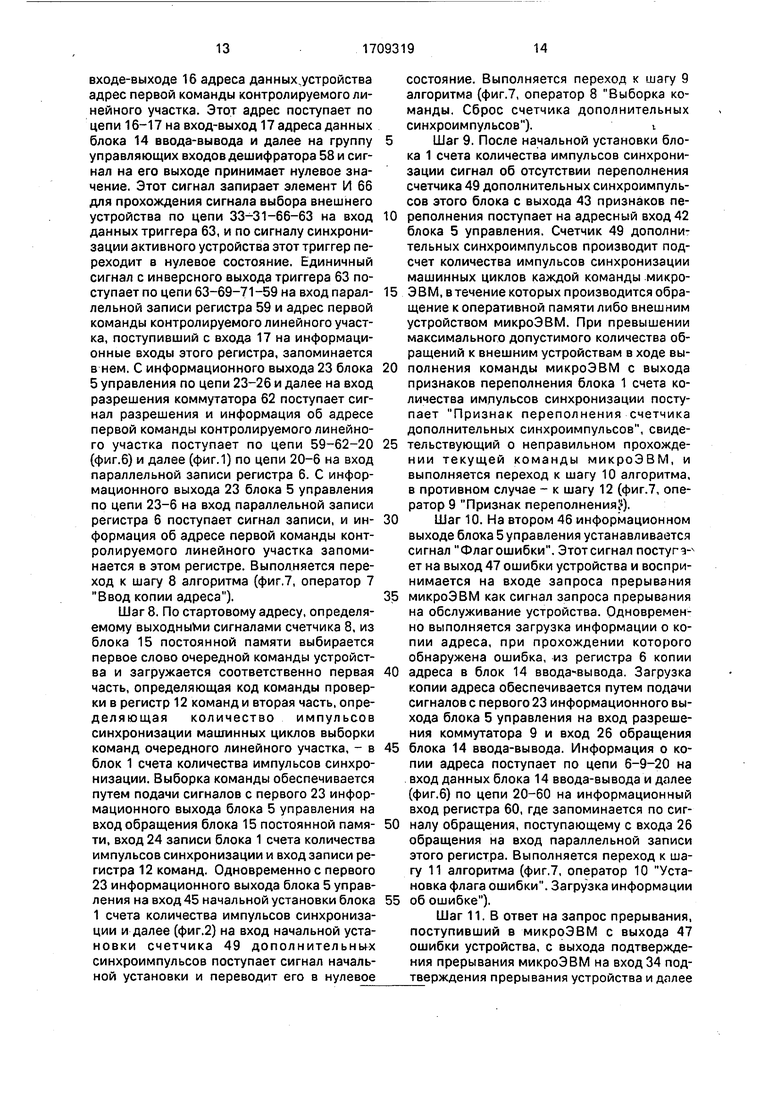

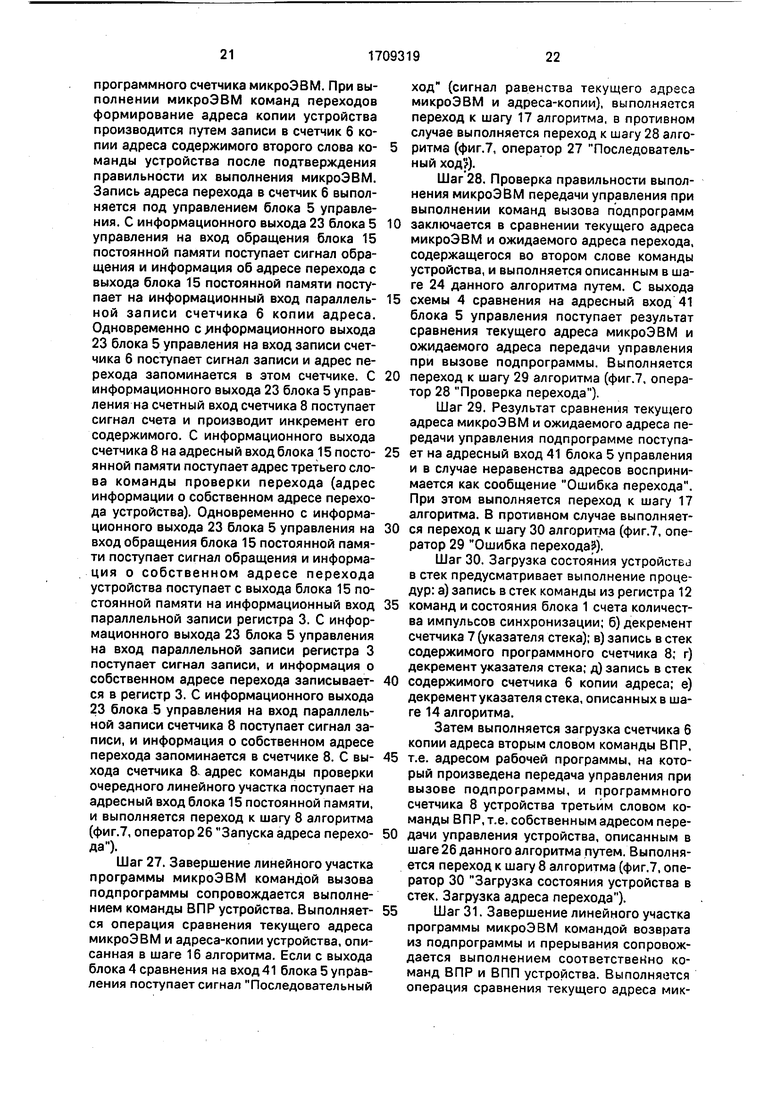

Временная диаграмма сигналов на информационных выходах блока 5 управления представлена на фиг. 8. Синхронизация работы блока 5 управления осуществляется

5 тактовыми сигналами, поступающими на его тактовый вход 21 (эпюра 72, фиг. 8). В каждом такте работы блока 5 управления на выходах программируемой логической матрицы 50 формируются сигналы управления (эпюра 73, фиг. 8) в соответствии со струкки линейного участка путем подачи сигналов с первого информационного выхода 23 блока 5 управления на счетный вход 44 блока 1 счета количества синхроимпульсов. Сигнал переполнения с выхода 43 признаков переполнения блока 1 счета количества импульсов синхронизации воспринимается на адресном входе 42 блока 5 управления как сообщение Конец линейного участке. При поступлении этого сигнала выполняется переход к шагу 20 алгоритма, в противном случае - к шагу 16 (фиг.7, оператор Конец линейного участка .

Шаг 16. Линейный участок программы, состоящий из команд последовательной цепи операций (команды пересылок, арифметические и логические операции, команды ввода, вывода, установки флагов и т.п.), микроЭВМ проходит путем инкремента программного счетчика микропроцессора. Содержимое программного счетч1 ка микроЭВМ устанавливается на шине адреса данных микроэвм в циклах обращения к памяти, содержащей контролируемую программу. Проверка правильности прохождения микроэвм линейного участка программы осуществляется путем сравнения текущих адресов обращения микроЭВМ к рабочей программе и синхронно изменяющегося адреса-копии, хранящегося в счетчике 6. Операция сравнения текущего адреса и адреса-копии и проверка правильности последовательного хода рабочей программы выполняется под управлением блока 5 управления. По сигналу синхронизации активного устройства микроЭВМ, поступающему на синхровход 29 устройства и далее (фиг.1) на вход параллельной записи регистра 2, текущий адрес микроЭВМ запоминается в этом регистре и с его выхода поступает на первый вход схемы 4 сравнения. Одновременное информационного выхода 23 блока 5 управления на вход разрешения коммутатора 9 поступает сигнал, разрешающий прохождение информации о состоянии счетчика 6 копии адреса на второй вход схемь 4 сравнения. Сигнал о результате сравнения с выхода схемы 4 сравнения поступает на адресный вход 41 блока 5 управления и воспринимается как сигнал Последовательный ход в случае равенства текущего адреса программы и адреса-копии. При этом выполняется переход к шагу 18 алгоритма. В противном случае выполняется переход к шагу 17 алгоритма (фиг.7, оператор 16 Последовательный ход).

Шаг 17. В случае, если в текущем машинном цикле установлено неравенство текущего адреса и адреса-копии, выполняется

инкремент счетчика дополнительных импульсов синхронизации. С информационного выхода 23 блока 5 управления на счетный вход 44 блока 1 счета количества импульсов

синхронизации и далее на счетный вход счетчика 49 дополнительных синхроимпульсов поступает сигнал, и содержимое этого счетчика увеличивается на единицу. Такая микрооперация выполняется каждый раз,

когда микроэвм выполняет циклы обращения к оперативному запоминающему устройству либо к внешним устройствам. Для микроэвм число обращений к внешним устройствам при выполнении, одной команды

ограничено максимальным значением. Система команд ДВК, например, допускает до четырех таких обращений в цикле выполнения некоторых команд (двухадресные команды косвенной адресации). Счетчик

дополнительных синхроимпульсов вырабатывает сигнал переполнения в случае, если в нём содержится максимально допустимое число дополнительных синхроимпульсов и выполняется его инкремент. Выполняется

переход к шагу 9 алгоритма (фиг.7, оператор 17 Инкремент количества дополнительных синхроимпульсов).

Шаг 18. В случае, если в текущем машинном цикле установлено равенство текущего адреса и адреса-копии, выполняется декремент счетчика количества импульсов синхронизации линейного участка. С информационного выхода 23 блока 5 управления на счетный вход 44 блока 1 счета количества импульсов синхронизации и далее на счетный вход счетчика 48 количества импульсов синхронизации линейного участка поступает сигнал, и содержимое этого

счетчика уменьшается на единицу. Такая микрооперация выполняется каждый раз, когда микроэвм выполняет циклы обращения к памяти программ. Одновременно, выполняется сброс счетчика 49 дополнительных синхроимпульсов блока 1 счета количества импульсов синхронизации путем подачи сигнала начальной установки с информационного выхода 23 блока 5 управления на вход 45 начальной установки блока 1

счета и далее на вход начальной установки счетчика 49. Одновременно производится инкремент счетчика 6 копии адреса путем подачи сигнала Инкремент копии адреса на счетный вход этого счетчика с информационного выхода 23 блока 5 управления. Выполняется переход к шагу 19 алгоритма (фиг.7, оператор 18 Сброс счетчика дополнительных синхроимпульсов. Декремент количества синхроимпульсов. Инкремент копии адреса).

/ Шаг 19. Производится повторная проверка условия окончания линейного участка описанным в шаге 15 алгоритма путем. Если выполняется условие Конец линейного участка, происходит переход к шагу 20 алгоритма, в противном случае - к шагу 9 (фиг,7, оператор 19 Конец линейного участка;).

Шаг 20. Выполняется декодирование команды, код которой поступает с информационного выхода регистра 12 команд на адресный вход 36 блока 5 управления, и в зависимости от этого кода выполняется переход к соответствующему шагу алгоритма:

при выполнении команды ПРД - к шгу

21алгоритма;

при выполнении команды ПБУ - к шагу

22алгоритма;

при выполнении команды ПУС - к шагу

23алгоритма;

при выполнении команды ВПР - к шагу 27 алгоритма;

при выполнении команд ВРП, ВПП - к шагу 31 алгоритма;

при выполнении команды РДИ - к шагу 2 алгоритма (фиг.7, оператор 20 Команда).

Шаг 21. Завершение линейного участка программы микроэвм командой последовательной цепи операций сопровождается выполнением команды ПРД устройства. Выполняется процедура сравнения текущего адреса микроэвм и адреса-копии устройства и проверка правильности последовательного хода рабочей программы. Работа устройства в режиме проверки правильности последовательного кода программы описана в шаге 16 данного алгоритма. Если с выхода блока 4 сравнения на вход41 блока 5 управления поступает сигнал Последовательный ход (сигнал равенства текущего адреса микроЭВМ и адреса-копии), выполняется переход к шагу 8 алгоритма, в противном случае выполняется переход к шагу 17 алгоритма (фиг.7, оператор 21 Последовательный ход ).

Шаг 22. Завершение линейного участка программы микроэвм командой безусловной передачи управления сопровождается выполнением команды ПБУ устройства. Выполняется операция сравнения текущего адреса микроЭВМ и адреса-копии устройства, описанная в шаге 16 алгоритма. Если с выхода блока 4 сравнения на вход 41 блока 5 управления поступает сигнал Последовательный ход (сигнал равенства текущего адреса микроЭВМ и адреса-копии), выполняется переход к шагу 17 алгоритма, в противном случае выполняется переход к шагу

24алгоритма (фиг.7, оператор 22 Последовательный ход).

I Шаг 23. Завершение линейного участка пр ограммы микроэвм командой передачи управления по условию сопровождается выпсвлнением команды ПУС устройства. Выполняется операция сравнения текущего адреса микроЭВМ и адреса-копии устройства описанная в шаге 16 алгоритма. Если с выхода блока 4 сравнения на вход 41 блока 5 управления поступает сигнал Последовате1ьный ход (сигнал равенства текущего адреса микроЭВМ и адреса-копии), выполняэтся переход к шагу 8 алгоритма, в проти JHOM случае выполняется переход к шагу 24 алгоритма (фиг.7, оператор 23 Последовательный ход).

Шаг 24. Проверка правильности выполнения микроэвм передачи управления заключается в сравнении текущего адреса микроэвм и ожидаемого адреса перехода, содержащегося во втором слове команды устройства и выполняется под управлением блока 5 управления. С информационного выхода 23 блока 5 управления на счетный вход программного счетчика 8 устройства поступает сигнал, производящий инкремент содержимого этого счетчика. С выхода счетчика 8 на адресный вход блока 15 постоянной памяти поступает адрес второго слова команды ПБУ (ПУС) устройства. Одновременно с информационного выхода 23 блока 5 управления на вход обращения блока 15 постоянной памяти поступает сигнал обращения и информация об ожидаемом адресе перехода линейного участка с выхода блока 15 постоянной памяти поступает на второй вход схемы 4 сравнения, на первый вход которой с выхода регистра 2 поступает информация о текущем адресе микроэвм. С выхода схемы 4 сравнения на адресный вход 41 блока 5 управления поступает результат сравнения текущего адреса микроэвм и ожидаемого адреса перехода. Выполняется переход к шагу 25 алгоритма (фиг.7, оператор 24 Проверка перехода).

Шаг 25. Результат сравнения текущего адреса микроЭВМ и ожидаемого адреса перехода поступает на адресный вход 41 блока 5 управления и в случае неравенства адресов воспринимается как сообщение Ошибка перехода. При этом выполняется переход к шагу 17 алгоритма. В противном случае выполняется переход к шагу 26 алгоритма (фиг.7, оператор 25 Ошибка перехода|1).

Шаг 26. При выполнении микроЭВМ команд последовательной цепи операций формирование адреса-копии процессора выполняется путем инкремента счетчика 6 копии адреса синхронно с инкрементом

турной таблицей переходов, реализующей алгоритм фиг. 7. Сигналы первой группы выходов (первый, второй и тpetий выходы) программируемой логической матрицы 50 поступают соответственно на управляющие входы первого дешифратора 52, на инверсный вход стробирования которого поступают тактовые сигналы с тактового входа 21 блока 5 управления. Выходы дешифратора 52 являются группой выходов управления приемниками информации информационного выхода 23. Сигналы на этих выходах представлены эпюрой 74, фиг.8. Инкремент программного счетчика 8 и изменение состояния счетчика 7 (указателя стека) осуществляется сигналами второй группы выходов (четвертый и пятый выходы) программируемой логической матрицы 50. Эти сигналы (эпюра 73, фиг. 8) поступают на управляющие входы второго 53 дешифратора, на прямой вход стробирования которого с тактового входа 21 блока 5 управления поступают тактовые сигналы (эпюра 72, фиг. В). Сигналы с выхода дешифратора 53 (эпюра 75, фиг.8) поступают на группу выходов управления счетчиками 7 и 8 информационного выхода 23 блока 5 управления. Сигналы третьей группы выходов (шестой, седьмой и восьмой выходы), программируемой логической матрицы 50 поступают соответственно на входы управления дешифратора 54, с выходов которого на соответствующие выходы третьей группы выходов управления источниками информации, информационного выхода 23 блока 5 управления поступают сигналы, представленные эпюрой 73, фиг. 8. Сигналы четвертой группы выходов (девятый-тринадцатый выходы) программируемой логической матрицы 50 (эпюра 73, фиг. 8) поступают на соответствующие входы обращения блока 13 оперативной памяти, управления счетом счетчика б копии адреса, начальной установки и управления счетом блока 1 счета количества импульсов синхронизации, и входят в состав информационного выхода 23 блока 5 управления. Сигнал (эпюра 73, фиг. 8) на четырнадцатом выходе программируемой логической матрицы является сигналом ошибки устройства. Двухфазная организация управления приемниками информации и счетчиками устройства позволяет совместить некоторые операции, предусмотренные схемой алгоритма работы блока 5 управления, и выполнить их за один такт работы

Использование изобретения позволяет контролировать шины управления микроЭВМ или программируемого контроллера, а также информационно-адресные шины.

обеспечивать быструю реакцию из возникшую ошибку (сбой или отказ; время реакции не превышает времени выполнения команды обращения к внешнему устройству),

предотвращать возможность аварии управляемого объекта путем устранения бесконтрольного блуждания микроэвм по программе в результате ошибки (сбоя или отказа). Использование изобретения предусматривает простой формальнь1й алгоритм подготовки служебной информации, отображающей рабочую программу пользователя в программу устройства для контроля и, следовательно, требует незначитель5 ных затрат для его использования в конкретных прикладных задачах. . Формула изобретения

5 оперативной памяти, блок ввода-вывода и :блок постоянной памяти, причем выход пер вого блока регистров подключен к первому информационному входу схемы сравнения, информационный вхоД первого блока регистров является информационным; входом устройства и подключен к входу-выходу адреса данных блока ввода-вывода, выход блока постоянной памяти, выходы Нервого, второго и третьего коммутаторов соединены с информационными входами второго блока регистров, блока счета количества импульсов синхронизации и регистра команд, информационным входом-выходом блока ввода-вывода, информационным входом0 выходом блока оперативной памяти и вторым информационным входом схемы сравнения, тактовый вход блока микропрограммного управления является тактовым входом устройства, группа выходов блока

5 микропрограммного управления соединена с входами записи первого и третьего счетчиков, второго блока регистров, блока счета количества импульсов синхронизации и регистра команд, входом блокировки первого

0 коммутатора, счетными входами первого, второго и третьего счетчиков, входом обращения для чтения-записи блока оперативной памяти, входами разрешения второго и третьего коммутаторов, входом обращения

5 для ввода-вывода блока ввода-вывода и входом обращения для чтения блока постоянной памяти, вход начальной установки устройства подключен к входам начальной установки второго счетчика и блока микропрограммного управления, синхровход устройства - к входу записи первого блока регистров, информационный выход первого счетчика соединен с информационным входом первого коммутатора, информационный выход второго счетчика подключен к адресному входу блока оперативной памяти, выход готовности, управляющий входвыход блока ввода-вывода соединены соответственно с первым входом условий блока микропрограммного управления и входом-выходом управления устройства, вход подтверждения прерывания устройства подключен к второму входу условий блока микропрограммного управления, выход второго блока регистров - к информационному входу третьего счетчика, выход которого - к адресному входу блока постоянной памяти и информационному входу второго коммутатора, информационный выход регистра команд соединен с входом кода операций блока микропрограммного управления и первым информационным входом третьего коммутатора, второй информационный вход которого подключен к информационному выходу блока счета количества импульсов синхронизации, отличающееся тем, что, с целью повышения быстродействия, информационный вход первого счетчика соединен с выходом блока постоянной памяти, синхровход устройства подключен к третьему входу условий блока микропрограммного управления, четвертый и пятый входы условий которого подключены соответственно к выходу схемы сравнения, выходу признака переполнения блока счета количества импульсов синхронизации, счетный вход и вход начальной установки которого подключены к группе выходов блока микропрограммного управления, выход которого является выходом ошибки устройства.

коммутатора образуют вход-выход адреса данных блока ввода-вывода, группа информационных входов второго регистра и группа выходов второго коммутатора информационный вход-выход блока вводавывода, выход дешифратора подключен к первому входу первого элемента И, выход которого соединен с информационным входом первого триггера, прямой выход которого подключен к первым входам второго и

третьего элементов И, выход второго элемента И - к первому входу первого элемента ИЛИ, входу разрешения первого коммутатора и входу установки второго триггера, выход третьего элемента И - к второму входу

первого элемента ИЛ И, к первому входу второго элемента ИЛИ и установочному входу третьего триггера, выход первого элемента ИЛИ, вторые входы первого, второго, третьего и первый вход четвертого элементов И и

синхровход первого триггера объединены и являются входом-выходом управления блока ввода-вывода, синхровходы второго и третьего триггеров соответственно подключены к входу параллельной записи второго

регистра и входу разрешения второго коммутатора, объединены и являются входом обращения блока ввода-вывода, а выходы второго и третьего триггеров объединены и являются выходом готовности блока вводавывода, инверсный выход первого триггера соединен с вторым входом четвертого элемента И, выход которого подключен к второму входу второго элемента ИЛИ, выход которого соединен с входом записи первого

регистра.

jilia 2k

ч1 li X J/

ttB

Lrx

33

Фиг. 2

Фиг.З

Продолжение таблицы

itS

/

9

J

Фиг.

Фиг.5

Фиг.6

Загрдзка еоет

еямия дстроаство в стек

Загрузка перехода

Нагрузка состояния устройства а стек

75

О

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР N21434439, кл.С 06 F 11/28, 1987. | |||

Авторы

Даты

1992-01-30—Публикация

1989-10-03—Подача