выходов устройства, выход десятого элемента И подключен к второму входу четвертого элемента И и к первым входам элементов И пятой группы, прямой выход второго триггера соединен .с первым входом седьмого элемента И, с первыми входами элементов И второй и третьей групп и с вторым входом первого элемента И, выход которого является другим индикаторным выходом устройства, инверсный выход второго триггера соединен с вторыми входами элементов И шестой группы, с вторым входом шестого, с первым входом девятого и с вторым входом одиннадцатого элементов И, выход одиннадцатого элемента. И подключен к первым входам элементов И четвертой группы, выход второго элемента И соединен с вторыми входами элементов И первой группы и седьмого элемента И, с первым входом пятого элемента И и с вторым входом девятого элемента И, выход которого подключен к второму входу третьего элемента И, входы элемента ИЛИ-НЕ соединены с выходом блока сравнения а выход - с вторым входом пятого элемента И, выход которого подключен к второму входу первого элемента ЗАПРЕ выход второго счетчика соединен с вторыми входами элементов И третьей группы и блока сравнения, а второй вход подключен к выходу элемента ИЛИ, второй вход второго элемента ЗАПРЕТ соединен с выходом первого .та ЗАПРЕТ, а выйод - с первым входом элемента ИЛИ, второй вход

которого подключен к выходу седьмого элемента И и второму входу второго триггера, первые входы элементов ИЛИ третьей группы подключены к выходам элементов И шестой группы, вторые входы - к выходам элементов И третьей группы, а выходы - к адресным входам накопителя, входы второго регисФра числа соединены с входами третьего регистра числа и с выходами .накопителя, а выходы - с первыми входами сумматоров по -модулю два группы, второй вход восьмого элемента И подключен к последнему выходу накопителя, выход - к входу третьего триггера,инверсный выход которого соединен с вторыми входами сумматоров по модулю два группы и с третьим входом четвертого элемента И, третьи входы элементов liJlli первой группы под1сшочены к выходам элементов И пятой группы, второй вход последнего элемента И которой соединен с выходом четвертого элемента И, вторые входы элементов И пятой группы, кроме последнего, соеди-нены с выходом третьего счетчика, выходы сумматоров по модулю два группы подключены к третьим входам -элементов И первой группы и вторым входам элементов И четвертой группы, выходы которых подкл1оче1в 1 к вторым входам элементов ИЛИ второй- группы, выходы элементов И первой группы являются информационными выходами устройства и соединены, кроме последнего элемента И, с вторьми входами элементов И второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1982 |

|

SU1034070A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1130897A2 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1088073A2 |

| Запоминающее устройство с обнаружением ошибок | 1985 |

|

SU1277215A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

| Запоминающее устройство с обнаружением ошибок | 1984 |

|

SU1164791A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК, содержащее накопитель, регистры числа с первого по третий, первую и вторую группы элементов ИЛИ, сумматоры по модулю два с первого по третий, элементы И с первого ПО третий, первую и вторую группы элементов И, счетчики с первого по третийJ элемент ИЛИ, причем выходы третьего регистра числа соединены с входами второго элемента И, а входы подключены к выходам накопителя, первые входы элементов МШ первой группы соединены с выходами второго регистра числа, вторые входы элементов ИЛИ первой группы и первые входы элементов ИЛИ второй группы являются информационными входами устройства, а выходы элементов ШШ первой группы подключены к входам первого регистра числа, выходы которого соединены с информационными входами накопителя, -входы первого и второго сумматора по модулю два подключены соответственно к выходам первого счетчика и к выходам элементов ИЛИ второй группы, а выходы - к входам третьего сумматора по модулю два, выход которого соединен с первым входом третьего элемента И, первый вход третьего счетчика подключен к выходу третьего элемента И,второй вход - к выходам элементов И второй группы, первый вход первого счетчика является адресным входом устройства, первью входы второго, счетчика и первого элемента И являются одним из управлякяцих входов устройства, отличающеес я тем, что, с целью повышения быстродействия устройства, в Него введены третья группа элементов ИЛИ, элементы И с четвертого по одиннадцатый, группы элементов И с третьей по шестую, с первого W по третий триггеры,, блок сравнения, первый и второй элементы ЗАПРЕТ элемент Ш1И-НЕ и группа сумматоров по модулю два, причем первый вход шестого элемента И соединен с одним из управляющих входов устройства, а выход подключен к пер « ел вому входу первого элемента ЗАПРЕТ и к второму входу первого счетчика, выход которого соединен с первыми .й входами элементов И шестой группы и с первым входом блока сравнения, вход первого и первый вход второго триггеров и первый вход восьмого элемента И является другим управляющим входом устройства, прямой выход первого триггера соединен с первыми входами второго элемента ЗАПРЕТ одиннадцатого элемента И, элементов И первой группы и четвертого элемента И, а инверсный выход - с первым входом десятого элемента И, второй вход которого и выход блока сравнения являются одним из индикаторных

Изобретение относится к вычислит тельной технике, точнее к запоминающим устройствам с записью-счиТьшанием массивов информации.

Известно запоминающее устройство с обнаружением ошибок, содержащее накопитель, адресный, входной информационный и выходной информационшлй регистры, первый и второй блоки сверток по модулю два, сумматор, счетчик, вычитатель, контрольный регистр и элементы ИЛИ tl3«

i Недостатками этого устройства являются невозможность контроля более чем одного массива информации, большое количество оборудования и низкЬе быстродействие.

Наиболее близким к предлагаемому является запоминающее устройство с обнаружением ошибок,содержащее накопитель, регистр слова, адресный и выходной регистры, первую и вторую группы элементов Ш1И, первый и третий сумматоры по модулю два, первый элемент И, первую группу элементов И

реверсивный счетчик, первый и второй счетчики, дополнительный регистр, , второй и третий элементы И, вторую группу элементов И и элемент ИЛИ, причем входы накопителя подключе- 5 пы к выходам регистра слова и адресного регистра, выходы выходного регистра соединены с первыми входами элементов ИЛИ и И, выходы первьпс групп элементов ИЛИ второй группы 10 подключены к входу регистра слова, входы первого и второго сумматоров

по модулю два подключены соответственно к входу адресного регистра и к выходам элементов ИЛИ первой груп 15 пы, выходы первого и второго суыматоров по модулю два соединены с Iвходами третьего сумматора по модулю два, первый вход первого элемента И подключен к выходу третьего 20 сумматора по модулю два, а выход соединен с одним из входов реверсивного счетчика, второй вход которого соединен с выходами элементов И первой группы, а выход подключен к 25 третьему входу элементов ИЛИ второй группы, вторые входы элементов ИЛИ первой и второй групп подключены к информационному входу устройства. Вторые входы элементов И первой зо группы подключены к первому управля-.

ющему входу, первые входы элементов И второй группы соединены с шиной . второго управляющего сигнала, вторые входы - с входами дополнитель- 35 ного регистра и выходаьш накопителя, а выходы подключены к вхоДу выходного регистра, выходы дополнительного регистра соединены с входами третьего элемента И, вьзход которого до подключен к вторым входам первого И; второго элементов и, первый вход второго элемента И соединен с входом первого счетчика и с шиной третьего управляющего сигнала, а вьпсод - с 45 первым входом второго счётчика, второй вход которого является дополнительным входом устройства, а выходы соединены с входами элемента ИЛИ, выход которого является до- 50

полнительным выходом устройства, втЪрые входы первого счетчика подключены к адресному входу, а выход у. входу адресного регистра, первые входы элементов ИЛИ второй группы55 соединены с первыми входами элементов ИЛИ первой группы и с выходами выходного регистра 123.

Однако в этом ус тройстве необходимо расходовать дополнительное вре|мя на восстановление информации в ячейках накопителя, с которых после проверки работоспособности считана информация потребителю. Таким образом, недостатком этого устройства является низкое быстродействие. Цель изобретения - повьшение быстродействия устройства.

Поставленная цель достигается тем, что взапоминающее устройство с обнаружением ошибок, содержащее накопитель, регистры числа с первого по третий, первую и вторую группы элементов ШШ, сумматоры по модулю два с первого по третий, элементы

,И С первого по третий, первую и вторую группы элементов И, счетчики с

первого по третий, элемент ИЛИ, причем выходы третьего регистра числа соединены с входами второго элемента И, а входы подключены к выходам накопителя, первые входы элементов ШШ первой группы соединены с вы ходами второго регистра числа,вторые входы элементов ИЛИ первой группы и первые входы элементов ИЛИ второй группы являются информационными входами устройства, а выходы элементов ШШ первой группы подключены к входам первого регистра числа,выходы которого соединены с информационными входами накопителя, входы первого и второго сумматоров по модулю два подключены соответственно к выходам первого счетчика и к выходам элементов ИЛИ второй группы, а выходы - к входам третьего сумматора по модулю два, выход, которого соединен с первым входом третьего элемента И, первый вход третьего счетчика подключен к выходу третьего-элемента И, второй вход - к выходам элементов И второй грзшпы, первый вход первого счетчика является адресным входом устройства, первые входы второго счетчика и первого элемента И являются одним из управляющих входов устройства, введены третья группа элементов И)Ш, элементы И с четвертого по одиннадцатый, группы элементов И с третьей по шестую, триггеры с первого по третий, блок сравнения, первый и

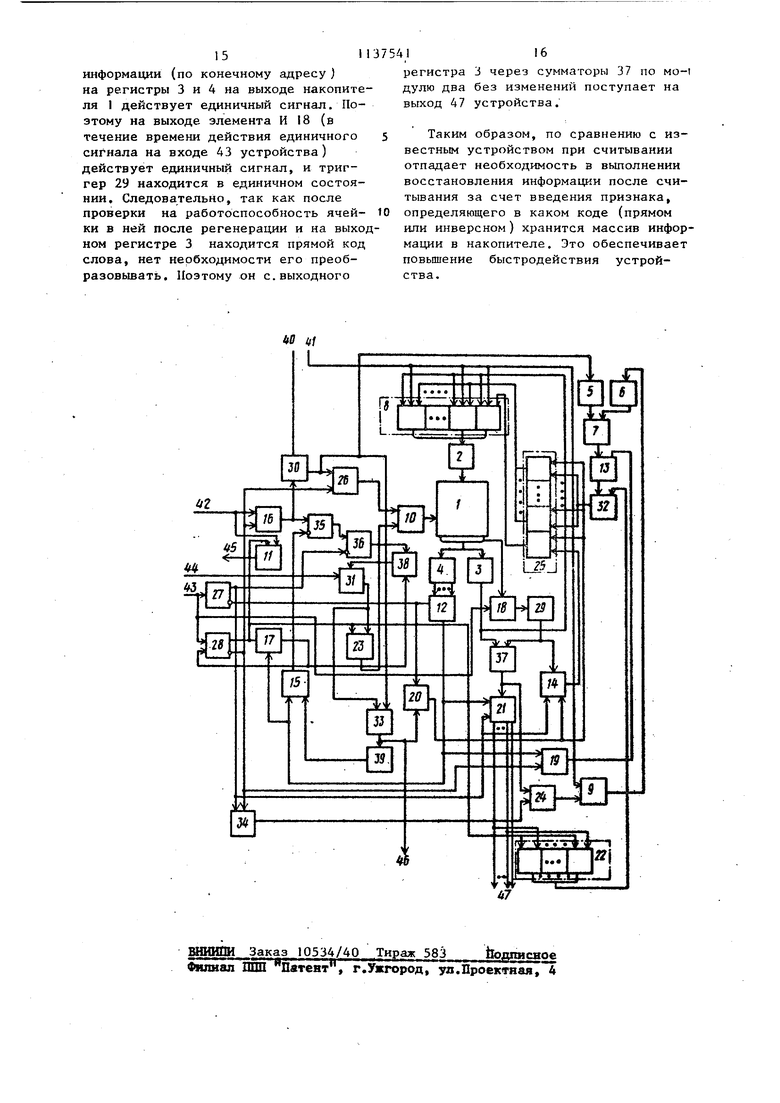

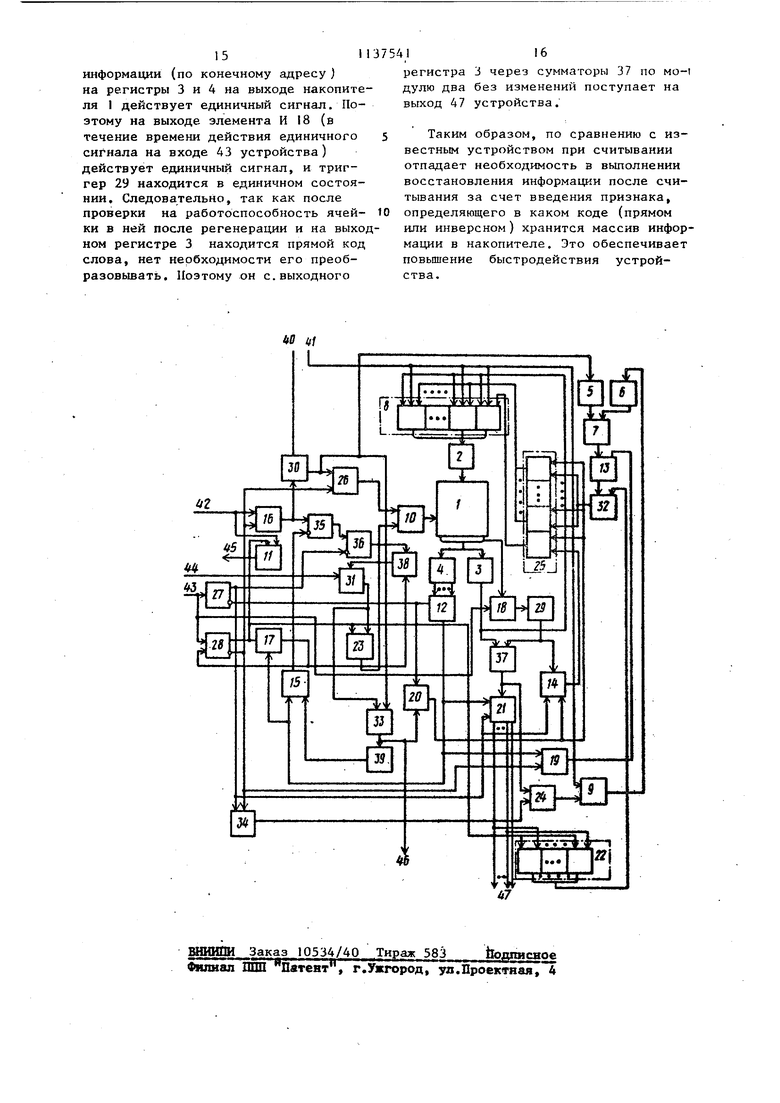

второй элементы ЗАПРЕТ, элемент ИЛИ-НЕ и группа сумматоров по модулю два,причем первый вход шестого элемента И соединен с одним из управляющих

.входов устройства, а выход подключен к первому входу первого элемента ЗАПРЕТ и к второму входу первого сче чика, выход которого соединен с пер выми входами элементов И шестой группы и с первым входом блока сравнения, вход первого и первый вход вт рого триггеров и первый вход восьмого элемента И являются другим упра ляющим входом устройства, прямой выход первого триггера соединен с первыми входами второго элемента ЗАПРЕТ, одиннадцатого элемента И, элементов И первой группы и четвертого элемента И, а инверсный выход с nepSbM входом десятого элемента И второй вход которого и выход блока сравнения являются одним из.индикаторных выходов устройства, выход десятого элемента И подключен к второму входу четвертого элемента И и к первым входам элементов И пятой группы, прямой выход второго триггера соединен с первым входом седьмого элемента И, с первыми входами элементов И второй и третьей групп и с вторым входом первого элемента И, выход которого является другим ин дикаторным выходом устройства, инверсный выход второго триггера соединен с вторыми входами элементов И лпестой группы, с вторым входом шестого, с первым входом девятого и с вторым входом одиннадцатого элементов И, выход одиннадцатого элемента И подключен к первым входам элемен тов И четвертой группы, выход второго элемента И соединен с вторыми в ходами элементов И первой группы и седьмого элемента И, с первьм вхоДОМ ПЯТОГО элемента И и с вторым входом девятого элемента И, выход которого подключен к второму входу третьего элемента И, входы элемента ШИ-НЕ соединеш 1 с выходом блока сравнейия, а вьпсод - с вторым входом пятого элемента И, выход кото рого подключен к второму входу перво го элемента ЗАПРЕТ, выход второго i: счетчика соединен с вторыми входами элементов И третьей группы и бло . ка сравнения, а второй вход подключен к выходу элементу ИЛИ,второй вход .. второго элемента ЗАПРЕТ соединен с выходом первого элемента ЗАПРЕТ, а выход - с первым входом элемента ИЛИ, второй вход которого подключен тк выходу седьмого элемента И и второму входу второго тригге416ра, первые входы элементов ИЛИ третьей группы подключены к выходам элементов И шестой группы, вторые входы - к выходам элементов И третьей группы, а выходы - к адресным входам накопителя, входы второго регистра числа соединены с входами третьего регистра числа и с выходами накопителя, а выходы - с первыми входами сз мматоров по модулю два группы, второй- вход восьмого элемента И подключен к последнему выходу го триггера, инверсньй выход которого соединен с вторыми входами сумматоров по модулю два группы и с третьим входом четвертого элемента И, третьи .входы элементов ШМ первой группы подключены к выходам элементов И пятой группы, второй вход последнего элемента И которой соединен с выходом четвертого элемента И, вторые входы элементов П пятой группы, кроме последнего, соединены с выходом третьего счетчика, выходы сумматоров по модулю два группы подключены к третьим входам элементов И первой 1руппы и вторым входам элементов И четвертой группы, выходь которых подключены к вторым входам элементов ИЛИ второй группы, выходы элементов И первой группы яв ляются информационными выходами устройства и соединены, кроме последнего элемента И, с вторыми входами элементов И второй группы. На чертеже изображена структурная схема предлагаемого устройства. Устройство содержит накопитель 1, первый 2,второй 3 и третий 4 регистры числа, первый 5, второй 6 и третий 7 сумматоры по модулю два, первую 8, вторую 9 и третью 10 группы элементов И-Ш, первый - десятый элементы И П-20,первую - шестую группы эле7 ментов И 21-26, первый 27, второй 28 и третий 29 триггеры, первьШ 30,второй 31 и третий 32 счетчики, блок 33 сравнения, одиннадцатый элемент И 34, первьй 35 и второй 36 элементы ЗАПРЕТ, группу сумматоров 37 по модулю два, элемент ИЛИ 38, элемент ИЛИ-НЕ 39. Устройство содержит также адресый вход 40, информационный вход 41, ервый 42, второй 43 и третий 44 упавляющие входы, первый 45 и второй 6 индикаторные выхода, информацинный выход 47 устройства. 71 Устройство работает следующим об разом. , Исходным состоянием, регистров 2-4, счетчиков 30-32 и триггеров 27 29 является нулевое. В сЦетчик 30 по входу 40 и в сче чик 31 по входу 44 принимаются соответственно адреса начала и конца массива информации, который необходимо записать в накопитель 1 или считать с него. В режиме записи адрес конца массива информации - это сумма начального адреса, и кода величины массива информации, в в режи ме считьшания - это адрес , ячейки накопителя 1, в которую записано по следнее слово массива информации. Обращение к ячейке накопителя 1 дл записи информации осуществляется по адресу, который формируется в счетчике 30, а для считьшания - по адресу , который формируется или в счетчике 30 или в счетчике 31..Режим работы устройства определяется сигналом, поступающим через вход 43 на входы первого 27 и второго 28 триггеров, причем нулевой сигнал соответствует режиму записи, а единичный - режиму считьшания информации с накопителя I. При записикаждого слова в накопитель 1 вьшолняются проверка ра ботоспособности ячейки накопителя 1 я запись в нее информации; формирование результирующего бита четности адреса и записьшаемого слова и запись его в счетчик 32; коррекция ко нечного адреса записьшаемого массива информации; формирование очередного адреса записи и обнуления регистра 4. Так как в режиме записи на входе 42 действует нулевой сигнал, то триггеры 27 и 28 не изменяют своего исходного состояния. В этом случае элемент, И 16 и элементы И 26 группы по одному, входу открыты, так как на инверсном выходе триггера 28 - единичный сигнал. При проверке работоспособности ячейки нако пителя 1 записываемое слово поступа ет на вход 41 и через элементы ИЛИ 8 принимает,ся в регистр 2. Инверсный код слова, снимаемый с инверсных выходов регистра2j записывается в ячейку накопителя 1 по адресу, содержащемуся в счетчике 30 и затем считываетсяi на регистры 1 -8 3 и 4. После этого осуществляется запись прямого кода слова (с прямых выходов регистра 2 ) в эту же ячейку накопителя 1 и его считьша- ние с одновременной регенерацией. Считанное слово выдается-- на регистры 3 и 4. На регистре 4 осуществляется поразрядное суммирование по модулю два инверсного и прямого кодов слова. Если ячейка накопителя 1, -в которую производилась зацись инверсного, а затем прямого кодов слова, работоспособна то все разряды регистра 4 устанавливаются в единичное состояние и на выходе элемента И I2 формируется единичный сигнал, свидетельствующий о работоспособности ячейки. В данном случае слово уже записано в требуемую ячейку памяти накопителя I. Одновременно с записью в накопитель 1 информационного слова адрес записи с выходов счетчика 30 поступает на первый сумматор 5 по модулю два, а записываемое слово - на входы второго сумматора 6. Сумматоры 5 и 6 формируют соответс:рвенно биты четности адреса и записьшаемого слова, которые объединяются сумматором 7 в результирующий бит четности адреса и записьшаемого слова. При появлении единичного сигнала на выходе элемента И 12 (когда ячейка работоспособна), он через открытый элемент И 19 (так как на другом входе элемента И 19 действует единичный сигнал с инверсного выхода триггера 28) действует на вход элемента И 13 и открывает его. Через открытый элемент И 13 результирующий бит четности псступает на вход, счетчика 32,,; При записи счетчик 32 работает в режиме суммирования, поэтому к его содержимому прибавляется значение результирующего бита четности адреса и записываемого слова. Кроме того, единичный сигнал с выхода элемента И 12 поступает на вход элемента И 15. Так как до записи в накопитель 1 последнего слова массива информации на выходе блока 33 действует нулевой, а на выходе элемента ИЛИ-НЕ 39 - единичный сигналы, едиичным сигналом, действуннцим на выходе элемента И 15, элемент ЗАПРЕТ 35 закрьшается. При этом пришедамй на вход 42 устройства едасничный сигнал проходит через открытый элемент И 16 и действует только на второй вход счет шка 30, увеличивая.-его значение на единицу, т.е. формирует адрес для за писи в накопитель 1 очередного елова информахщн. Увеличение начального адреса при неизменном конечном адресе (при появлении единичного сигнала на входе 42) свидетельствует о том, что в накопитель 1 записано очередное слово. Далееосуществляется аналогичным образом запись и других слов поступившей инфо мации . Если в проверяемой ячейке накопи теля 1 неисправен какой-либо разряд то значения считьюаемого из -него пр мого и инверсного сигналов одинаковы Поэтому содержимое соответствующего ему разряда регистра 4 равно нулю и на выходе элемента И 12 формирует ся нулевой сигнал, свидетельствующи р неработоспособности ячейки. Этот сигнал действует на вход элемента И 19 и закрывает его. и соответствен но элемент И 13 и запрещает запись результирующего бита четности адреса и записываемого слова в счетчик Кроме того, наличие нулевого сигнала.на выходе элемента И 12 (ячей ка неработоспособна) приводит к то- у, что нулевой сигнал появляется на выходе элемента И I5, а соответственно и на запретном входе элемента ЗАПРЕТ 35. В данном случае пр шедший на вход 42 единичный сигнал поступает как на вход счетчика 30, так и через открытые элементы ЗАПРЕТ 35 и 36 (на запретном входе элемента ЗАПРЕТ 36 действует нулевой сигнал с прямого выхода триггера 27) на вход счетчика 31. Содержимое счетчиков 30 и 31 увеличивается, на единицу, т.е. форм руется новый адрес записи очередного слова информации и меняется койачный адрес записи всего массива информации. Увеличение конечного адреса записи (Свидетельствует о том, что очередное слово в накопитель 1 не записано и по новому на- |Чальному адресу осуществляется про верка соответствующей ячейки накопи теля 1. Если проверяемая ячейка раб тоспособна, то в нее с регистра 2 з писывается слово, которое должно был быть записано в предвдущую (неработоспособную ) ячейку, т.е. осуществл ется обход неработоспособной ячейки Запись продолжается до тех пор, пока в накопитель 1 не будет записан весь массив информации, а также сопроволщающие этот массив контрольная сумма битов четности и признак кода хранимой в накопителе информагщи, т.е. пока текущий адрес записи на станет равным конечному адресу записи массива информации. При равенстве текущего и конечного адресов на выходе блока 33 сравнения, а соответственно и на выходе 46 устройства формируется единичный сигнал. Счетчик 32 фиксирует при этом количество результирующих битов, равных единице, а на выходе элемента И 14 появляется сигнал, определяющий признак типа кода хранимой в накопителе 1 информации. Признак типа кода показьшает, в каком (прямом или инверсном) коде хранится информация в накопителе 1 после ее записи туда или считьшания оттуда, причем, если признак равен 1, то информация в накопителе хранится в инверсном коде, а если О - в прямом. Так как при записи информации .на входе элемента И 14 действует нулевой сигнал, то независимо от того, какие сигналы действуют на других его входах, на выходе действует нулевой сигнал, показывающий, что после записи информации в н:акопитель Г она там хранится только в прямом коде. Таким образом, в накопитель 1 записывается с обходом неработоспособных ячеек массивов информации и соответствунщие ему контрольная сумма и признак типа кода, показывающий в каком виде Хранится информация в накопителе 1. В режиме за писи информация на выход 47 уст ройства не поступает, так как элементы И 21 закрыты нулевым сигналом с вьйсода триггера 27. Перед считыванием массива информации, так же как и при записи,регистры 2-4, триггер .29 и счетчик 32 обнуляются. Кроме того, в режиме считывания на вход 43 устройства поступает единичный сигнал, под действием которого триггеры 27 и 28 устанавливаются в единичное состояние. В этом случае под действием единичного сигнала с прямого и нулевого сигнала с инверсног о выхода триггера 28 элементы И 23 открываются, а элементы И 26 закрываются. Поэтому обращение к накопителю 1 сначала происходит по конечному адре су, который перед началом работы заносится в счетчик 31 через вход 44 Последнее слово массива информации, где находится контрольная cyi«iMa с признаком, считывается с накопителя 1 на регистры 3 и 4, а затем с регистра 3 через элементы ИЛИ 8 - на регистр 2,Но«в течение времени записи информации с. накопителя 1 на регистры 3 i# 4, на последнем выходе накопителя 1 действует сигнал, определяю щий признак типа кода хранимой в нак пителе 1 информации. Этот признак хранится в последнем разряде последнего слова массива информации. Рассмотрим работу устройства, ког да этот признак равен О, т.е. информация в накопителе 1 хранится в прямом коде. В этом случае при считывании слова на регистры 3 и 4 по конечному адресу массива, находящемуся в счетчике 31, на один вход элемента И 18 действует нулевой сигнал. Поэтому, независимо от того, ка кой сигнал действует на другом его входе, на выходе действует нулевой сигнал и, следовательно, триггер 29 тоже находится в нулевом состоянии, После этого действие единичного сигнала на входе 43 устройства прекращается и независимо от того, какой сигнал присутствует НА первом входе элемента И 18, триггер 29 до. конца считьшания слов массива информахщи своего состояния не изменяет, В дальнейшем инверсный код слова, снимаемый с инверсных выходов Р1егистра 2, записьшается в эту. же ячейку накопителя I (в ячейку, с которой было считано последнее слова массива) и затем снова считывается на регистры 3 и 4 (с одновременной регене1)ацией) ,т,е, происхо дит, как и при записи информации, проверка работоспособности ячейки. Если ячейка оказывается работоспособной, то на выходе элемента И 12 появляется единичный сигнал, под действием которого преобразованный с помощью сумматоров 37 по модулю два HiiBepcHb код последнего слова в пря мой (так как на вторых входах .сумматоров действует единичный сигнал с инверсного выхода триггера 29 ) посту пает на выход 47 устройства; контрольная сумма через элементы И 22 , записьшается в счетчик 32; на выходе элемента И 17 появляется единичный .сигнал, который действует на вход (вход установки в О ) триггера 28 и устанавливает его в нулевое состояние, а также проходит через элемент ШШ 38 на вход счетчика 31 и уменьг шает его значение на единицу (счетчик 31 является реверсивным и при считывании работает в режиме вычитания ). . Установка триггера 28 в нулевое состояние приводит к тому, что элементы И 26 открываются, -а элементы И 23 закрываются. Этим подготовительные операции перед считыванием непосредственно информационных слов с накопителя I заканчиваются. Если ячейка накопителя, где хранится контрольная сумма с признаком типа хранимой информации, оказьшается неработоспособной, то триггер 28 своего состояния не меняет и с приходом единичного сигнала ма вход 42 на входе 45 устройства появляется единичный сигнал. Он показьшает, что необходимо принять меры для восстановления информации в ячейке, где хранится контрольная сумма с признаком типа ...информации, или осуществлять считывание массива информац11и без признака и контрольной суммы. При считывании каждого слова из накопителя 1 (в случае, когда ячейка с контрольной суммой и признаком типа информации оказывается работоспособной) по адресу, содержащемуся в счетчике 30, выполняются следующие действия: проверка работоспособности ячейки накопителя 1, с которой считывается слово; формирование резуль. тирующего бита четности адреса и считьшаемого слова и вычитание его из содержимого счетчика 32j формиро- ; вание очередного адреса считывания и обнуление регистра 4. Так как элементы И 26 открыты,считывание информационных слов массива осуществляется по адресу, хранящемуся в счетчике .30. При проверке работоспособности ячейки производится считьгоание содержащегося в ней прямого кода слова (так как признак типа кода информации равен О ) и вцдача его на регистры 3 и 4,С регистра 3 131 считанное слово через элементы ШИ 8 поступает на регистр 2, Инверсный код слова с выходов регистра 2 записывается в эту же ячейку накопителя 1 (в ячейку, с которой было считано слово ) и затем считьшается на регист ры 4 и 3 (с одновременной регенерацией ), На регистре 4 осуществляется поразрядное суммирование по модулю два инверсного и прямого кодоз слова. Если ячейка накопителя, с которой считьшался прямой, а затем инверсный, коды слова, работоспособна, то все разряды регистра 4 устанавливаются в единичное состояниа и. на вькоде элемента И П формируется единичный сигнал, свидетельствующий о работоспособности ячейки Одновременно с проверкой на работоспособность ячейки накопителя адрес считывания из счетчика 30 выдается на сумматор 5, а считываемое слово с выходов сумматоров по модул два через элементы И 24 и элементы ИЛИ 9 поступает на сумматор 6. Сумма торы 5 и 6 формируют соответственно биты четности адреса и считываемого слова, которые объединяются сумматором 7 в результирующий бит четности. Если ; чейка работоспособна, то считанное слово вьщается через сумматоры 37 по модулю два и элементы И 21 на вькод 47 устройства. Кро ме того, по единичному сигналу с выхода элемента И 12 н соответствен с -выхода элемента И 19 результирующий бит четности через элемент И 13 вьздается на вход счетчика 32, При считьшанйи. счетчик 32 работает в ре жиме вычитания, поэтому из его содержимого вычитается значение результирующего бита четности. При появлении единичного сигнала на входе 42 он через элемент И 16 поступает на счетчик 30 и увеличива ет его содержимое на единицу, т.е. формирует новый адрес обращения к н копителю 1 . Содержимое счетчика 3 остается неизменным, Если в ячейке накопителя 1 неисп равен какой-либо разряд, то значение считьшаемого из него сигнала од{шаково как в прямом, так и в инверсном значениях.Поэтому содержимое соответствующего ему разряда регистра 4 равно нулю и на выходе 114 элемента И 12 формируется нулевой сигнал, свидетельствующий о неработоспособности ячейки. Этот сигнал запрещает запись результирую1Чего бита четности адреса и записы-. ваемого слова в счетчик 32, так как на выходе элемента И 19 действует нулевой сигнал. В данном случае считанное с регистра 4 слово на выход 47 не выдается, и по единичному сигналу с входа 42 содержимое счетчика, а соответственно и адрес считьшания, увеличиваются на единицу, осуществляется проверка соответствующей Ячейки накопителя 1 и в случае ее работоспособности считывание последующего слова, т.е. осуществляется обход неработоспособной ячейки. Считывание информации продолжается до тех пор, пока последний информационный элемент массива не будет считан с накопителя 1. При этом содержимое счетчика 30 и 31 становится одинаковым м на выходе блока 33, а соответственно и на выходе 46, формируется единичный сигнал. Если в процессе считывания информации в устройстве возникают ошибки, не связанные с неисправностью ячеек памяти, то счетчик 32 фиксирует количество ошибок и, если их много, считывание информации можно производить повторно. При этом в счетчик 32 предварительно вновь записывается контрольный код. После считывания информации,хранящейся в накопителе I в прямом коде, информация в нем остается, но в инверсном коде. В инверсном коде представляется и контрольная сумма с признаком типа хранимой информации,который в этом случае равен 1. В этом случае работа устройства аналогична работе устройства при . считывании информации с накопителя 1, когда признак кода хранимой информации равен нулю. Только при проверке ячейки на работоспособность на регистры 3 и 4 сначала считывается не прямой, а инверсный код слова, и с инверсных выходов регистра 2 (после записи на этот регистр инверсного кода слова с выходов регистра 3 ) в проверяемую ячейку и с нее снова на регистры 3 и 4 принимается не инверсный, а прямой код слова. Кроме того, при считывании инверсного кода слова с контрольной суммой и признаком типа хранимой информации (по конечному адресу ) на регистры 3 и 4 на выходе накопите ля I действует единичный сигнал. Поэтому на выхода элемента И 18 (в течение времени действия единичного сигнала на входе 43 устройства) действует единичный сигнал, и триггер 29 находится в единичном состоянии. Следовательно, так как после проверки на работоспособность ячейки в ней после регенерации и на выхо ном регистре 3 находится прямой код слова, нет необходимости его преобразовьшать. Поэтому он с.выходного 1 116 регистра 3 через сумматоры 37 по мо-1 дулю два без изменений поступает на выход 47 устройства. Таким образом, по сравнению с известным устройством при считывании отпадает необходимость в вьтолнении восстановления информации после считывания за счет введения признака, определяющего в каком коде (прямом или инверсном) хранится массив информации в накопителе. Это обеспечивает повышение быстродействия устройства.

Авторы

Даты

1985-01-30—Публикация

1983-11-14—Подача