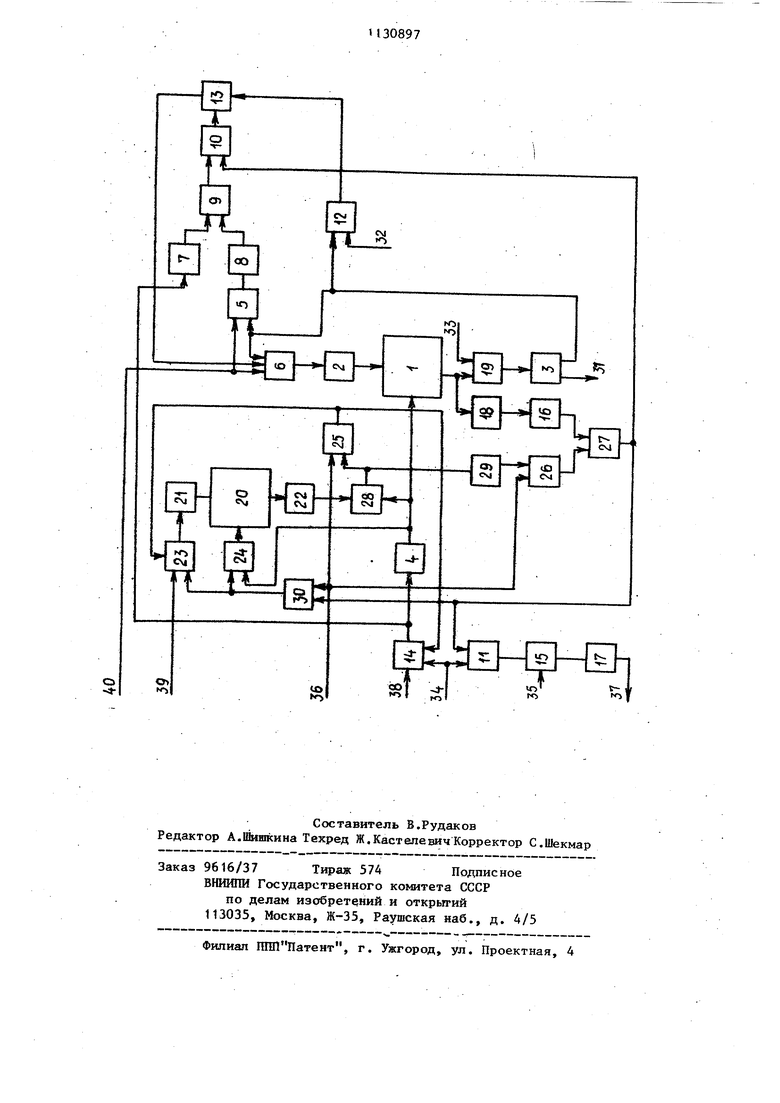

Изобретение относится к вычислительной техни се, в частности к запо.микающим устройствам. По основному авт. св. № 1034070 известно запоминакщее устройство с обнаружением ошибок, содержащее наксшитель, регистры,-сумматоры по модулю два, счетчики иютульсов, группы элементов ИШ и элемент ИЛИ, группы элементов И и элементы И, причем первые входы элементов И первой груп пы являются одним из управляющих входов устройства, первые входы элементов ШШ первой и второй групп соответственно объединены и являются информам;ионными входами устройства, вьвсоды элементов ИЛИ второй группы подключены к входам первого регистра, выходы которого соединены с инфс мационньши входам : накопителя, один из выходов второго регистра подключен к вторым входам элементов ИШ первой группы и вторьм вхог, дам элементов И первой группы, выхода которых соединены с одним из входов первого счетчика импульсов, другой вход которого подключен к выходу первого элемента И, а вькод - к вторьн4 входам элементом ИЛИ второй , адресные входы наксшителя со единены с выходами третьего регистра входа первого и второго сумматоров по модулю два соединены соответственно с BXotqaMH третьего, регистра и с выходами элементов ИЛИ первой груп пы, а выходы подключены к входам тре тьего сумматора по модуло два, выход которого соединен с первьм входом первого элемента И, другие в жоды второго регистра являются инфорMaiQioHHtASfli выхода1 ш устройства, первые входа элементов И второй группы Соединены с .входают четвертого регистра и выходагШ накопягеяя а выходы - с входами второго регистра, выходы второго счетчика шЛгульсов йодключеиы к входам третьего регистра, а один из васрдов соединен с первым входом второго элемента И, второй вход которого подключен к втсфому входу первого элемента И и вьиоду третьего элемента И, входы которого соединены с выходами четвертого регистра, выход второго элемента И подключен к первому входу третьего счетчика импульсов, выходы которого соединены с входами элемента ИЛИ, выход которого является индикаторным выходом устройства, другие входы вто рого счетчика имцульсов являются адресными входами .устройства, другими управляющими входами которого являются вторые входа элементов И второй групггы, первый вход второго элемента И и второй вход третьего счетчика импульсов, третьи входы элементов ИЛИ второй группы подключены к выходам второго регистра }. В этом устройстве при записи и считьгоании каждый раз проверяется состояние накопителя и производится обход неработоспособных ячеек. При записи слова последовательно осуществ,-, ляется запись инверсного кода в накопитель, считывание его, запись прямого коДа и также считывание. Это позволяет осуществить контроль работоспособности данной ячейки. Если данная ячейка неработоспособна, запись dnoBa производится аня.логично в следующую ячейку. При считывании слова последовательно осуществляется считывание прямого кода слова из накопителя, запись в накопитель инверсного кода слова, считьюание его, т.е. контролируется работоспособность ячейки. Если ячейка работоспособна, слово выдается на выход устройства и в накопитель записывается прямой код. Если неработоспособна, считывание осуществляется из следующей ячейки. Таким образом, недостатком известного устройства является низкое быстродействие при считывании данных. Цель изобретения - повышение быстродействия устройства; Поставленная цель достигается тем, что в запоминающее устройство с обнаружением опшбок введены дополнительный накопитель, пятый и шестой регистры, четвертый счетчик импульсов, третья группа элементов И, четвертьй и пятый элементы И, второй элемент ИЛИ, блок сравнения, элемент НЕ и элемент ИГШ-НЕ, причем первый вход четвертого счетчика импульсов является другим адресным входом устройства, входы пятого регистра соединены с вькодами четвертого счетчи , ка импульсов, а выходы подключены к адресным входам дополнительного накопителя, информационные вход.: которого соединены с выходами элементов И третьей ггуппы, а выходы - с входами шеечного регистра, выходы которого подключены к одним из входов блока сравнения, другие входы которого соединены с первыми входами эл ментов И третьей группы и с выходами третьего регистра, а выход соединен с входом элемента НЕ и с.первым вхо дом четвертого элемента И, выход которого подключен к третьему входу второгб счетчика импульсов и второму входу четвертого счетчика импульсов, третий вход которого соединен с вторьа Е входами элементов И третьей группы и с выходом элемента ИЛИ-НЕ, первый вход которого, второй вход четвертого элемента И и первый вход пятого элемента И являются одним из управляющих входов ус ройства, второй вход пятого элемента И соединен с выходом элемента НЕ, а выход - с одним из входов вто рого элемента ИЛИ, выход которого подключен к вторым входам первого и второго элементов И и к второму вхо ду элемента-ШИ-НЕ. На чертеже представлена структур ная схема предлагаемого устройства. Устройство содержит накопи-тель 1 первый 2, второй 3 и третий 4 регист рь1, первую 5 и вторую 6 группы элементов ИЛИ, первый 7 второй 8 и тре тий 9 сумматоры по модулю два, первы 10 и второй 11 элементы И, первую группу элементов И 12, первый 13, второй 14 и третий 15 счетчики импул сов, третий элемент И 16, первый эле мент ИЛИ 17, четвертый регистр 18, вторую группу элементов И 19, дополнительный накопитель 20, пятый 21 и шестой 22 регистры, четвертый счетчик 23 импульсов, третью группу элементов И 24, четвертый 25и пятый 26 элементы И,второй элемент ИЛИ 27 блок 28 сравнения, элемент НЕ 29 и элемент .ИЛИ-НЕ 30. Устройство также содержит информационный выход 31, первый 32, второй 33, третий 34, четвертый 35 и пятый 36 управляющие входы, индикаторный выход 37, первый 38 и второй 39 адресные и информационный 40 входы.. Счетчик 13 выполнен реверсивным. Устройство работает следующим образом. В исходном состоянии регистры 2, 3, 4, 18, 21 и 22, счетчики 13, 14 и 23 установлены в нулевое состояние В счетчик 13 по входу 35 записывается код веаичикы массива инфоря ации,который необходимо записать в нако974питель 1 или считать с него, а в счетчик i4 по входу 38 принимается адрес начала массива в накопителе 1. Обращение к ячейке накопителя 1 для записи или считывания информации осуществляется по адресу, который . формируется в счетчике 14, а затем выдается в регистр 4, а обращение к ячейке дополнительного накопителя 20 по адресу, который формируется в счетчике 23 и вьщается на регистр 21. В режиме записи в счетчик 23по входу 39 принимается адрес начала свободных ячеек накопителя 20, а на управляющий вход 36 подается нулевой сигнал. . При записи каждого слова в накопитель 1 выполняются следую(щие операции: проверка работоспособности ячейки накопителя 1 и запись в нее информации, формирование результирующего бита четности адреса и записываемого слова и запись его в счетчик 13, коррекция кода величины массива информации, формирование очередного адреса записи и установка в ну-. левое состояние регистра 18. При проверке рабогвспособности ячейки накопителя 1 записываемое ело- .во поступает по входу 40 через группу , элементов ИШ 6 на регистр 2. Инверсный код слова q регистра 2 записывается в ячейки накопителя 1 по адресу, содержащемуся в регистре 4, а затем считывается на регистр 18. После этого осуществляется запись прямого кода слова в эту же ячейку накопителя 1 и его считывание с одновременной регенерацией. Считанное слово вьщается на регистр 18 и через груп пу элементов И 19 - на регистр 3. На регистре 18 осуществляется поразрядное суммирование по модулю два.инверсного и прямого кодов слова. Если ячейка накопи- еля 1, в которую произведена запись инверсного, а затем .прямого кодов слова, работоспособна, все разряды регистра 18 устанавливаются в единичное состояние и на выходе элемента И 16 и элемента ИЛИ 27 формируется единичный сигнал, св1здетельствующий о работоспособности ячейки. В.данном случае слово уже записано в требуемую ячейку памяти. Одновременно с записью в накопитель 1 адрес записи из счетчика 14 выдается на сумматор 7, а записываемое слово по входу 40 через элементы S ИЛИ 5 - на сумматор 8, где формируют ся биты четности адреса и записываемого слова, которые объединяются сум матором 9 в результирующий бит четности. Если ячейка работоспособна,, то по единичному сигналу с выхода элемента ИЛИ 27 результирукщий бит четности через элемент И 10 поступает на вход счетчика 13. При записи счетчик 13 работает в режиме суммирования, поэтому к содерясимому счетчика 13 прибавляется значение резуль тирующего бита четности. Кроме того, единичный сигнал с выхода элемента ИЛИ 27 поступает на вход элемента И 11 и разрешает коррекцию кода величины массива. Коррекция осуществляется с помощью управляющего сигнала, поступающего по входу 34 через элемент И It на вход счетчика 15. Счетчик 15 всегда работает в режиме вычитания, поэтому его значение уменьшается на единицу после записи одного слова, .Управляющий сигнал с входа 34 поступает также на счетчик 14 и увеличивает его значение на единицу, т.е. формирует адрес очередного слова, который вьщается в регистр 4. Да лее осуществляется аналогично рассмотренному запись очередного слова Если в проверяемой ячейке накопи теля 1.неисправен хотя бы один разряд, значение считываемого из него сигнала является одинаковым как в прямом, так и в инверсном значениях слова. ПОЭТОМУ содержимое соответст вующего ему разряда регистра 18 равно нулю и на выходе элемента И 16 и элемента И 27 формируется нулевой сигнал (поскольку элемент И 2 в режиме записи постоянно закрыт уп равляющим сигналом с входа 36), сви детельствующий о неработоспособност ячейки. Этот сигнал запрещает запис результирующего бита четности адрес и записываемого слова в счетчик 13 и коррекцию кода величины массива в счетчике 15, а также вырабатывает на выходе элемента ИЛИ-НЕ 30 единич ный сигнал, который разрешает запис адреса неработорпособной ячейки накопителя 1 через группу элементов И 24 в дополнительный накопитель 20 увеличивает на единицу значение в счетчике 23, т.е. формирует адрес очередной -ячейки дополнительного на 97 копителя 20, который вьщается на регистр 21. По управляющему сигналу с входа 34 адрес записи в счетчике 14 увеличивается на единицу, осуществляется проверка соответствующей ячейки накопителя 1 и в случае ее работоспособности - запись с регистра 2 слова, которое должно бьио быть записано в предьщущую (неработоспособную) ячейку, т.е. осуществляется обход неработоспособной ячейки. Запись продолжается до тех пор, пока весь массив информации не за-пишется в накопитель 1. При этом содерз симое счетчика 15 становится равным нулю и на выходе 37 формируется нулевой сигнал. Счетчик 13 зафиксирует количество результирующих битов, равных единице. Зафиксированное счетчиком 13 число через элементы ИЖ 6 подается на регистр 2 и записывается в накопитель 1.Таким образом, в накопитель 1 записан с обходом неработоспособных ячеек массив данных и соответствующий ему контрольный код, а в дополнительный накопитель 20 - адреса неработоспо-. собных ячеек накопителя 1, обнаруженных при записи массива данных, В режиме чтения в счетчике 23 по входу 39 принимается адрес массива адресов неработоспособных ячеек накопителя 1 (соответствующих считываемому из накопителя 1 массиву, данньк), а на зт1равляющий вход 36 подается единичный сигнал. Контрольный код массива данных считывается из ячейки накопителя 1 и через элементы И 19 (при наличии управляющего сигнала с входа 33) принимается в регистр 3, с выходов которого по управляющему сигналу с входа 32 выдается через элементы И 12 группы а счетчик 13. Адрес счетчика 23 принимается в регистр 21 и производится считывание из дополнительного накопителя 20 в регистр 22 адреса ближайшей неработоспособной ячейки накопителя 1. При считывании каждого слова из накопителя 1 выполняются следующие действия: проверка работоспособности ячейки накопителя 1 и считывание из нее информации, формирование результирующегс бита четности адреса и считьгеаемого слова ч вычитание его из содержимого счетчика 13, коррекция кода величины массива считываемой информации и формирование очеред ного адреса считывания и обнуление регистра 18. При проверке работоспособности . ячейки накопителя 1 блоком 28 производится сравнение адресов, находящих ся в регистрах 4 и 22. При совпадени адресов (ячейка неработоспособна) на выходе блока28 и элемента И 25 фиксируется единичный сигнал, который увеличивает на единицу значения в счетчиках 14 и 23, которые шядаются в регистры 4 и 21. Из дополнитель ного накопителя 20 в регистр 22 считывается адрес следующей неработоспособной ячейки накопителя 1 и вновь производится сравнение адресов содержащихся в регистрах 4 и 22, блоком 28. При совпадении процесс повторяется, таким образом, производится обход неработоспособных ячеек накопителя 1 без непосредственного обращения к ним. . При несовпадении адресов (ячейка работоспособна) производится считывание информации из ячейки накопителя 1 по адресу, содержащемуся в регистре 4, через элементы И 19 (при nocTytmeifflH управлякицеГо сигнала с входа 33) в регистр 3. Сигнал несовпадения инвертируется элементом НЕ 29 и на выходе элемента И 26 и элемента ИЛИ 27 формируется единичный сигнал, свидетельствующий о работоспособности ячейки. Одновременно со считыванием из на копителя 1 адрес считывания из счетчика 14 выдается на сумматор 7, а считываемое слово с регистра 3 через элементы ИЛИ 5 - на сумматор 8, в которых формируются биты четности адреса и считываемого слова, которые объединяются сумматором 9 в результирующий бит четности. По единичному сигналу с выхода элемента ИЛИ 27 результирующий бит четности через элемент И 10 вьщается на вход счетчика 13. При считывании счетчик 13 работает в режиме вычитания, поэтому из содержимого счетчика 13 вычита- ется значение результирующего бита. Считанное слово из регистра 3 вьщается на выход 31 устройства. Коррекция кода величины считываемого массива информации, формирование очередного адреса считывания и обнуление регистра 18 осуществляются так же, как и при записи информации в ячейку накопителя 1. Считывание информации продолжается до тех пор, пока последний элемент массива не будет считан с накопителя 1.При этом содержимое счетчика 15 становится равным нулю и на выходе 37 формируется нулевой сигнал. Если в процессе записи, хранения или считывания данных в устройстве возникают ошибки, счетчик 13 фиксирует количество ошибок, и в случае их большого количества считывание информации можно произвести повторно. Предлагаемое устройство по срав- . нению с известным является более быстродействукхцим.При считывании массива данных быстродействие предлагаемого устройства выше на 75% по сравнению с быстродействием известного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1982 |

|

SU1034070A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Запоминающее устройство с обнаружением ошибок | 1985 |

|

SU1277215A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1088073A2 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с обнаружением ошибок | 1984 |

|

SU1164791A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

ЗАПОМИНАЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОПИВОК по авт. св. № 1034070, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дополнительный накопитель, пятый и шестой регистры, четвертый счетчик импульсов, третья группа элементов И, четвертый и пятый элементы И, второй элемент ИЛИ, блок сравнения, элемент НЕ и элемент ШШ-НЕ, причем первый вход четвертого счетчика импульсов является другим адресным входом устройства, входы пятого ре . гистра соединены с выходами четвертого счетчика импульсов, а.выходы подключены к адресным входам допол- . нительного накопителя, информационные входы которого соединены с шлходами элементов И третьей группы, а выходы - с входами шестого регистра, выходы которого подключены к одним из входов блока сравнения, другие входы которого соединены с первыми входами элементов И третьей группы и с выходами третьего регистра, а выход соединен с входом элемента НЕ и с первым входом четвертого элемента И, выход которого подктаочен к третьему входу второго счетчика импульсови к второму входу четвертого счетчика импульсов, третий вход i которого соединен с вторыми входами элементов И третьей группы и с выходом элемента ИЛИ-НЕ, первый вход которого, второй вход четвертого элемента И и первый вход пятого элемента И являются одним из управляющих входов устройства, второй вход пятого элемента И соединен с выходом элемента НЕ, а выход - с одним СО из входов второго элемента ИЛИ, выО 00 ход которого подключен к вторым входам первого и второго элементов И со и к второму входу элемента ШШ-НЕ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-12-23—Публикация

1983-09-26—Подача