Изобретение относится к запоминающим устройствам.

Цель изобретения - повьшение надежности устройства путем исключения случаев ложных сбоев при передаче массивов с повторяющимися адресами и повьппение диагностичности системы.

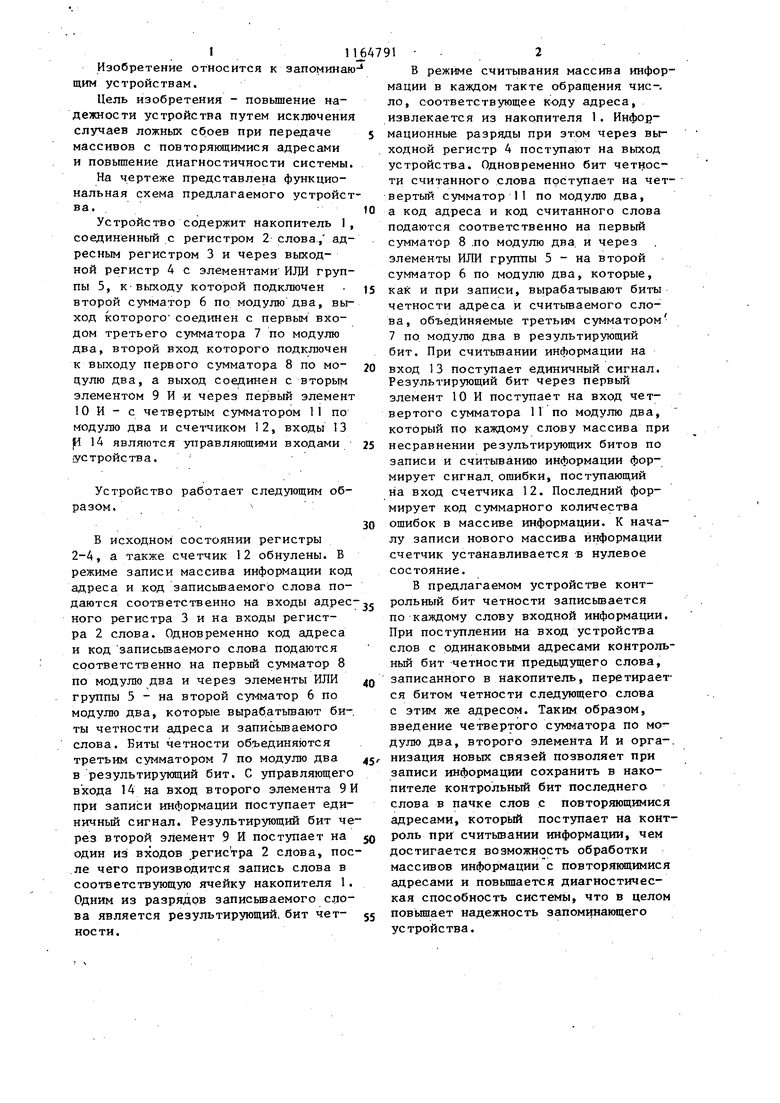

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит накопитель 1 , соединенный с регистром 2 слова., адресным регистром 3 и через выходной регистр 4 с элементами ИЛИ группы 5, к выходу которой подключен второй сумматор 6 по модулю два, выход которого соединен с первым входом третьего сумматора 7 по модулю два, второй вход которого подключен к выходу первого сумматора 8 по моцулю два, а выход соединен с вторым элементом 9 И -и через элемент 10 И - с четвертым сумматором 11 по модулю два и сче1чиком 12, входы 13 JH 14 являются управляющими входами устройства.

Устройство работает следующим образом. .

Б исходном состоянии регистры 2-4, а также счетчик 12 обнулены. В режиме записи массива информации код адреса и код записываемого слова подаются соответственно на входы адресного регистра 3 и на входы регистра 2 слова. Одновременно код адреса и код записьшаемого слова подаются соответственно на первый сумматор 8 по модулю два и через элементы ИЛИ группы 5 - на второй сумматор 6 по модулю два, которые вырабатьшают биты четности адреса и записьшаемого слова. Биты четности об.ъединяются третьим сумматором 7 по модулю два в результирующий бит. С управляющего входа 14 на вход второго элемента 9И при записи информации поступает единичный сигнал. Результирующий бит через второй элемент 9 И поступает на один из входов регистра 2 слова, пос,ле чего производится запись слова в соответствующую ячейку накопителя 1. Одним из разрядов записьшаемого слова является результирующий, бит четности.

В режиме считывания массива информации в каждом такте обращения чис-ло, соответствующее коду адреса, извлекается из накопителя 1. Информационные разряды при этом через выходной регистр 4 поступают на выход устройства. Одновременно бит четности считанного слова поступает на четвертый сумматор 11 по модулю два, а код адреса и код считанного слова подаются соответственно на первый сумматор 8 .по модулю два. и через элементы ИЛИ группы 5 - на второй сумматор 6 по модулю два, которые, как и при записи, вырабатывают биты четности адреса и считьгоаемого слова, объединяемые третьим сумматором 7 по модулю два в результирующий бит. При считьтании информации на

вход 13 поступает единичный сигнал. Результирующий бит через первый

элемент 10 И поступает на вход четвертого сумматора 11 по модулю два, который по каждому слову массива при несравнении результирующих битов по записи и считыванию информации формирует сигнал, ошибки, поступающий на вход счетчика 12. Последний формирует код суммарного количества ошибок в массиве информации. К началу записи нового массива информации счетчик устанавливается -в нулевое состояние.

В предлагаемом устройстве контрольный бит четности записьгоается по каждому слову входной информации. При поступлении на вход устройства слов с одинаковыми адресами контрольный бит четности предьщущего слова, записанного в накопитель, перетирается битом четности следующего слова с этим же адресом. Таким образом, введение четвертого сумматора по модулю два, второго элемента И и орга- низация иовых связей позволяет при записи информации сохранить в накопителе контрольный бит последнего слова в пачке слов с повторяющимися адресами, который поступает на контроль при считьшаиии информации, чем достигается возможность обработки массивов информации с повторяющимися адресами и повышается диагностическая способность системы, что в целом повьшает надежность запом1 нающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Запоминающее устройство с обнаружением ошибок | 1985 |

|

SU1277215A1 |

| Запоминающее устройство с обнаружением ошибок | 1982 |

|

SU1034070A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1130897A2 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1088073A2 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

| Запоминающее устройство с обнаружением ошибок | 1980 |

|

SU881876A1 |

| Запоминающее устройство с обнаружением ошибок | 1977 |

|

SU672655A1 |

| Устройство для сопряжения ЦВМ с линиями связи | 1986 |

|

SU1462328A1 |

ЗАПОМИНАНШЩЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК, содержащее накопитель, регистр слова, адресный регистр, выходной регистр, группу элементов ИЛИ, первьй, второй и третий сумматоры по модулю два, первый элемент И, счетчик, причем входы накопителя подключены соответственно к выходам регистра слова и адресного регистра, а выходы - к входам выходного регистра, выходы которого соединены с первыми входами элементов ИЛИ группы, причем выходы элементов ИЛИ группы и вход адресного регистра соединены соответственно с входами второго и первого сумматоров по мо-. дулю два, выходы которых подключены к входам третьего сумматора -по модулю два, выход которого соединен с вторым входом первого элемента И, вторые входы элементов ИЛИ группы, входы адресного регистра и выход счетчика являются соответственно информационньми и адресными входами и контрольным вьпсодрм устройства, отличающееся тем, что, с целью повышения надежности устройства, внего введены второй элемент И и четвертый сумматор по модулю два, первый вход которого соединен с выходом первого элемента И, а второй вход подключен к одному из выходов выходного регистра, а выход соединен с входом счетчика, причем выход третьего сумматора по модулю два соединен с вторым входом второго элемента И, выход которого соединен с одним иэ входов регистра слова, другие входы которого соединены с вторыми входами элементов ИЛИ группы , а первые входы первого и второго элементов И О) являются соответственно первым и втоNU рым управляющими входами устройства. СО

| Запоминающее устройство с обнаружением ошибок | 1977 |

|

SU672655A1 |

| Солесос | 1922 |

|

SU29A1 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-06-30—Публикация

1984-01-30—Подача