Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств с обнаружением ошибок и возможностью локализации неисправностей.

Цель изобретения - повьппение надежности устройства.

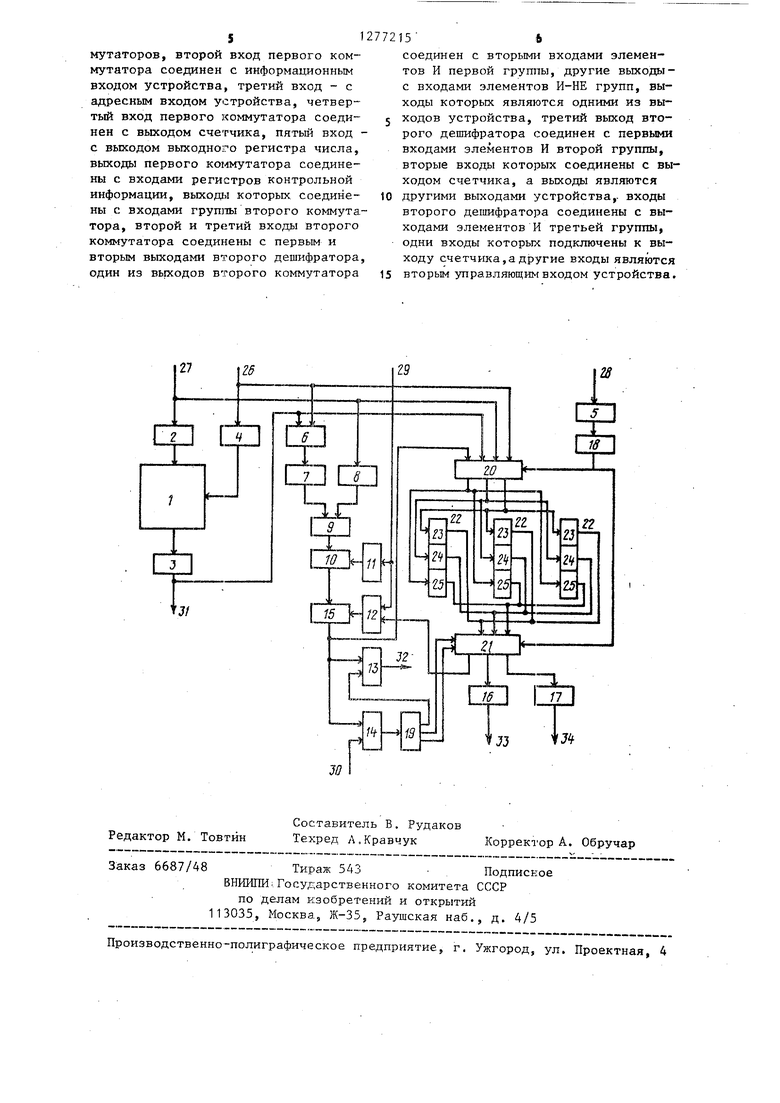

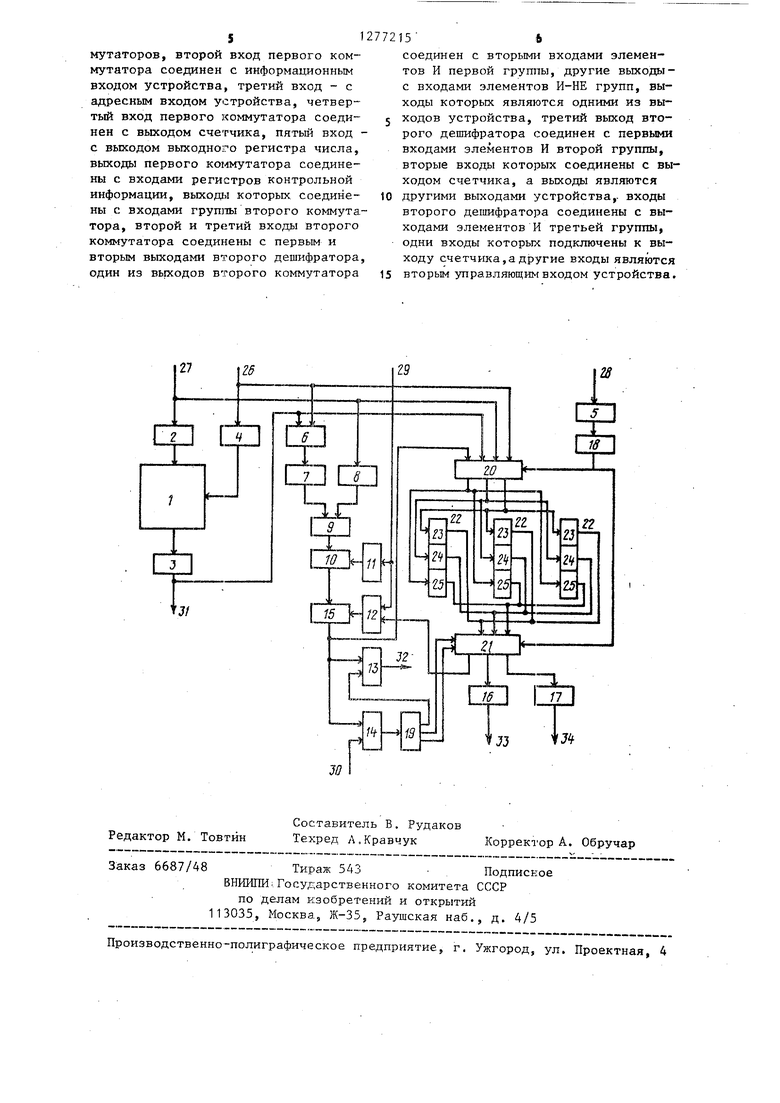

На чертеже изображена структурная схема запоминающего устройства с обнаружением ошибок.

Устройство содержит накопитель 1, входной регистр 2 числа, выходной регистр 3 числа, первьш 4 и второй 5 регистры.адреса, элементы ИЛИ 6, первый 7, второй 8 и третий 9 сумматоры по модулю два, элемент И 10, элемент НЕ 11, 12, вторую 13 и третью 14 группы элементов И, счетчик 15, первую 16 и вторую 17 группы элементов И-НЕ, первый 18 и второй 19 дешифраторы, первьй 20 и второй 21 коммутаторы, регистры 22 контрольной информации, причем поле 23 каждого регистра 22 предназначено для хранения содержимого счетчика 15 поле 24 - для хранения поразрядной суммы по модулю два кодов адресов слов массива, поле 25 - для хранения поразрядной суммы по модулю два кода слов массива. Разряды полер 24 и 25 каждого регистра 22 выполнены на базе триггеров со счетным входом.

На чертеже обозначены информационный 26 и адресный 27 входы устройства. На вход 28 поступает адрес массива, на входы 29 к 30 - управляющие сигналы. Устройство имеет первьш 31, второй 32, третий 33, четвертьй 34 выходы.

Устройство работает следующ1;-1м образом.

В исходном состоянии регистры 2-5 и 22, а также счетчик 15 обнулены. В режиме записи код адреса, код записываемого слова и код адреса массива подаются соответственно на входы регистров 4, 2 и 5 и происходит запись слова в соответствующую Ячейку накопителя 1. Одновременно код записываемого слова подается через элементы 1ШК 6 на вход с:/мма- тора 7 и на вход коммутатора 20, а код адреса - на вход сумматора 8 и вход коммутатора 2С. Сумматоры 7 и 8 вырабатывает биты четности адреса и записьшаемого слова. Биты четности объединяются сумматором 9 в резуль

5

0

тирующий бит. с входа 29 на вход элемента НЕ 11 при этом поступает нулевой сигнал. Следовательно, на выходе элемента НЕ 11 при этом единичный уровень, В случае едийичного значения результирующего бита он через элемент И 10 поступает на вход счетчика 15. Содержимое счетчика 15 (он является реверсивным) увеличивается на единицу, так как при записи информации он работает как суммирующий.

Код адреса массива с регистра 5 поступает на вход дешифратора 18, который вырабатывает управляющий сигнал, обеспечивающий прием через коммутатор 20 на соответствующий (в соответствии с содержимым регистра 5) регистр 22 с входов 26 и 27 устройства. При этом в поле 24 на счетные входы триггеров поступают коды адресов слов записываемого массива, а в поле 25 - коды слов массива.

Таким образом, к концу записи всего массива информации в накопитель 1 счетчик 15 зафиксирует количество результирующих одиночных битов, равных единице, а в поле 24 и поле 25 регистра 22 контрольной информации будут храниться поразрядные суммы по модулю два кодов адресов массива и кодов записанных слов соответственно. Зафиксированное счетчиком 15 число (контрольный код) по фронту окончания импульса записи последнего чис- 5 ла массива в накопитель 1 заносится через коммутатор 20 в поле 23 выбранного регистра 22, где сохраняется до тех пор, пока соответствующий массив информации Н11ХОДИТСЯ в накопителе 1, а счетчик 15 обнуляется.

С приходом импульса записи первого числа следуюп;,его массива информации устройство аналогично описанному выше производит его запись. Кон гроль- ная информация этого массива будет формироваться и храниться в полях следующего регистра 22.

5

0

0

SO

55

Перед считыванием информации соответствующий контрольный код из поля 23 регистра 22 записывается в счетчик 15. Выбор соответствующего регистра 22 обеспечивается управляю- 1Вд-1м сигналом с дешифратора 18, а запись в счетчик 15 - управляющим сигналом с входа 29 устройства.

В режиме считьгоания массива информации в каждом такте обращения число, соответствующее зада1шому адресу.

3

извлекается из накопителя 1, поступает на выход устройства и через регистр,3, элементы ИЛИ группы 6 - на сумматор 7, а через коммутатор 20 на счетные входы триггеров поля 25 выбранного регистра 22. Одновременно код адреса подается через коммутатор 20 на счетные входы триггеров поля 24 регистра 22 и на сумматор 8

Сумматоры 7 и 8, как и при записи вырабатывают биты четности адреса и считываемого слова, объединяемые . сумматором 9 в результирующий бит. При этом на вход 29 устройства подается нулевой сигнал. Результирующий. бит через элемент И 10 поступает на вход счетчика 15, который при считы- вании работает как вычитающий.

После считывания последнего числа массива информации в поле 24 ре- гистра 22 будет зафиксирован результат поразрядного суммирования кодов адресов записанных и затем считанных слов, в поле 25 - результат поразрядного суммирования кодов этих слов, в счетчике 15 - код суммарного количества ошибок, возникших при записи или считывании в устройство и выявленных контролем по четности.

В случае нулевого значения содер- жимого счетчика 15 по сигналу дешифратора 19 коды, хранящиеся в полях 24 и 25 соответствующего регистра 22, с инверсных выходов регистра через коммутатор 21 вьщаются соответ- ственно на входы элементов И-НЕ первой 16 и второй 17 групп И-НЕ. Еди- ничньш сигнал на выходе 33 элементов И-НЕ первой группы 16 свидетельствует об отсутствии ошибок в адресных цепях устройства, а единичный сигнал на выходе 34 элементов И-НЕ второй 17 группы - в информационной цепи. Нулевой сигнал хотя бы на одном из выходов 33 и 34 указывает на наличие ошибок в устройстве, возникших при записи или считывании выявленных контролем с использованием поразрядного суммирования кодов чисел и адресов.

Ненулевое значение содержимого счетчика 15, которое вьщается на выход 32, указывает количество ошибок, возникающих в устройстве и выявлен- ньк контролем по четности. Для анали за, где именно возникли ошибки (в информационной части или адресной), дешифратор 19 обеспечивает выдачу на

0

72

5

0 5 0 5 Q

5

15

выходы 33 и 34 содержимого полей 24 и 25 регистра 22,

при нулевых значениях содержимого счетчика 15 и полей 24 и, 25 регистра 22 принимается решение о безошибочности выдаваемой из устройства информации.

Формула изобретения

Запоминающее устройство с обнаружением ошибок, содержащее накопитель, входной регистр числа, первый регистр адреса, выходной регистр числа, элементы ИЛИ, суьматоры по модулю два, счетчик, перв то группу элементов И, элемент НЕ и элемент И причем входы накопителя подключены соответственно к выходам входного регистра числа и первого .регистра адреса, а выходы - к входам выходного регистра числа, выходы которого соединены с одними из входов элементов ИЛИ, входы первого и второго сумматоров по модулю два подключены соответственно к входу первого регистра адреса и к выходам элементов ИЛИ, выходы первого и второго сумматоров по модулю два соединены соответственно с входами третьего сумматора по модулю два, другие входы элементов ИЛИ, входы первого регистра адреса являются соответственно информационным и первым адресным входом устройства, первый и второй входы элемента И подключены соответственно к выходу третьего сумматора по модулю два и к выходу элемента НЕ, вход которого соединен с первыми входами элементов И первой группы и является первым, управляющим входом устройства, выходы элементов И первой группы соединены с одним из входов счетчика, другой вход которого подключен к выходу элемента И, отличающееся тем, что, с целью повьшзения надежности устройства, в него введены второй регистр адреса,первьш и второй дешифраторы, первый и второй коммутаторы, регистры контрольной информации, вторая и третья группы элементов И, первая и вторая группы элементов И-НЕ, причем входы второго регистра адреса являются вторым адресным входом устройства, а выходы со- единены с входами первого дешифратора, выходы которого соединены с пер- выми входами первого и второго комS12

мутаторов, второй вход первого коммутатора соединен с информащтонным входом устройства, третий вход - с адресным входом устройства, четвертый вход первого коммутатора соединен с выходом счетчика, пятый вход - с выходом выходного регистра числа, выходы первого ко мутатора соединены с входами регистров контрольной информации, выходы которых соединены с входами группы второго коммутатора, второй и третий входы второго коммутатора соединены с первым и вторым выходами второго дешифратора, один из вьрсодов второго коммутатора

Редактор М. Товтйн

Составитель В. Рудаков Техред Л.Кравчук

Заказ 6687/48 Тираж 543 Подписное ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

15 6

соединен с вторыми входами элементов И первой группы, другие вькоды- с входами элементов И-НЕ групп, выходы которых являются одними из выходов устройства, третий выход второго дешифратора соединен с первыми входами элементов И второй группы, вторые входы которых соединены с выходом счетчика, а выходы являются другими выходами устройства,, входы второго дегнифратора соединены с выходами элементов И третьей группы, одни входы которых подключены к выходу счетчика,а другие входы являются вторым управляющим входом устройства.

Корректор А. Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1982 |

|

SU1034070A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1130897A2 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1088073A2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Постоянное запоминающее устройство с самоконтролем | 1985 |

|

SU1285538A1 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств с обнаружением ошибок и возможностью локализации неисправностей. Цель изобретения - повьппение надежности устройства. Устройство содержит накопитель, два регистра адреса, сумматоры по модулю два, счетчик, группы элементов И, два дешифратора, счетчик, регистры контрольной информации, два коммутатора, группы элементов И-НЕ. В устройстве происходит локализации неисправности (определяется в адресной или информационной частях находится неисправность), обнаруживается ошибка при приеме массивов информации, поступающей в устройство непрерывно. 1 ил. ю | N5

| Устройство для контроля памяти | 1981 |

|

SU1001180A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-15—Публикация

1985-04-25—Подача