Изобретение относится к вычйслительной технике, в частности к запоминающим устройствам.

Известно запоминающее устройство с обнаружением ошибок, содержащее накопитель, входные и адресные регистры, блоки сверток по модулю два, сумматоры по модулю два, счетчики и ВБГЧитатель fl.

Недостатком известного устройства является невозможность контроля брлее чем одного массива информации.

Наиболее близким к предлагаемому является запоминающее устройство с обнаружением ошибок, содержащее накопитель, регистр слова, адресный регистр, выходной регистр, первую и вторую группы элементов ИЛИ, первый, второй и третий сумматоры по модулю два, первый элемент И, элемент НЕ, первую группу элементов И и рчетчик реверсивного типа, причем входы накопителя подключены соответственно к выходам регистра слова и адресного регистра, а выходы - к входам выходного регистра, выходы которого соединены с первыми входами первых групп элементов ИЛИ и И, входы первого и второго сумматоров по модулю два подключены соответст.венно к входу адресного регистра и к выходам элементов ИЛИ первой группы, входы первого и . второго сумматоров по модулю два соединены соответственно с входами третьего сумматора по модулю два, первый и второй входы первого элемента И подключены соответственно к выходу третьего сумматора по модулю два и выходу элемента НЕ, вход элемента НЕ соединен с вторыми входами первой группы элементов И и является управляющим входом устройства,выхолн первой группы элементов И соединены с одним из входов счетчика, другой вход которого подключен к выходу первого элемента И, а выходы - к вторым входам элементов ИШ второй группы, первые входы элементов ИЛИ второй группы подключены к вторым входам элементов ИЛИ первой группы, а выходы - к входам регистра слова, входы адресного регистра и один из входов первого сумматора по модулю два являются адресными, а первый вход второй группы и второй вход первой группы элементов ИЛИ - информационными входами устройства 2 .

Недостатком этого устройства является низкая надежность, так как при возникновении отказов ячеек накопителя запоминающее устройство становится неработоспособным.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в эапорданающее .устройство с обнаружением ошибок г содержащеенакопитель, регистры, сумматоры по модулю

два, первый счетчик импульсов, группы элементов ИЛИ, первый элемент И и первую группу элементов И, первые входы которых являются одними из управляющих входрв устройства, причем первые входы элементов ИЛИ первой и второй групп соответственно объединены и являются информационными входами устройства, выходы элементов ИЛИ второй группы подключены к входам первого регистра, выходы которого соединены с информационными вхп ::, дами накопителя, одни из выходов второго рег.истра подключены к вторым входам элементов ИЛИ первой группы и вторым входам элементов И первой группы, выходы которых соединены с одними из входов первого счетчика импульсов, другой вход которого подключен к выходу первого элемента И, а выход - к вторым входам элементов ИЛИ второй группы, адресные входы накопителя соединены с выходами третьего .регистра, входы первого и второго сумматоров по модулю два соединены соответственно с входами третьего регистра и с выходами элементов ИЛИ второй группы, а выходы подключены к входам третьего сумматора по модулю два, выход которого соединен с .первым входом первого элемента И, другие Выходы второго регистра являются информационньоми выходами устройства, введены второй и третий счетчики импульсов, второй и третий элементы И, четвертый регистр, элемент ИЛИ и вторая группа элементов И первые входы которых соединены с входами четвертого регистра и выходами накопителя, а выходы - с входами второго регистра, причем выходы второго счетчика импульсов подключены к входам третьего регистра, а один из входов соединен с первым входом второго элемента И, второй вход которого подключен к второму входу первого элемента И и выходу третьего элемента И, входы которого соединены с выходами четвертого регистра, выход второго элемента И подключен к первому ВХОДУ третьего счетчика импульсов , Выходы которого соединены с входами элемента ИЛИ, выход которого кх«ляется индикаторным выходом устройства, другие входы второго счетчика импульсов являются сщресными входами устройства, другими управляющими входами которого являются вторые входа элементоа И второй группы,-первый вход второго элемента И и второй вход третьего сметчика импульсов, третьи входы элементов ИЛИ второй группы подключены к выходам второго регистра.

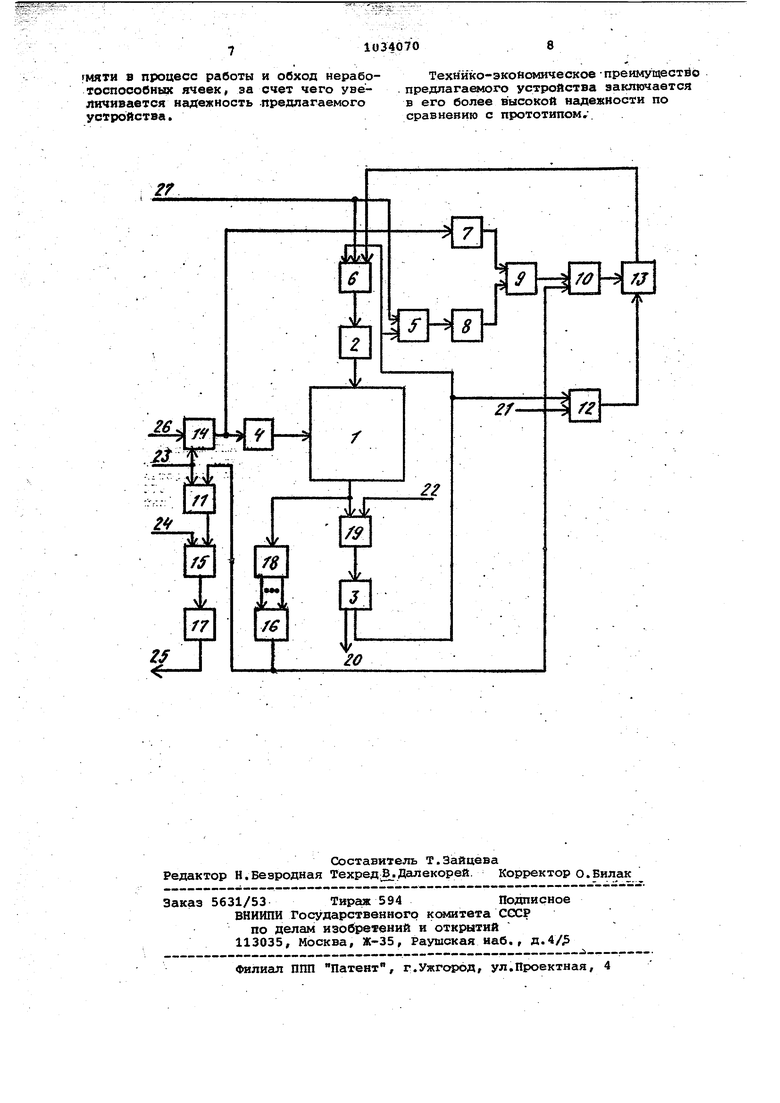

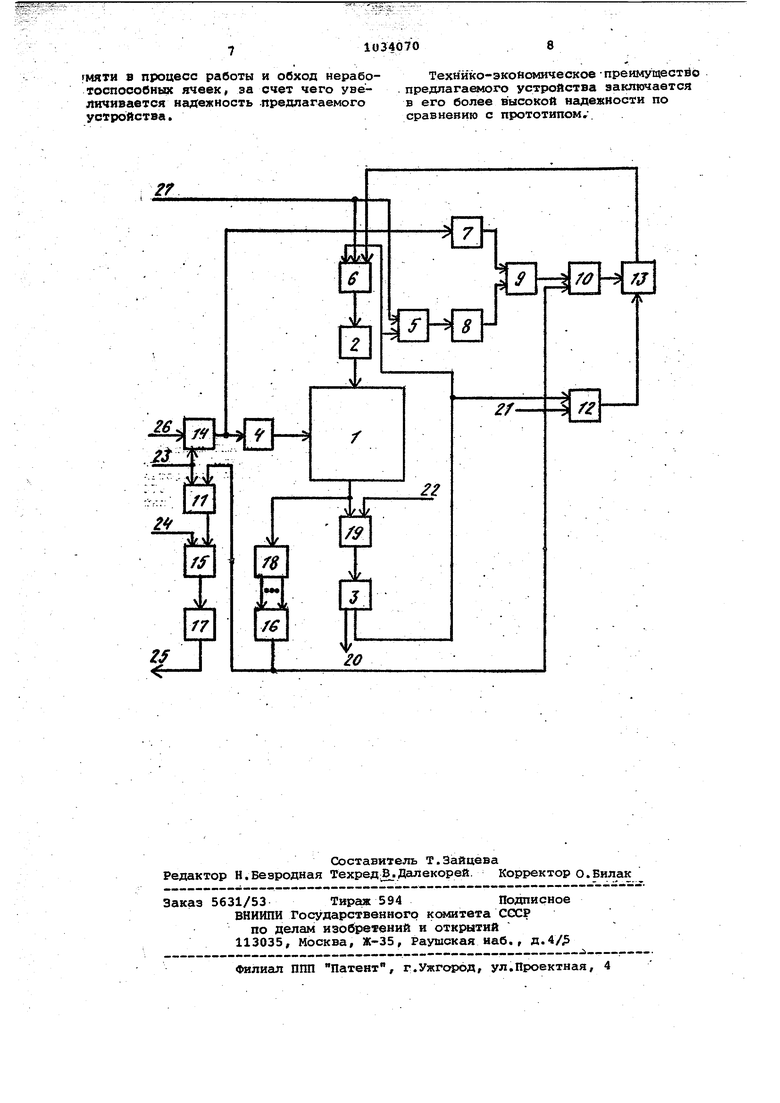

Еа чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит накопитель 1, первый 2, второй 3 и третий 4 регисЗтры, первую 5 и вторую 6 группы элементов ИЛИ, первый 7, второй 8 и третий 9 сумматоры по модулю два, первый 10 и в.торой 11 элементы И,первую группу элементов И 12, первый 13 второй 14 и третий 15 счетчики импульсов, третий элемент И 16, элемент ИЛИ 17, четвертый регистр 18, вторую группу элементов И 19.

На чертеже обозначены информационные выходы 20, первый 21, второй 22, третий 23 и четвертый 24 управляющие входы, индикаторный выход 25, адресные 26 и информационные 27 входы устройства.

Счетчик 13 выполнен реверсивным.

Устройство работает.следующим образом.

В исходном состоянии регистры 2, 3, 4 и 18, счетчики 13 и 14 обнулены. В счетчик 15 по входу 24 записывается код величины массива информации, который необходимо записать в накопитель 1 или считать с него, а в счетчик 14 по входам 26 принимается адрес начала массива в накопителе 1. Обращение к ячейке накопителя 1 для эап«си или считывания информации осуществляется по-адресу, который формируется в счетчике 14, а затем внщается в регистр 4,

При записи каждого слова в накопитель 1 выполняются следующие операции: проверка работоспособности ячейки накопителя 1 и запись в нее информации, формирование результирующего бита четности адреса и записываемого слова и запись его в Ьчетчик 13, коррекция кода Величины массива информации и формирование очередного адреса записи и обнуление регистра 18.

При проверке работоспособности ячейки накопителя 1 записываемое слово поступает по входам 27 через группу элементов ИЛИ 6 на регистр 2. Инверсный код слова с регистра 2 записывается в ячейку накопителя 1 по адресу, содержащемуся в регистре 4, и затем .считывается на регистр 18. После этого осуществляется запись прямого кода слова (с прямых выходов регистра 2) в эту же ячейку накодителя 1 и его считывание с одновременной регенерацией. Считанное слово выдается на регистр 18 и через элементы И 19 группы (при поступлении сигнала по входу 22) - на регистр 3. На регистре 18 осуществляется поразрядное суммирование по модулю два инверсного и прямого кодов слова. Бели ячейка накопителя 1, .в которую производилась запись инверсного, а затем прямого кодов слова, работоспособна, то все разряды регистра 18 установятся в единичное состояние и на выходе элемента И 16 сформируется единич«ый

сигнал, свидетельствующий о работоспособности ячейки. В данном случае слово уже записано в требуемую ячейку накопителя 1.

Одновременно с записью в накопитель 1 адрес записи из счетчика 14 выдается на сумматор 7, а записываемое слово по входам 27 через элементы ИЛИ группы 5 - на сумматор 8, где формируются биты четности адреса и записываемого слова, которые объединяются сумматором 9 в результирующий бит четности.

Если ячейка работоспособна, то по единичному сигналу с выхода элемента И 16 регультирующий бит четности через элемент И 10 поступает на вход счетчика 13. При записи счетчик 13 работает в режиме суммирования, поэтому к содержимому счетчика 13 прибавляется значение результирующего бита четности.

Кроме того, единичный сигнал с выхода элемента И 16 поступает на вход элемента И 11 и разрешает коррекцию кода величины массива. Коррекция осуществляется с помощью управляющего сигнала, поступающего п& входу 23 через элемент И 11 на вхо . счетчика 15. Счетчик 15 работает всегда в режиме вычитания, поэтому его значение, уменьшается на единицу после записи одного слова.

Управляющий сигнал с входа 23 поступает также на счетчик 14 и увеличивает .его значение на единицу, т.е. формирует адрес очередного слова, который выдается в регистр 4, Далее осуществляется аналогично рассмотренному запись очередного слова.

Если в проверяемой ячейке накопителя 1 неисправен хотя бы один разряд, то значение считываемого из него сигнала является одинаковым как в прямом, так и в инверсном значениях слова. Поэтому содержимое соответствующего ему разряда регистра 18 будет равно нулю и на выходе элемента И 16 формируется нулевой сигнал, свидетельствующий о неработоспособ ности ячейки. Этот сигнал запрещает запись результирующего бита, четности адреса и записываемого слова в счетчик 13 и коррекцию кода величины массива в счетчике 15. В данном случае по управляющему сигналу с входа 23 адрес записи увеличивается на единицу, осуществляется проверка соответствующей ячейки накопителя 1 и в случае ее работоспособности запись с регистра-2 слова, которое должно было быть записано в предыдущую (неработоспособную ) ячейку, т.е. осуществляется обход неработоспособной ячейки.

Запись будет продолжаться до тех пор, пока весь массив информации не будет записан в Накопитель 1, При

этом содержимое счетчика 15 станет равно нулю и на выходе 25 сформируется нулевой сигнал. Счетчик 13 зафиксирует количество результирующих битов, равных единице. Зафиксированное счетчиком 13 число через элементы ИЛИ б группы подается на регистр 2 и записывается в накЬпитель 1. Таким образом в накопитель 1 будет записан с обходом неработоспособных ячеек массив информации и соответствующий er-iy контрольный код.

При считывании массива информации так же, как и при записи,, регистры 2, 3, 4 и 18 и счетчик 14 обнуляются.Затем контрольный код массива ИИформации считывается из ячейки накопителя 1 и через элементы И 19 группы (.при наличии управляющего сигнала с входа 22) принимается в регистр 3, с выходов которого по управляющему сигналу с -входа 21 выдается через элементы И 12 группы на счетчик 13. При считывании каждого слова из накопителя 1 по адресу, содержащемус в регистре 14, выполняются cлeдsfFЭI1иe действия: проверка работоспособности ячейки накопителя 1, с которой считывается .Слово, формирование результирующего бита четности адреса и счи-тываемого слова и вычитание его из содержимого счетчика 13, коррекция . кода величины массива считываемой информации и формирование очередного адреса считывания и обнуления регистра 18.

При проверке работоспособности ячейки производится считывание содержащегося в ней прямого кода слева и выдача его на регистр 18 и через элементы И 19 группы (при поступлении управляющего сигнала с входа 22) на регистр 3. С регистра 3 считанное слово через элементы ИЛИ б группы поступает на регистр 2, инверсный код слова с выходов которого записывается в эту же ячейку накопителя 1 (в ячейку, с которой было считано слово) и затем считывается на регистр 18. На регистре 18 осуществляется поразрядное суммирование по модулю два инверсного и прямого кодов слова. Если ячейка накопителя, с которой считывался сначала прямой, а затем инверсный коды слова, работоспособна, то все разряды регистра 18 установятся в единичное состояние и на выходе элемента .И 16 сформируется единичный сигнал, свидетельствующий о работоспособности ячейки.

Одновременно со считыванием с накопителя 1 адрес считывания из счет-г чика 14 выдается на сумматор 7, а считываемое слово с регистра 3 через ИЛИ 5 группы - на сумматор ,8, в которых формируются биты четности адреса и считываемого слова,

которые объединяются сумматором 9 в результирующий бит четности.

Если ячейка работоспособна, то считанное слово из регистра 3 выдается на выходы 20 устройства. Кроме того, по единичному сигналу с выхода элемента И 16 результирующий бит четности через элемент И 10 вьщается на вход счетчика 13. При считывании t счетчик 13 работает в режиме вычитания, поэтому из содержимого счетчика 13 вычитается значение результирующего бита. . .

Коррекция кода величины считываемого массива информации и формирование очередного адреса записи, обнуление регистра 18 осуществляются так же, KajK и при записи в ячейку накопителя 1 информации.

Если в ячейке накопителя 1 неисправен хотя бы один разряд, то значение считываемого и-з него сигнала является одинаковым как для прямого, так и для инверсного значений кодов слова. Поэтому содержимое соответствующего ему разряда регистра 18 равно, нулю и на выходе элемента И 16 формируется нулевой сигнал, свидетельствующий о неработоспособности ячейки. Этот сигнал запрещает запись результирующего бита четности адреса и записываемого слова в счетчик 13 и коррекцию кода величинымассива в счетчике 15. В данном случае считанное с регистра 3 слово на выход 20 устройства не вьщается, по управляющему сигналу со входа 23 адрес считы вания увеличивается на единицу, осуществляется проверка соответствующей ячейки накопителя 1 и в случае ее работоспособности - считывание по.следующего слова, .то есть осуществляется обход неработоспособной ячейки.

Считывание информации будет продолжаться до тех пор, пока последний элемент массива не будет считан с накопителя 1. При этом содержимое счетчика 15 станет равным нулю и на выходе 25 сформируется нулевой сигнал. Если в процессе записи, хранения или считывания информации в устройстве возникают ошибки, не связанные с не-. исправностью, ячеек памяти, то.счетчик 13 зафиксирует количество ошибок и в случае ихбольшого количества считывание информации можно производить повторно. При этом в счетчик предварительно вновь записывается контрольный код, а на счетчик 15 - код величины массива информации.

Таким образом, по сравнению с известным устройством при записи и считывании каждый раз проверяется состояние ячейки накопителя 1, т.е. осуществляется динамический контроль пагмяти В процесс работы и обход нерабртоспособньк ячеек, за счет чего увеличивается надежность .предлагаемого устройства.

Технйко-экойомическое -преимущество предлагаемого устройства заключается в его более высокой нгщежности по сравнению с прототипом,

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1130897A2 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1088073A2 |

| Запоминающее устройство с обнаружением ошибок | 1981 |

|

SU955197A1 |

| Запоминающее устройство с обнаружением ошибок | 1985 |

|

SU1277215A1 |

| Запоминающее устройство с обнаружением ошибок | 1984 |

|

SU1164791A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

| Запоминающее устройство с обнаружением ошибок | 1980 |

|

SU881876A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ Ш1ИБОК, содержащее накоЬитель, регистры,, сумматоры по модулю два, первый счетчик импульсов, группы элементов ИЛИ, первый элемент Ни первую группу элементов И, первые входы которых являются одними из управляющих входов устройства, причем лервые вхЬды элементов ИЛИ первой и второй групп соответственно объединены и являются информационными входами устройства, вьаходы элементов ИЛИ второй группы подключены к входам первого регистра, выходы которого соединены с информационными входами накопителя, одни из выходов второго регистра подключены к вторым входам элементов ИЛИ первой группы и вторым .. ;входам элементов И первой группы, выходы KOTopibK соединены с одними из входов первого счетчика импульсов, другой вход которого подключен к выходу первого элемента И, а выход :к вторым входам элементов ИЛИ второй группы, адресные входы накопителя соединены с выходами третьего регист:ра, входы первого и второго сумматоров по модулю два соединены соответственно с входами третьего регистра и с выходами элементов ИЛИ второй группы, а выходы подключены к входам третьего сумматора по модулю два, выход которого соединен с первым входом первого элемента И, другие выходы второго регистра являются информационными выходами устройства, о т л и чающееся тем, что, с целью повышения надежности устройства, в него введены второй и третий счетчики импульсов, второй, и третий элементы И, четвертый регистр, элемент ИЛИ и вторая группа элементов И, первые входы которых соединены с входами четвертого регистра и выходами накоI пителя , а выходы - с входами второго регистра, причем выходы второго счет(Л чика импульсов подключены к входам третьего регистра, а один из входов с соединен с первыгл входом второго элемента И, второй вход которого подключен к второму входу первого элемента И и выходу третьего элемента И, входы которого соединены с выходами четвертого регистра, выход второго элемента И подключен к первому входу третьего счетчика и шyльcoв, выходы которого соединены с входами элемента ИЛИ, выход которого является индикаторным выходом устройства, другие входы второго счетчика импульсов .являются адресными входами устройства , другими управляющими входами ко..торого я.вляются вторые входы элементов И второй Группы, первый вход второго элемента И и второй вход третьего счетчика импульсов, третьи входы элементов ШШ второй группы подключены к выходам второго регистра.

ж«

fO

rj

га-.

I

yf Of

re

гг

2f2Z

Авторы

Даты

1983-08-07—Публикация

1982-03-23—Подача