нулевому входу второго триггера, отличающееся тем, что,с целью расширения области применения за счет вычисления Г-функций от произвольного действительного аргумента, оно содержит сумматор, блок деления и блок постоянной памяти, а в блок управления введены группа дешифраторов и третий триггер, причем выходы первого блока элементов- И поразрядно подключены к информационному входу сумматора, выходы информационных разрядов сумматора подключены к информационньв4 входам второго и шестого блоков элементов И, выходы младших информационных разрядов сумматора подключены к адресным входам блока постоянной памяти, выходы блока постоянной памяти подключены к информационньи входам пятого и . седьмого блоков элементов И, выходы разрядов первого умножителя подключены к информационным входам восьмого блока элементов И, выходы шестого и восьмого блоков элементов И подключены к перЛэй и второй труппам входов второго блока элементов ИЛИ, выходы седьмого блока элементов И и выходы второго блока элементов ИЛИ подключены к входам разрядов делимо- го и делителя блока деления, выходы разрядов которого подключены к третьей группе входов первого блока элементов ИЛИ, входы первого дешифратора блока управления соединены с входами группы дешифраторов, первый выход группы дешифраторов является выходом ошибки устройства, второй выход группы дешифраторов подключен к нулевому входу первого триггера. 21 единичный выход которого, объёдиненный с нулевым входом третьего триггера, является пятым выходом блока управления и подключен к установочным входам первого и второго умножителей, блока деления и сумматора, знаковый выход сумматора подключен к первому входу первого элемента И блока управления, второй вход первого элемента И подключен к выходу второй группы второго дешифратора, выход первого элемента И подключен к второму вхо- ду второго элемента ИЛИ и к единичному входу третьего триггера, единичный выход третьего триггера подключен к первым входам .второго и третьего элементов И, нулевой выход третьего триггера подключен к первым входам четвертого и пятого элементов И, вторые .входы второго и четвертого элементов И подключены к выходу первого элемента ИЛИ, выходы второго и четвертого элементов И являются шестым и седьмым выходами блока управления и подключены соответственно к входу суммирования с единицей и входу вычитания единицы сумматора, третий выход первого дешифратора блока управления подключен к третьему входу третьего элемента ИЛИ и к вторьм входам третьего и пятого элементов И, выходы третьего и пятого элементов И подключены к входам четвертого элемента ИЛИ, выходы третьего, пятого элементов И и четвертого элемента ИЛИ являются восьмым девятым и десятьм выходами блока управления и подключены к управляющим входам восьмого, шестого и седьмого блоков элементов И соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Устройство для вычисления @ -функции | 1984 |

|

SU1241229A1 |

| Устройство для вычисления функций синуса и косинуса | 1984 |

|

SU1205140A1 |

| Устройство для решения дифференциальных уравнений | 1979 |

|

SU1023340A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ Г-ФУНКЦИЙ, содержащее блоки элементов И, ИЛИ, первый и второй умно ители, блок управления, содержащий первый и второй триггеры, формирователь импульсов, генератор тактов, счетчик, первый и второй дешифраторы, первый и второй элементы задержки, элементы И, ИЛИ, причем информа. ционный вход устройства поразрядно подключен к информационным входам первого блока элементов И, выходы второго блока элементов И подключены к информационным входам разрядов первого умножителя, выходы разрядов которого подключены к информационным входам третьего и четвертого блоков элементов И, выходы четвертого ипятого блоков элементов И подключены соответственно К первой и второй группам информационных входов второго умножителя, выходы третьего блока элементов И и выходы разрядов ;второго умножителя подключены соответственно к первой и второй группам ВХОДОВ первого блока элементов ИЛИ, выход которого является информационным выходом устройства, единичный вход первого триггера в блоке управления является входом запуска устройства, единичный выход Первого триггера подключен к входу первого элемента задержки, выход которого является первым выходом блока управления и подключен к управляющему входу первого блока элеЛнтов И, нулевой выход первого триггера подключен к входу формирователя импульсов, выход которого подключен к единичному входу второго триггера, выход второго триггера подключен к управляющему входу генератора тактов, выход которого подключен к входу счетчика, выход счетчика поразрядно под(Л ключен к входам первого дешифратора, первая группа выходов первого дешифратора подключена к входам первого элемента ИЛИ, выход которого через второй элемент задержки подключен к первому входу второго элемента ШШ, выход которого является вторым выходом блока управления и подключен к управляющему входу второго блока S9 элементов И, информационные входы 1 которого объединены с входами второго 9 дешифратора блока управления, первый и второй выходы второго дешифратора объединены соответственно с первым и вторым входами третьего элемента ИЛИ и являются третьим и четвертым выходами блока управления, причем третий выход блока управления подключен к управляющим входам четвертого и пятого блоков элементов И, а четвертый выход блока управления к управляющему входу третьего блока элементов И, выход третьего элемента ИЛИ блока управления подключен к

Изобретение относится к автоматике и вычислительной технике и может быть использовано при решении задач математической физики, требующих вычислений Г-функций. рГзвестно устройство для вычисления функций, содержащее блок степени полинома, генератор факториалов, блок умножения, блок вычисления но1меров коэффициентов, блок деления, блок коэффициентов полинома, и блок кратности дифференцирования Г13 Однако круг задач, решаемых этим устройством, не предусматривает числение значений Г-функций. Наиболее близким к предлагаемому является устройство для вычисления Г-функций, содержащее блоки элементов И, ИЛИ, регистр; аргумента, регистр константы, два умножителя и блок управления, причем информационные входы первого блока элементов И являются входами устройства, выходы первого блока элементов И подключены к разрядным входам регистра аргуменвторой блок элементов И подключены к информационным входам первого умно жителя, выходы разрядов которого под ключены к инфорг зционным входам третьего и четвертого блоков элементов И, вькоды разрядов регистра конс танты подключены к информационным входам пятого блока элементов И, выходЪ четвертого и пятого блоков I элементов И подключены к соответствующнм группам информационных входов второго умножителя 1 выходы разрядов второго умножителя и третьего блока элементов И подключены к соответству ющим группам входов блока элементов ИЛИ, выходы которого являются выходами устройства, управляющие входы регистров, умножителей и блоков элементов И подключены к соответствующим выходам блока управления 2 Недостаток известного устройства состоит в узких функциональных возможностях, ограниченных вычислением Г-функций только для положительного целого или полуцелого аргумента, представленного в естественной форме с запятой, разделающей целую и дробную части. Цель изобретения - расширение области применения за счет вычисления Г-функций от произвольного де ствительного аргумента. Поставленная цель достигается тем, что устройство для вычисления Г-функйцй, включающее в себя блоки элементов И, ИЛИ, первый и второй . умножители, блок управления, содерж щий первьй и второй триггеры, формиров тель импульсов, генератор такто счетчик, первый и второй дешифраторы первый и второй элементы задержки, элементы И, ИЛИ, причем информационный вход устройства поразрядно подключен к информационным входам перЗбго блока элементов И, выходы второго блока элементов И подключены к информационным входам разрядов первого умножителя, выходы разрядов которого подключены к информационным входам третьего и четвертого блоков элементов И, выходы четвертого и пятого блоков элементов И подключены соответственно к первой и второй 21 группам информационных входов второго умножителя, выходы третьего блока элементов И и выходы разрядов второго умножителя подключены соответственно к первой и второй группам входов первого блока элементов ИЛИ,, выход которого является информационным выходом устройства, единичный вход первого триггера в блоке управления является входом запуска устройства, единичный выход первого триггера подключен к входу первого элемента задержки, выход которого является первым выходом блока управ-ления и подключен к управляющему входу первого блока элементов И, нулевой выход первого триггера подключен к входу формирователя импульсов, выход которого подключен к единичному входу второго триггера, выход второго триггера подключен к управляющему входу генератора тактов, выход которого подключен к входу счетчика, выход счетчика поразрядно подключен к входам первого дй шифратора, первая группа выходов первого дешифратора псдключена к входам первого элемента ИЛИ, выход i которого через второй элемент задержки подключен к первому входу второго элемента ИЛИ, выход которого является вторым выходом блока управления и подключен к управляющему входу второго блока элементов И, информационные входы которого объединены с входами второго дешифратора блока управления, первьш и второй выходы второго де- шифратора объединены соответственно с первым и вторым входами третьего элемента ИЛИ н являются третьим и четвертым выходами блока управления, причем третий выход блока управления подключен к управляющим входам четвертого и пятого блоков элементов И, а четвертый выход блока управления к управляющему входу третьего блока элементов И, выход третьего элемента ИЛИ блока управления подключен к нулевому входу второго триггера, содержит сумматор, блок деления и блок постоянной памяти, а в блок управления введены группа дешифраторов и третий триггер, причем выходы первого блока элементов И поразрядно подключены к информационному входу сумматора, выходы всех информационных разрядов сумматора подключены к информационным входам второго и шеетого блоков элементов И, выходы младших информационных разрядов сумматора подключены к адресным входам блока, постоянной памяти, выходы блока постоянной памяти подключены к информационным входам пятого и седьмого блоков элементов И, выходы разрядов первого умн1ржителя подключены к информационным входам восьмого блока элементов-И, выходы шестого и вось- мого блоков элементов И подкдпочены к первой и второй группам входов второго блока элементов ИЛИ, выходы седьмого блока элементов И и выходы второго блока элементов ИЛИ подключены к входам разрядов делимого и делителя блока деления, выходы разрядов которого подключены к третьей группе входов первого блока элементов 11ПИ, входы первого дешифратора блока управления соединены с входами группы дешифраторов, первый выход группы дешифраторов является выходом ошибки устройства, второй выход группы дешифраторов подклочен к нулевому входу первого триггера, единичный выход которого, объединенный с нулевым входом третьего триггера, является пятым выходом блока управления и пoдкJлoчeн к установочным входам перво го и второго умножителей, блока деления и сумматора, знаковый выход сумматора подключен к первому входу лервого элемента И- блока управления, второй вход первого элемента И подключен к выходу второй группы второ.го дешифратора, выход первого элемента И подключен к второму входу второго элемента ИЛИ и к единичному входу третьего триггера, единичный выход третьего триггера подключен к первым входам второго и третьего элементов И, нулевой выход третьего триггера подключен к первым входам четвертого и пятого, элементов И, вторые входы второго и четвертого, элементов И подключены к выходу первого элемента ИЛИ, выходы второго и четвертого элементов И являются шестым и седьмьм выходШ4И блока управле ния и подключены соответственно к

входу суммирования с единицей и входУ вычитания единицы сумматора, третий выход первого дешифратора блока управления подключен к третьему входу третьего элемента ИЛИ и к вторым входам третьего и пятого элементов И, выходы третьего и пятого элементов И подключены к входам четвертого элемента ИЛИ, выходы третьего, пятого элементов И и четвертого элемента ИЛИ являются восьмым, девятым и десятым выходами блока управления и подключены к управляющим входам восьмого, шестого и седьмого блоков элементов И соответственно.

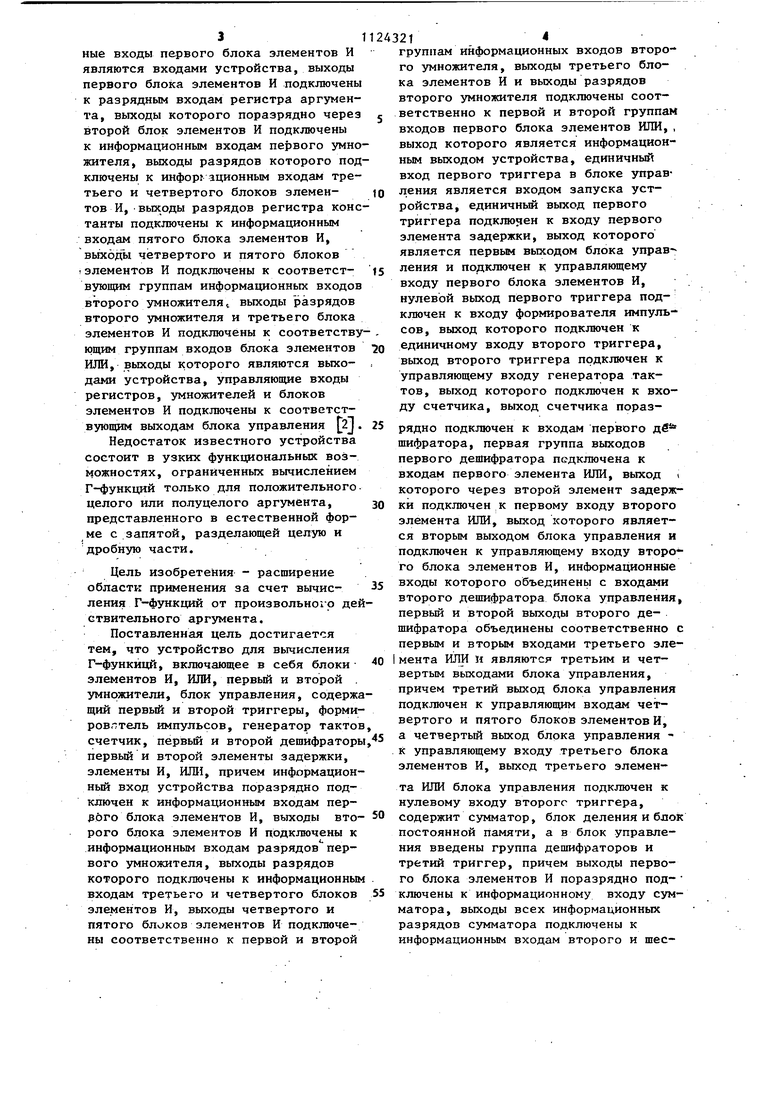

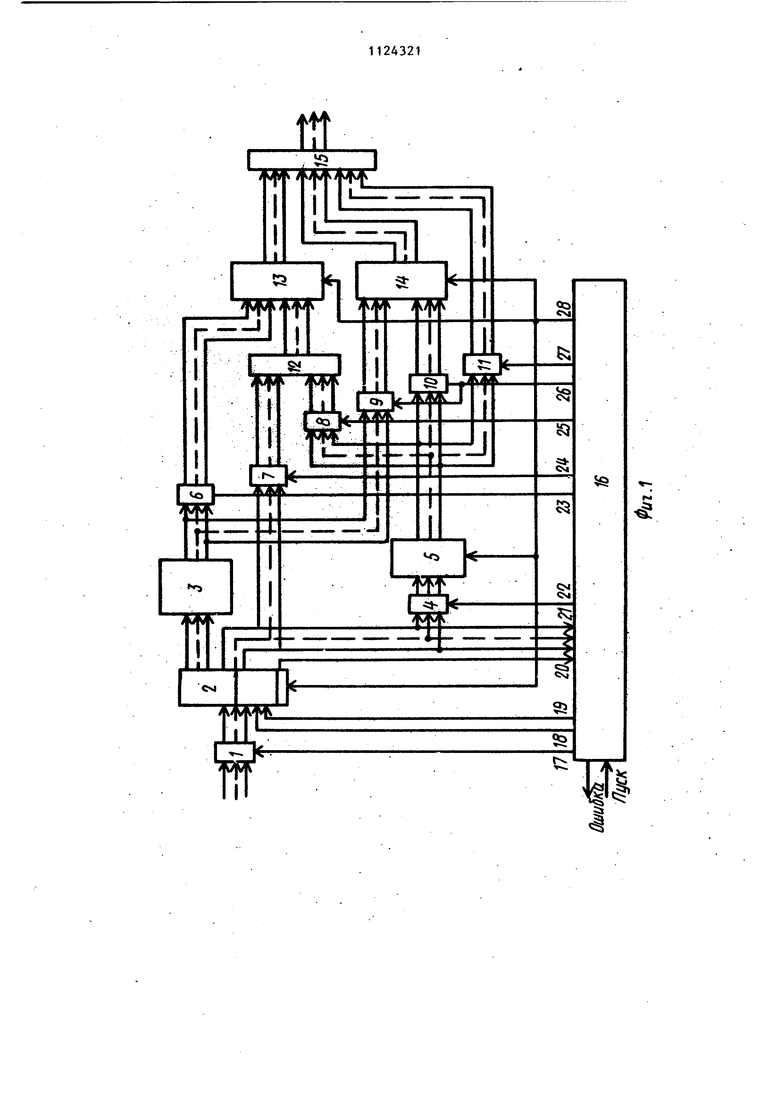

На фиг. 1 приведена функциональт ная схема предлагаемого устройства для вычисления Г-функций; на фиг.2 схема блока управления.

Устройство содержит блок 1 элементов И, сумматор 2, блок 3 постоянной памяти, блок 4 элементов И, умножитель 5, блоки. 6-11 элементов И блок 12 элементов ИЛИ, блок 13 деления, умножитель 14, блок 15 элементов ИЛИ, блок 16 управления, входывыходы 17,-28 блока управления.

Блок 16 управления содержит триг.гер.29, группу 30 дешифраторов, формирователь 31 импульсов, дешифратор 32, триггер 33, элемент ИЛИ 34, элементы И 35 и 36, генератор 37 тактов счетчик 38, депшфратор 39, элементы И 40 и 41, ИЛИ 42, И 43, ИЛИ 44, триггер 45, элемент ИЛИ 46, элементы 47 и 48 задержки.

Устройство работает следующим образом.

По команде Пуск триггер 29 устанавливается в единичное состояние и формирует управляющий сигнал .28, который приводит в единичное состоят кие умножитель 3 и устанавливает в нулевое состояние сумматор 2, умно житель 14, блок 13 деления и триггер 45. Этот же сигнал после задержки разрешает прием через блок 1 элементов И с входов устройства аргумента X в сумматор 2. Аргумент X с выходов суммАтора 2 подается на вход группы 30 дешифраторов, анализирующих аргумент X на равенство 0,-1,-2,

Если .-1,-2, ..., то формируется сигнал ошибки и работа устройства прекращается. Если ,-1,-2, ... то на другом выходе группы 30 дешифраторов формируется сигнал, устанавливающий триггер 29 в нулевое состояние. Одновременно с этим код аргумента X с выходов сумматора 2 подается на. дешифратора 32, знаковый разряд - на первый Вход элемента И 43.

Переход триггера 29 из единичного состояния в нулевое обеспечивает формирование на выходе формирователя 31 управляющего сигнала, который устанавливает триггер 33в единичное состояние. Под управлением единичного состояния триггера 33 генератор 37 тактов генерирует на своем выходе сигналы, которые подсчитываются счетчиком 38, Первому сигналу на выходе генератора 37 соответствует управляющий сигнал на первом выходе дешифра1тора 39, Если аргумент отрицательный , то этот сигнал проходит через элемент И 43, устанавливает триггер 45 в единичное состояние и, пройдя через элемент ИЛИ 46, разрешает передачу аргумента X из сумматора 2 через блок 4 элементов на входы умножителя 5, который выполняет умножение аргумента X на занесенное ранее в него значение (в первом такте Х1), Если аргумент положительный , то триггер 45 остается в нулевом состоянии и в первом такте запрещается передача аргумента X из сумматора 2 на входы умножителя 5,

По второму тактовому сигналу генератора 37 формируется управляющий сигнал на другом выходе дешифратора 39, Если аргумент , то этот сигнал с выхода дешифратора 39 проходит на вход сумматора 2 через элементы ИЛИ 44 и И 40, на другой вход которого подается разрешение с нулевого вькода триггера 45, и -выполняет вычитание единицы из содержимого сумматора 2, т,а, выполняется (Х-1), Если аргумент , то этот сигнал с выхода дешифратора 39 проходит на другой вход сумматора 2 через элементы ИЛИ 44 и И 41, на другой .вход которого в этом случае подается разрешение сединичного выхода триггера 45,; и вьшоляет суммирование единицы с содерж1 мым сумматора 2, т,е. выполняется (Х+1), Затем этот же сигнал после задержки, пройдя через элемент ИЛИ 46, разрешает передачу содержимого сумматора 2 через блок 4 элементов И на входы умножителя 5, вкотором выполняется умножение очередкого кода сумматора 2 с пред еду-т щим значением произведения, т,е, на втором такте, выполняется (Х+1)Х для и (Х-1) для , По третьему и остальным тактовым сигналам повторяется процесс, аналогичный процессу на втором такте, т,е, .в умножителе 5 накапливается одно из произведений

(Х-1)(Х-2) .,, (Х-К), , (1)

Х(Х+1)(Х-ь2) ,,, (Х+К),

X 0 и X э -1,-2 ,,. (2)

Генератор 37 генерирует тактовые сигналы до тех пор, пока дешифратор 32 не находится в одном из трех состояний, зависящих от текущего содержимого X сумматора 2. Если аргумент X - полоижетльное целое число, то

Г(Х) (Х-1) ,

и процесс вычисления произведения (1) останавливается в момен-т равенства содержимого сумматора 2 единице т,е, , При этом на .первом выходе дешифратора 32 формируется управляющий сигнал 27, который через элемент ИЛИ 42 возвращает триггер 33 в нулевое состояние и, теМ самым, запрещает работу генератора 37, Этот же сигнал разрешает передачу из умножителя 5 вычисленного факториала (Х-1) через блок 11 элементов И и блок 15 элементов ИЛИ на выход устройства.

Если аргумент положительный дробный Xfe(0,1), то Г(Х) вычисляется как отношение

Г()

Г(Х)

при этом дешифратор 32 формирует управляющий сигнал на третьем выходе сразу после приема аргумента X в сумматор 2, Этот управляющий сигнал через элемент ИЛИ 42 устанавливает триггер 33 в нулевое состояние и запрещает работу генератора 37 (произведение (1) при этом не вычисляется) , Этот же сигнал с выхода дешифратора 32 проходит через элемент И 35, на другой вход которого подается разрешение с нулевого выхода триггера 45, и разрешает передачу аргумента X из сумматора 2 через блок 7 элементов И и блок 12 элементов ИЛИ в блок 13 деления. Одновременно с этим управляющий сигнал с выхода элемента И 35 через элемент ИЛИ 34 подается на управляющий вход блока 6 элементов И и разрешает гьередачу из блока 3 постоянной памяти значения Г(Х+1), выбираемого по адресу X, на другие входы блока 13 делеГ(Х+1) из блока 13 ния. Результат деления через блок 15 элементов ИЛИ передается на выход устройства. Если аргумент положителен, и принадлежит интервалу Хб(1,2), то дешиф ратор 32 формирует управляющий сигнал 26 на втором выходе сразу после приема аргумента X в сумматор 2, Это сигнал устанавливает триггер 33 в нулевое состяние, запрещает работу генератора 37 (произведение (1) при этом не вычисляется) и одновременно разрешает передачу через блок 9 элементов И из блока 3 постоянной памяти на один из входов умножителя 14 значения Г(х), выбираемого по адресу соответствующему дробчой части аргумента X, и через блок 10 элементов И из умножителя 5 на другой вход умножителя 14 передается значение единицы, содержащееся в нем. Результат Г(х)Г(Х)1 из умножителя 14 через блок 15 элементов ИЛИ передается на выход уртройства. Если аргумент , то Г(Х) вычисляется как произведение (Хк). Г(Х)(Х-1)(Х-2) в этом случае начальный процесс аналогичен процессу, когда аргумент X - положительное целое число, до те пор, пока в сумматоре 2 не останется значение (1,2). При этом дешифратор 32 формирует управляющий сигнал 26 на втором выходе, который через элемент ИЖ 42 останавливает работу генератора 37, подается на управляющий вход блоков 9 и 10 элементов И и разрешает передачу в умн житель 14 соответственно из умножителя 5 накопленного произведения (Х-1)-(Х-2), Xj; и из блока 3 постоян ной памяти значения Г (Х), выбранного по адресу, определяемому дробной частью X,,, т.е. (Хц-1). Результат в соответствии, с выражением (3) из умножителя 14 через блок 15 элементов ИЛИ передается на выход устройства. Если аргумент и ,2, ..., то вычисляется отношение Г() X.Тх+ о(х+2) ...X В этом случае начальный процесс выполняется аналогично выражению (2) для отрицательного аргумента X - в умножителе 5 накапливается произведение. Х(Х+1) (Х+2) ... Х, пока X не ок зывается в диапазоне (0,1). При этом дешифратор 32 на третьем выходе формирует управляющий сигнал, который останавливает работу генератора 37. Этот же сигнал с выхода дешифратора 32 проходит через элемент И 36, на другой вход которого подается разрешение с единичного выхода триггера 45, и разрешает передачу через блок 8 элементов И и блок 12 элементов ИЛИ на входы блока 13 деления из умножителя 5 накопленного произведения Х(Х+1)«(Х+2) ...X. Одновременно с этим управляющий сигнал с выхода элемента И 36 проходит через .элемент ИЛИ 34 и разрешает передачу через блок 6 элементов И на другие входы блока 13 деления из блока 3 постоянной памяти значения Г(), выбранного по адресу Х Результат в соответствии с вьфажением (4) из блока 13 деления через блок 15 элементов ИГМ передается на выход устройства. Функциональные возможности предлагаемого устройства для вычитания Г-функции расширены - обеспечено вычисление Г-функции произвольного действительного аргумента, представленного в естественной форме или с ;плавающей запятой.

tn

щ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для дефференцирования алгебраических полиномов | 1973 |

|

SU487391A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления Г-функций | 1979 |

|

SU922759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-25—Подача