(54) ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1983 |

|

SU1132344A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Динамический логический элемент | 1979 |

|

SU822370A1 |

| Многоуровневая ячейка памяти | 1980 |

|

SU1067534A1 |

| Регистр сдвига | 1980 |

|

SU883973A2 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU868836A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Т-триггер (его варианты) | 1984 |

|

SU1226615A1 |

| Преобразователь уровня для усилителя считывания | 1987 |

|

SU1492381A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

1

Изобретение относится к области вычислительной техники и микроэлектроники, а более конкретно - к ячейкам па.мяти для микроэлектронных регистров сдвига.

Известны микроэлектронные регистры сдвига, которые полностью построены на совмещенных транзисторных структурах и обеспечивают вьгсокую степень интеграции элементов при выполнении их в составе БИС и низкую потребляемую мощность 1.

Наиболее близким к изобретению техническим решением является ячейка памяти, содержащ ая триггеры, выполненные на транзисторах, эмиттеры которых соединены с базой входного транзистора, базой опорного транзистора и щиной нулевого потенциала, коллекторы входного транзистора подключены соответственно к базам вторых транзисторов триггеров, эмиттер входного транзистора соединен с входной шиной, эмиттер опорного транзистора соединен с шиной питания, выходную и тактовую шины 2.

Известные ячейки памяти обладают низким быстродействием.

Цель изобретения.- повышение быстродействия ячейки памяти.

Поставленная цель достигается тем, что в нее введены транзисторы связи, токозадающий транзистор, блокировочный транзистор и выходные транзисторы, коллекторы которых соединены с выходной шиной, эмиттеры выходных транзисторов соединены с базами первых транзисторов тригге. ров и с первыми коллекторами токозадающего транзистора, а базы - с базами транзисторов связи, эмиттером блокировочного транзистора, базой токозадающего транзистора и шиной нулевого потенциала, э.миттеры транзисторов связи соединены с коллекторами опорного транзистора и коллекторами блокировочного транзистора, коллекторы транзисторов связи подключены к базам первых транзисторов триггеров, вторые коллекторы токозадающего транзистора соединены с базами вторых транзисторов триггеров, ба.за блокировочного транзистора соединена с эмиттером токозадающего транзистора и тактовой шиной.

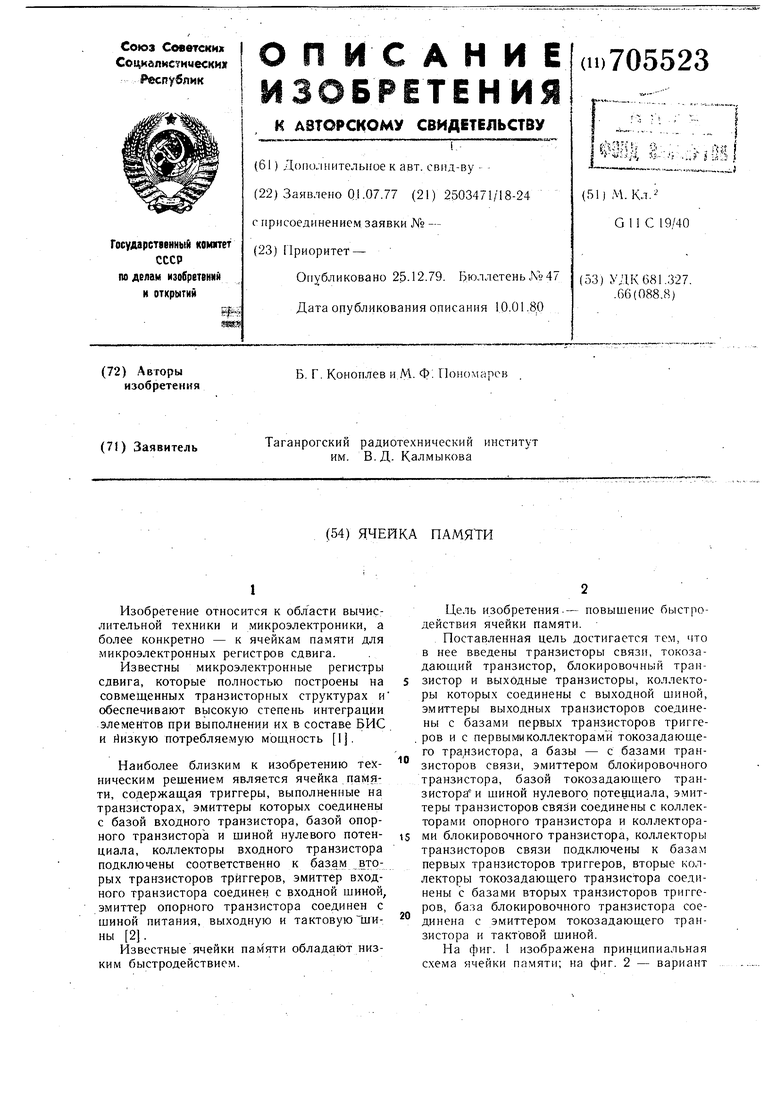

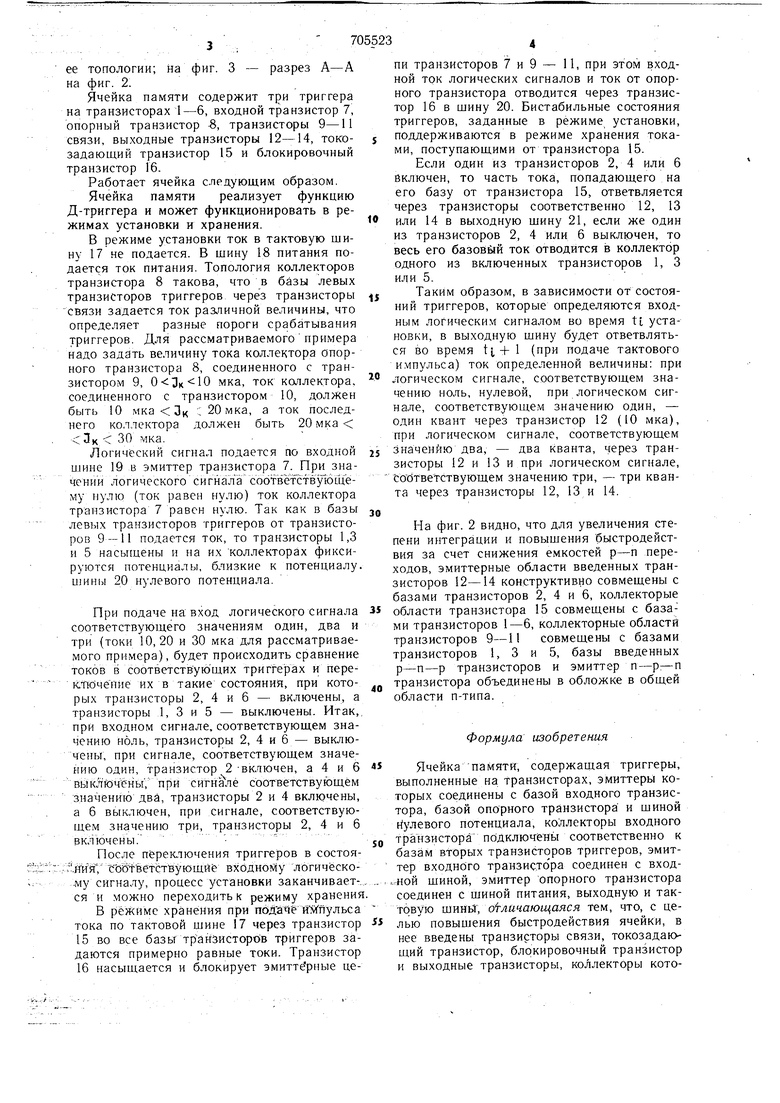

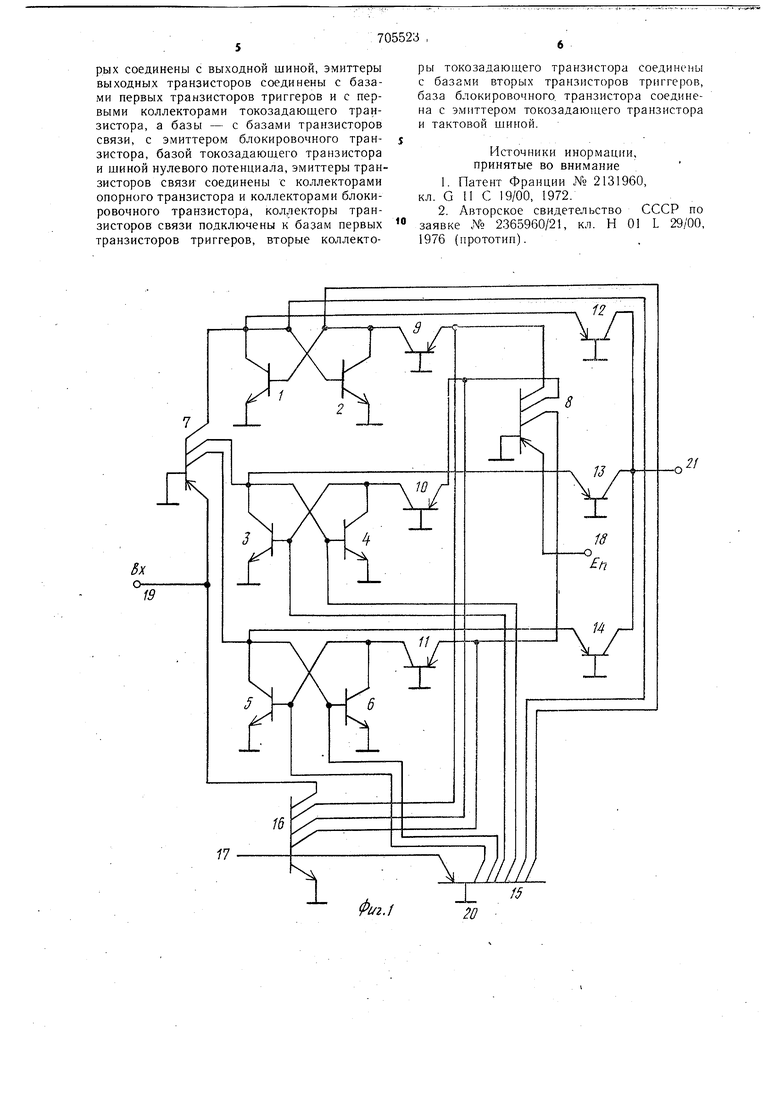

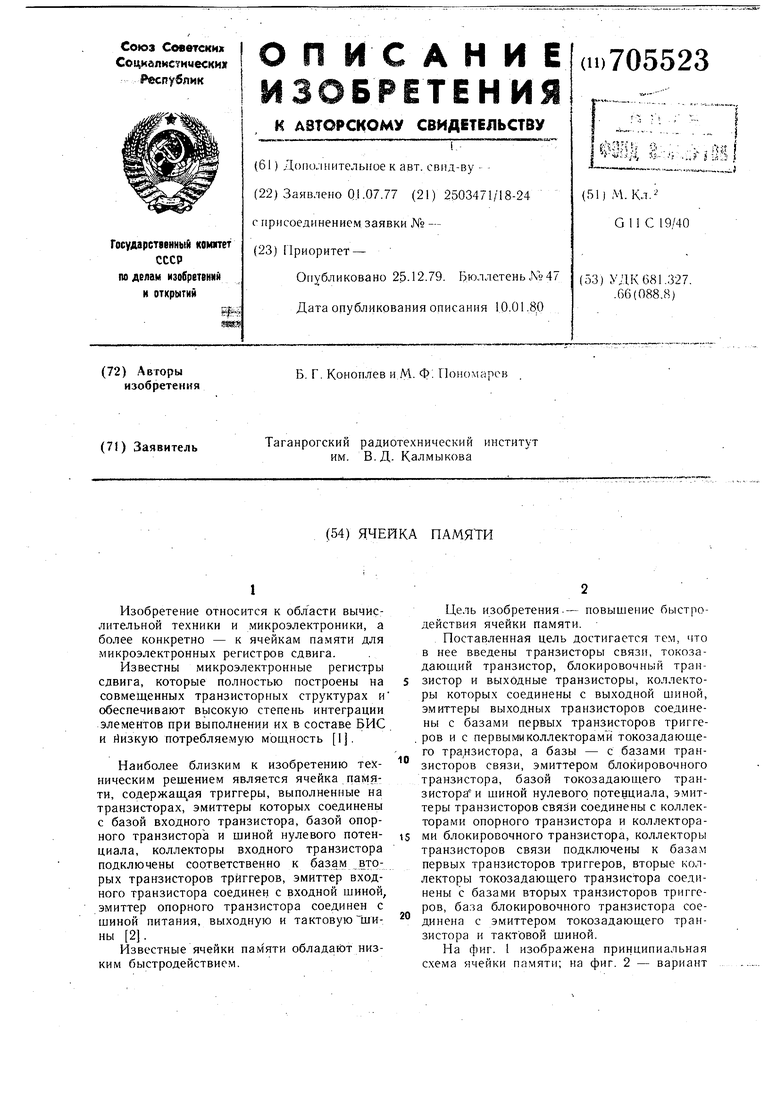

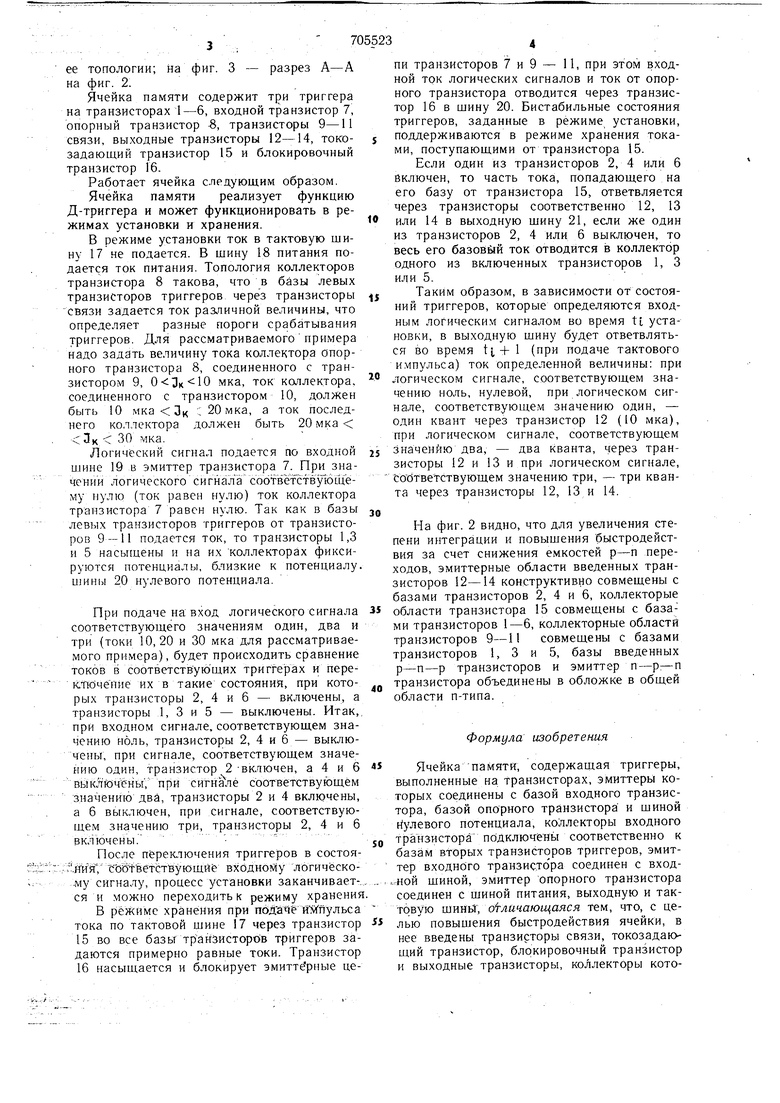

На фиг. 1 изображена принципиальная схема ячейки памяти; на фиг. 2 - вариант ее топологии; на фиг. 3 - разрез А-А на фиг. 2. Ячейка памяти содержит три триггера на транзисторах 1-6, входной транзистор 7, опорный транзистор -8, транзисторы 9-11 связи, выходные транзисторы 12-14, токозадающий транзистор 15 и блокировочный транзистор 16. Работает ячейка следующим образом. Ячейка памяти реализует функцию Д-триггера и может функционировать в режимах установки и хранения. В режиме установки ток в тактовую шину 17 не подается. В шину 18 питания подается ток питания. Топология коллекторов транзистора 8 такова, что в базы левых транзисторов триггеров через транзисторы СВЯЗИ задается ток различной величины, что определяет разные пороги срабатывания триггеров. Для рассматриваемого примера надо задать величину тока коллектора опорного транзистора 8, соединенного с транзистором 9, мка, ток коллектора, соединенного с транзистором 10, должен , 10 мка 3к - 20 мка, а ток последнего коллектора должен быть 20 мка Лк 30 мка. Логический сигнал подается по входной шине 19 в эмиттер транзистора 7. При значении логического сигнала соответствуТощему нулю (ток равен нулю) ток коллектора транзистора 7 равен нулю. Так как в базы левых транзисторов триггеров от транзистоpoEi 9-11 подается ток, то транзисторы 1,3 и 5 насыщены и на их коллекторах фиксируются потенциалы, близкие к потенциалу, тины 20 нулевого потенциала. При подаче на вход логического сигнала соответствующего значениям один, два и три (токи 10,20 и 30 мка для рассматриваемого примера), будет происходить сравнение токов в соответствующих триггерах и переклточёние их в такие состояния, при которых транзисторы 2, 4 и 6 - включены, а транзисторы 1, 3 и 5 - выключены. Итак, при входном сигнале, соответствующем значению ноль, транзисторы 2, 4 и 6 - выключены, при сигнале, соответствующем значению один, транзистор 2-включен, а 4 и 6 вЬ1ключенЬ ; при ситна лё соответствующем значению двй, транзисторы 2 и 4 включены, а 6 выключен, при сигнале, соответствующем значению три, транзисторы 2, 4 и 6 включены. После переключения триггеров в состоя-.йгй; собГветСтвующйе входному логичёско.му сигналу, процесс установки заканчивает-. ся и можно переходить к режиму хранения В режиме хранения при пбдаЧе йШульса тока по тактовой шине 17 через транзистор 15во все базы трайэисторбв триггеров задаются примерно равные токи. Транзистор 16насыщается и блокирует эмиттфные цепи транзисторов 7 и 9 -- 11, при этом входной ток логических сигналов и ток от опорного транзистора отводится через транзистор 16 в шину 20. Бистабильные состояния триггеров, заданные в режиме установки, поддерживаются в режиме хранения токами, поступаюш,ими от транзистора 15. Если один из транзисторов 2, 4 или 6 включен, то часть тока, попадающего на его базу от транзистора 15, ответвляется через транзисторы соответственно 12, 13 или 14 в выходную щину 21, если же один из транзисторов 2, 4 или 6 выключен, то весь его базовйй ток отводится в коллектор одного из включенных транзисторов 1, 3 или 5. Таким образом, в зависимости от состояний триггеров, которые определяются входным логическим сигналом во время tl установки, в выходную шину будет ответвляться во время tj,-l- 1 (при подаче тактового импульса) ток определенной величины: при логическом сигнале, соответствующем значению ноль, нулевой, при логическом сигнале, соответствующе.м значению один, - один квант через транзистор 12 (10 мка), при логическо.м сигнале, соответствующем значению два, - два кванта, через транзисторы 12 и 13 и при логическом сигнале, Соответствующем значению три, - три кванта через транзисторы 12, 13 и 14. На фиг. 2 видно, что для увеличения степени интеграции и повышения быстродействия за счет снижения емкостей р-п переходов, эмиттерные области введенных транзисторов 12-14 конструктивно совмещены с базами транзисторов 2, 4 и 6, коллекторые области транзистора 15 совмещены с базами транзисторов 1-6, коллекторные области транзисторов 9-II совмещены с базами транзисторов 1, 3 и 5, базы введенных р-п-р транзисторов и эмиттер п-р:-п транзистора объединены в обложке в общей области п-типа. Формула изобретения Ячейка памяти, содержащая триггеры, выполненные на транзисторах, эмиттеры которых соединены с базой входного транзистора, базой опорного транзистора и шиной Нулевого потенциала, коллекторы входного транзистора пОДключёнь соответственно к базам вторых транзисторов триггеров, эмиттер входного транзистора соединен с входной шиной, эмиттер опорного транзистора соединен с шиной питания, выходную и тактовую шины, обличающаяся тем, что, с целью повышения быстродействия ячейки, в нее введены транзисторы связи, токозадающий транзистор, блокировочный транзистор и выходные транзисторы, коллекторы которых соединены с выходной шиной, эмиттеры выходных транзисторов соединены с базами первых транзисторов триггеров и с первыми коллекторами токозадающего транзистора, а базы - с базами транзисторов связи, с эмиттером блокировочного транзистора, базой токозадающего транзистора и шиной нулевого потенциала, эмиттеры транзисторов связи- соединены с коллекторами опорного транзистора и коллекторами блокировочного транзистора, коллекторы транзисторов связи подключены к базам первых транзисторов триггеров, вторые коллекторы токозадающего транзистора соединены с базами вторых транзисторов триггеров, база блокировочного, транзистора соединена с эмиттером токозадающего транзистора и тактовой шиной.

..

Источники инормации, принятые во внимание

1976 (прототин).

18 п

-In

Авторы

Даты

1979-12-25—Публикация

1977-07-01—Подача