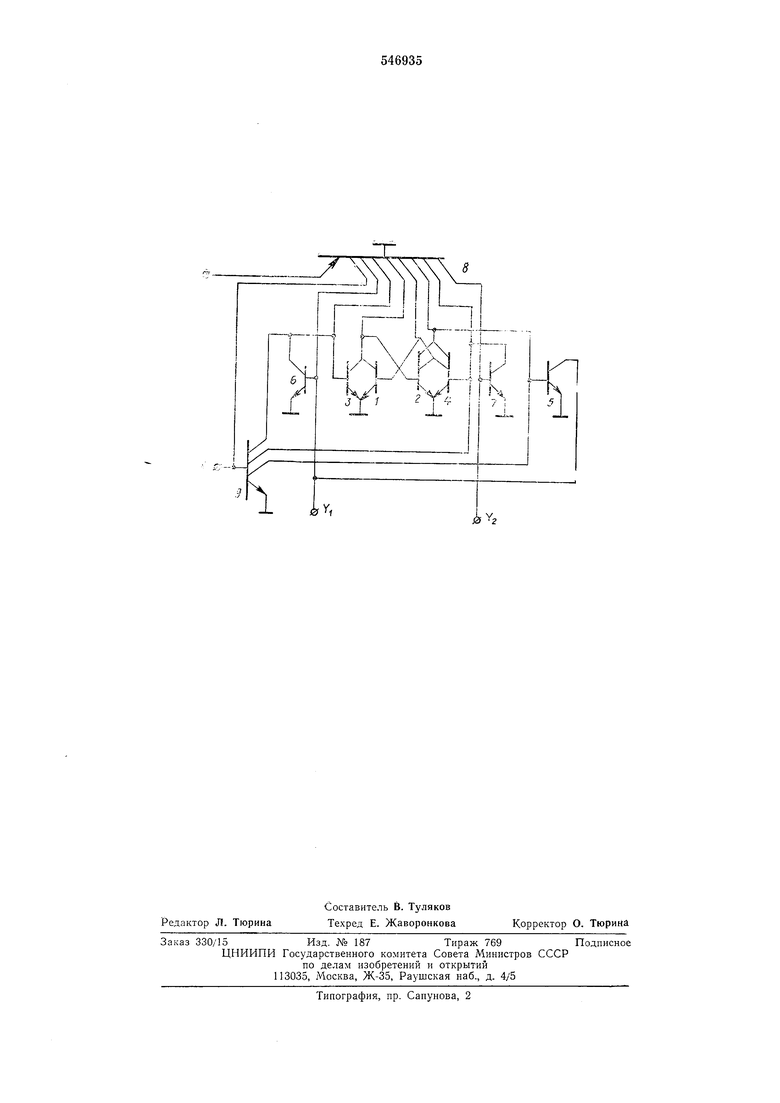

4, коллекторы которых соединены с коллекторами транзисторов 1 и 2, входные транзисторы 5 и 6, на базе которых с разрядных шин /1, YZ подаются сигналы записи, транзистор 7, служаш,ий для вывода информации при считывании, р-«-/ -транзистор 8, управляющий режимом работы (выборка или хранение) и «-/7-«-транзистор 9, задающий ток питания в базы всех л-/7-«-транзисторов.

В режиме хранения на базу транзистора 8 подается сигнал «логической единицы (ток в щине X равен «О), транзистор 9 - включен, а транзисторы 3, 4 и 7 - закрыты. Сигналы с шин У и /2 не могут пройти на базы транзисторов il II 2, и триггер на этих транзистоpax хранит информацию. В свою очередь сигнал с выхода триггера не может пройти на шину YI, так как транзистор 7 закрыт.

В режиме выборки на базу транзистора 8 через щину X подается сигнал «логического нуля, запирающий этот транзистор.

В режиме записи на разрядных щинах в противофазе устанавливается пульная информация, которая и записывается в триггер.

Например, если на шине Yi - сигнал «О, а на щпне YZ - сигнал «1, то транзистор 5 - выключен, а транзистор 3 включается, и на левом плече триггера (коллектор транзистора 1) устанавливается «О.

Б режиме считывания на шине У2 устанавливается сигнал «логической единицы (ток в шине равен «О), а шина У подключается ко входу усилителя считывания. Сигнал на шине Yi определяется состоянием триггера. Если транзистор I включен, то на шине /i появляется сигнал «логического нуля (напряжение, близкое к «О, поддерживаемое открытым транзистором 7). Если транзистор 1 выключен, то сигнал на шине YI соответствует «логической единице (ток в шине равен «О).

Описывае.мая ячейка, в отличие от известных, содержит две, а не три разрядных шины, что упрощает создание межсоединений и уменьшает площадь накопителя. Кроме того, в ней нет необходимости во втором многоколлекторном р-«-р-транзисторе п разделительных областях, требующих для своего создания дополнительной технолотической операции. Этим достигается положительный эффект - упрощение ячейки и накопителя.

Ф о р м } л а изобретения

Ячейка памяти, содержащая первый п-р-птранзистор и второй многоколлекторный /г-/з-л-транзистор с перекрестпыми связями, третий и четвертый «-/7-л-транзисторы, коллекторы которых соединены соответственно с коллектором первого л-р-л-транзистора и первым коллектором второго л-р-п-транзкстора, иятый л-р-л-транзистор, база которого соединена со вторым коллектором второго л-р-лтранзистора, а коллектор - с разрядной шиной, шестой и седьмой л-р-л-транзисторы, коллекторы которых соединены соответственно с базами третьего и четвертого л-р-л-транзисторов, причем база седьмого л-р-л-транзистора соединена со второй разрядной шиной, восьмой многоколлекторный р-л-р-транзистор, коллекторы которого подключены соответственно к базам первого, второго, шестого и седьмого л-р-л-транзисторов, а эмиттер - к шине питания, шину нулевого потенциала и шину выборки, отличающаяся тем, что, с целью упрощения ячейки памяти, она содержит девятый многоколлекторный п-р-птранзистор, база которого подключена к щине выборки, а коллекторы - соответственно к базам третьего, четвертого и пятого л-р-лтранзисторов, дополпительный коллектор четвертого л-р-л-транзистора, соединенный с базой пятого л-р-л-транзистора, причем база шестого л-р-л-транзистора соединена с коллектором пятого л-р-л-транзистора, четыре дополнительных коллектора восьмого р-л-ртранзнстора, соединенные соответственно с базами третьего, четвертого, пятого и девятого л-р-д-траизисторов.

1 V---t

A/ 4-4

a I

| название | год | авторы | номер документа |

|---|---|---|---|

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Ячейка памяти | 1977 |

|

SU637866A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Ячейка памяти для регистра сдвига | 1979 |

|

SU851495A1 |

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Интегральная ячейка памяти | 1973 |

|

SU566268A1 |

| Способ записи и считывания информации в запоминающих устройствах с инжекционным питанием и устройство для его осуществления | 1975 |

|

SU646371A1 |

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Одноразрядный сумматор | 1982 |

|

SU1043641A2 |

Авторы

Даты

1977-02-15—Публикация

1974-02-01—Подача