Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, устройствам для записи и считывания информации в цифровых запоминающих устройствах, и может быть использовано во внешних устройствах ЭВМ.

Известно оперативное запоминающее устройство, содержащее накопители, счетчик, элемент ИЛИ, триггеры, элементы 2 И-ИЛИ-, НЕ, ИЛИ-НЕ и элемент НЕ, причем одни из входов накопителей подключены к одним из выходов счетчика, а другие - соответственно к выходам элементов 2И-ИЛИ-НЕ и ИЛИ-НЕ, выход элемента ИЛИ соединен со счетным входом счетчика, единичные выходы триггеров подключены к одним из входов элементов 2И-ИЛИ-НЕ, другие входы которых соединены соответственно с входами элемента ИЛИ, являющимися соответственно входами чтения и записи устройства I.

Недостатками этого устройства являются сложность управления записью и считыванием и невысокая достоверность информации, хранимой в нем.

Наиболее близким к предлагаемому является запоминающее устройство с самоконтролем, содержащее накопители, выходы которых подключены к входам блоков контроля и входам блоков сравнения, соединенным регистрами, связанными с дещифраторами, блок формирования сигнала отказа, подключенный к блоку задержки строба 2.

Недостатками этого устройства являются больщие аппаратурные затраты и связанная с ними недостаточная надежность.

Цель изобретения - упрощение и повыщение надежности устройства.

Поставленная цель достигается тем, что в оперативное запоминающее устройство с автономным контролем, содержащее блоки памяти, адресные входы которых соединены с выходами счетчика, а выходы подключены к одним из входов блока контроля по четности, выход которого является управляющим выходом устройства, введены генератор импульсов, триггеры с первого по третий, элементы И с первого по пятый и элементы И-НЕ с первого по одиннадцатый, причем одни из входов сброса триггеров и счетчика являются первым управляющим входом устройства, вторым управляющим входом которого является установочный .вход второго триггера, единичный выход которого соединен с входом генератора импульсов, с первыми входами пятого элемента И. элементов И-НЕ с седьмого по десятый и информационным входом третьего триггера, выход генератора импульсов подключен к второму входу пятого элемента И, к первым входам элементов И с первого по четвертый и к счетному входу первого триггера, единичный выход которого соединен со счетным входом третьего триггера, с первым входом первого элемента И-НЕ и с вторыми входами элементов И-НЕ с седьмого по десятый, нулевой выход первого триггера соединен с информационным входом того же триггера, единичный выход третьего триггера соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым входом щестого элемента И-НЕ, второй вход которого является третьим управляющим входом устройства, первые входы элементов И-НЕ с второго по пятый являются четвертым управляющим входом устройства, а вторые - соответственно управляющими . входами устройства с пятого по восьмой,

выходы элементов И-НЕ с второго по пятый соединены соответственно с вторыми входами элементов И с первого по четвертый, выходы элементов И-НЕ с седьмого по десятый подключены к информационным входам соответствующих блоков памяти, управляющие входы которых соединены с выходами элементов И с первого по четвертый, выход пятого элемента И подключен к другому входу блока контроля по четности, одни из выходов счетчика соединены с входами одиннадцатого элемента И-НЕ, выход которого соединен с другими входами сброса счетчика и триггеров, счетный вход счетчика к выходу щестого элемента И-НЕ.

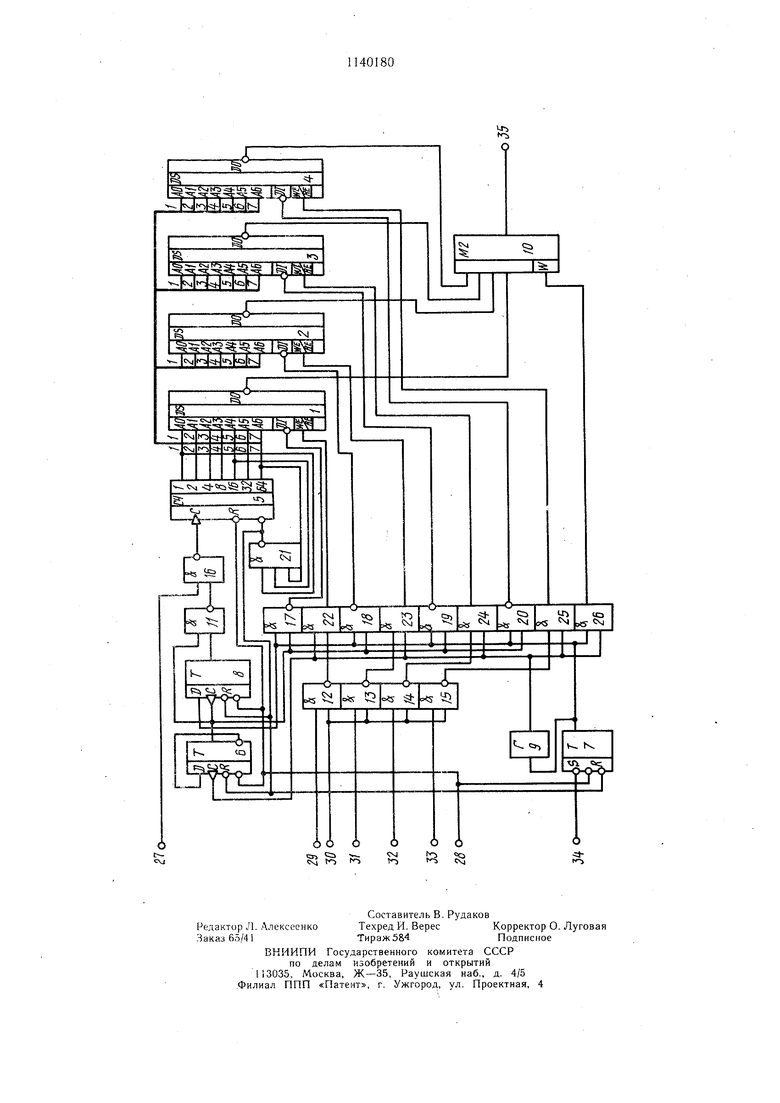

На чертеже изображена структурная схема предлагаемого оперативного запоминающего устройства с автономным контролем.

Оперативное запоминающее устройство с автономным контролем содержит блоки

--4 памяти, выполненные, например, на микросхемах типа 565 РУ 2, счетчик 5, триггеры 6-8 с первого по третий, генератор 9 импульсов, блок 10 контроля по четкх:)сти, элементы И-НЕ 11-21 с первого по одиннадцатый, элементы И 22-26 с первого.по пятый.

Устройство имеет управляющие входы 27-34 и выход 35.

Запоминающее устройство может работать в трех режимах: проверка ЗУ контрольными кодами; запись информации; считывание информации.

В режи.ме проверки ЗУ контрольными кодами устройство работает следующим образом.

Q Перед началом работы импульсом отрицательной полярности с входа 28 счетчик 5, триггеры 6 и 7 устанавливаются в исходное нулевое состояние. В этом режиме на входах 29-33 постоянно присутствует уровень логического нуля, а на входе 27 - уровень

5 ./ огической единицы. При поступлении на вход 34 импульса отрицательной полярности на выходе триггера 7 появляется уровень логической единицы, который разрешает

работу генератора 9. На выходе генератора 9 появляется импульс отрицательной полярности. Перед ним фронтом этого импульса перебрасывается триггер 6, на нулевом выходе которого появляется уровень логического нуля. На выходах элементов И-НЕ 17-20 появляется уровень логической единицы, на выходах элементов И 22-25 - уровень логического нуля. Происходит запись логической единицы в блоки 1-4 по адресу 0000000. После окончания импульса отрицательной полярности на выходе элементов И 22-25 появляется уровень логической единицы. Происходит считывание информации из блоков 1-4 по адресу 0000000. С выходов блоков 1-4 уровни логической единицы поступают на входы блока 10 контроля по четности. На выходе элемента И 26 появляется уровень логической единицы, который разрешает контроль информации в блоке 10. В случае нечетной (Ошибочной) информации формируется уровень логической единицы на -выходе блока 10. Затем на выходе генератора 9 появляется второй импульс отрицательной полярности. По переднему фронту этого импульса перебрасывается триггер 6, на его нулевом выходе появляется уровень логического нуля. На единичном выходе триггера 8 появляется уровень логической единицы. На выходах элементов И-НЕ 17-20 появляется уровень логического нуля. На входах элементов И 22-25 появляется уровень логического нуля. Происходит запись логического нуля в блоки 1-4 по адресу 0000000. После окончания импульса отрицательной полярности на выходе элементов И 22-25 появляется уровень логической единицы. Происходит считывание информации из блоков по адресу 0000000. С выходов блоков 1-4 уровни логического нуля поступают на входы блока 10. На выходе элемента И 26 появляется уровень логической единицы, который разрешает контроль информации в блоке 10. В случае нечетной (ошибочной)информации формируется уровень логической единицы на выходе блока 10. Затем на выходе генератора 9 появляется третий импульс отрицательной полярности. По этому импульсу перебрасывается триггер 6, на единичном выходе которого появляется уровень логического нуля. На выходе элемента И-НЕ 16 появляется уровень логической единицы, по положительному фронту которого на счетчике устанавливается адрес 0000001. Происходит запись-считывание в блоки 1-4 сначала уровня -логической единицы, затем уровня логического нуля по -описанному принципу. Так происходит проверка блоков 1-4 и запись в них по всем адресам уровней логического нуля. После установки на счетчике 5 адреса 1010001 на выходе элемента И-НЕ 21 появляется отрицательный уровень,

который устанавливает устройство в исходное состояние (сбрасываются счетчик 5, триггеры 6-8). На этом заканчивается проверка ЗУ контрольными кодами.

В режиме записи информации устройство

работает следуюш.им образом.

Формируется положительный импульс разрешения записи. Если во время действия этого импульса на одном из входов 29,31 - 33 появляется положительный сигнал, то

происходит запись в ячейку памяти уровня логической единицы (на выходах элементов И-НЕ 12,И 22 и триггера 7 присутствует уровень логического нуля, на выходе элемента И-НЕ 17 - уровень логической единицы). Если на указанном входе отсутствует

положительный импульс, то в ячейках памяти остается уровень логического нуля (который был записан при проверке ЗУ контрольными кодами). Затем при поступлении отрицательного импульса по входу 27 изменяется адрес ячейки памяти. Процесс записи информации повторяется. После записи информации в ячейку с адресом 1010000 по входу 28 поступает отрицательный импульс, который устанавливает в начальное состояние счетчик 5.

В режиме считывания информации устройство работает следующим образом.

В течение всего режима на выходе триггера 7 постоянно присутствует уровень логического нуля, на выходе генератора 9 -

уровень логической единицы, на выходе 30 - уровень логического нуля, на выходе элементов И-НЕ 12-15 - уровень логической единицы, на выходе элементов И 22-25- уровень логической единицы.

Устройство находится в режиме считывания информации из ячейки с адресом 0000000. При поступлении отрицательного импульса по входу 27 изменяется адрес ячейки (0000001). Происходит считывание информации из этой ячейки. После считывания

информации из ячейки с адресом 1010000 отрицательным импульсом по входу 28 счетчик 5 устанавливается в начальное состояние.

Изобретение позволяет строить запоминающие устройства с большим объемом памяти при относительно простой схеме управления. Это, в свою очередь, повышает надежность работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации с перфокарт | 1980 |

|

SU940187A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU826419A1 |

| Запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1317484A1 |

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU830386A1 |

| Устройство для микропрограммногоупРАВлЕНия C КОНТРОлЕМ | 1979 |

|

SU809183A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1283858A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896621A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Устройство для сигнализации | 1985 |

|

SU1278913A1 |

ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНО.МНЫМ КОНТРОЛЕМ, содержащее блоки памяти, адресные входы которых соединены с выходами счетчика, а выходы подключены к одним из входов блока контроля по четности, выход которого является управляющим выходом устройства, отличающееся тем, что, с целью упрощения и повыщения надежности устройства, в него введены генератор импульсов, триггеры с первого по третий, элементы И с первого по пятый и элементы И-НЕ с первого по одиннадцатый, причем одни из входов сброса триггеров и счетчика являются первы.м управляющим входом устройства, вторым управляющим входом которого является установочный вход второго триггера, единичный выход которого соединен с входом генератора импульсов, с первыми входами пятого элемента И, элементов И-НЕ с седьмого по десятый и информационным входом третьего триггера, выход генератора импульсов .подключен к второму входу пятого элемента И, к первым входам элементов И с первого по четвертый и к счетному входу цервого триггера, единичный выход которого соединен со счетным входом третьего триггера, с первым входом первого элемента И-НЕ и с вторыми входами элементов И-НЕ с седьмого по десятый, нулевой выход первого триггера соединен с информационным входом того же триггера, единичный выход третьего триггера соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым входом шестого элемента И-НЕ, второй вход кот.орого является третьим управляющим входом устройства, первые входы элементов И-НЕ с второго по пятый являются четвертым управляющим входом устройства, а 3. вторые - соответственно управляющими входами устройства с пятого по восьмой, ел выходы элементов И-НЕ с второго по пятый соединены соответственно с вторыми входами элементов И с первого по четвертый, выходы элементов И-НЕ с седьмого по десятый подключены к информационным входам соответствующих блоков памяти, управляющие входы которых соединены с выходами элементов И с первого по четвертый, 4 выход пятого элемента И подключен к другому входу блока контроля по четности, одни из выходов счетчика соединены с входами одиннадцатого элемента И-НЕ, выход ко00 о торого соединен с другими входами сброса счетчика и триггеров, счетный вход счетчика подключен к выходу шестого элемента И-НЕ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU826419A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 758257, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-02-15—Публикация

1983-08-09—Подача