(54) УСТРОЙСТВО ДЛЯ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

С КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU830386A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Микропрограммное устройство управления | 1980 |

|

SU943728A1 |

| Микропрограммное устройство управления | 1981 |

|

SU999052A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении самоконтролируемых устройств управления вычислительных машин и других систем.

Известно микропрограммное устройство управления, содержащее два запоминающих блока, регистры, логические элементы И и ИЛИ, элементы задержки, дешифраторы и генератор тактовых импульсов 1.

Недостаток этого устройства - низкая достоверность функционирования, обусловленная отсутствием контроля его работоспособности.

Наиболее близким к предлагаемому по технической супдности и достигаемому результату является устройство для микропрограммного управления, содержаш.ее генератор импульсов и дешифратор логических условий, выход которого соединен с информационным входом регистра логических условий, выходом подключенного к управляющим входам элементов И первой группы, установочные входы которых являются входами буферного регистра, выход буферного регистра соединен с первыми входами элементов И второй группы, выходы которых

подключены к первым входам регистра адреса, установочный вход которого является входом кода операции устройства, а выход соединен с информационным входом первого дешифратора, выход которого подключен к

управляющим входампервого запоминающего блока, первым информационным входом соединенного со вторым входом буферного регистра, вторым информационным выходом - с первь м входом дешифратора логических условий и первым счетным входом

счетчика микрокоманд, третьим информационным выходом - со вторым входом дещифратора логических условий и информационным входом счетчика адреса, четвертым информационным входом - со вторым входом регистра адреса, выходы счетчика микрокоманд через первый элемент И соединены с первым входом второго элемента И и через первый элемент И соединены с первым входом второго элемента И и через первый элемент НЕ - с первым входом третьего эле

мента И, выход первого элемента задержки подключен ко второму входу второго элемента И и через второй элемент задержки - к первому входу четвертого элемента И, выходом соединенного со вторыми входами

элементов 4 второй группы, выход второго элемента И подключен к установочным входам регистра логических условий, буферного регистра, первого дешифратора и счетчика адресов, выходом соединенного с первым информационным входом второго дешифратора, выход которого подключен к управляющему входу второго запоминающего блока, информационный вход которого является информационным входом устройстваСУ.

Недостаток устройства состоит в низкой надежности, обусловленной отсутствием контроля правильности выполнения заданной микропрограммы.

Цель изобретения - повышение надежности устройства.

Указанная цель достигается тем, что устройство содержит третий элемент задержки, триггер, элемент ИЛИ, пятый, шестой, седьмой, восьмой и девятый элементы И, второй третий и четвертый элементы НЕ, счетчик идентификаторов и дешифратор идентификаторов, первый и второй информационные входы которого соединены соответственно со вторым и третьим информационными выходами первого запоминающего .блока, а выход - с информационным входом счетчика идентификаторов, обнуляющий вход которого подключен к управляющему выходу второго запоминающего блока и через второй элемент НЕ - к первому входу шестого элемента И, а выходы через седьмой элемент И - ко второму входу шестого, к первому входу восьмого элементов И и ко входу третьего элемента НЕ, выход которого соединен с первым входом девятого элемента И, выход первого элемента И подключен ко вторым входам четвертого и девятого элементов И и через четвертый элемент НЕ - ко второму входу восьмого элемента И, выходы шестого, восьмого и девятого элементов И соединены с соответствуюшими входами элемента ИЛИ, выходом подключенного к входу триггера инверсный выход которого подсоединен к третьему входу второго, третьему входу четвертого и первому входу пятого элементов И, второй вход пятого элемента И подключен к выходу генератора импульсов, а выход - ко входу первого элемента задержки и второму входу третьего элемента И, выходом соединенного со вторым информационным входом второго дешифратора и через третий элемент задержки - со вторым счетным входом счетчика микрокоманд.

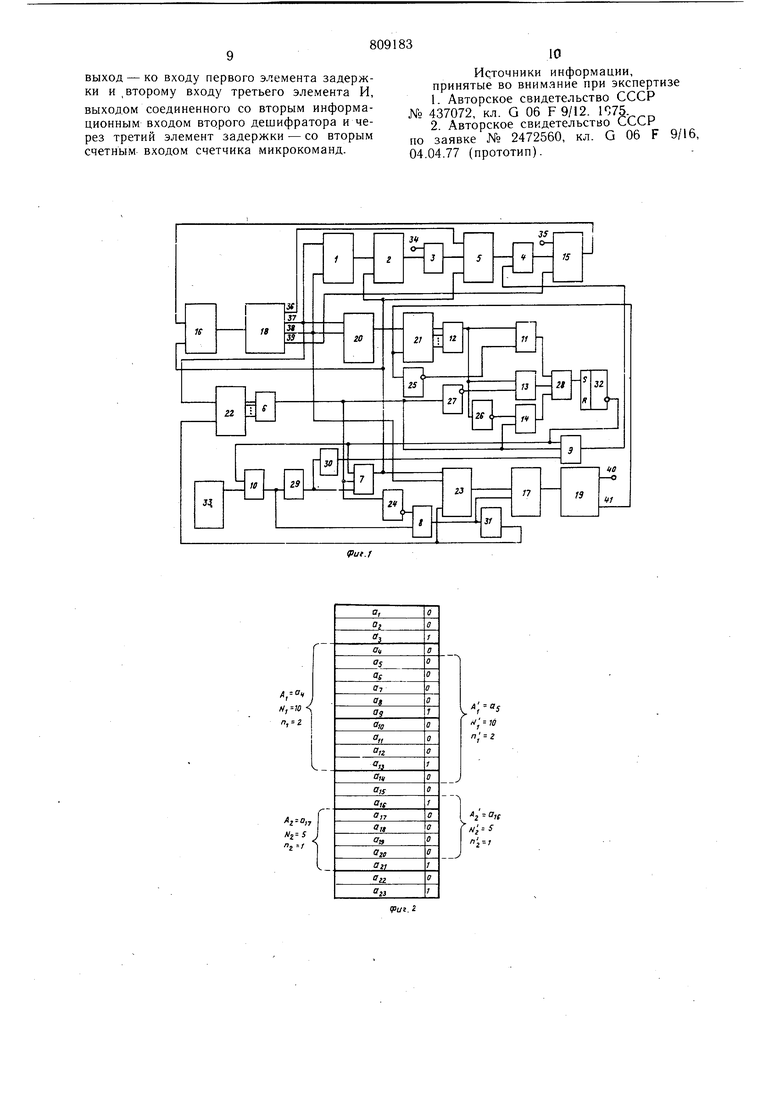

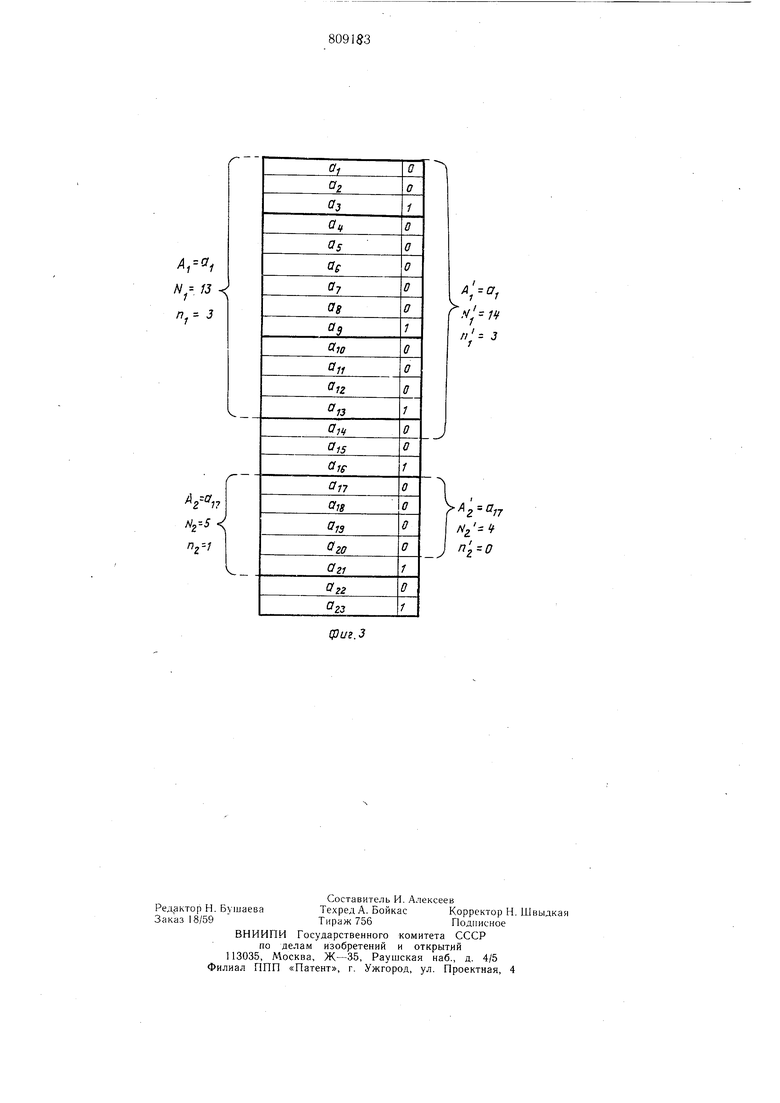

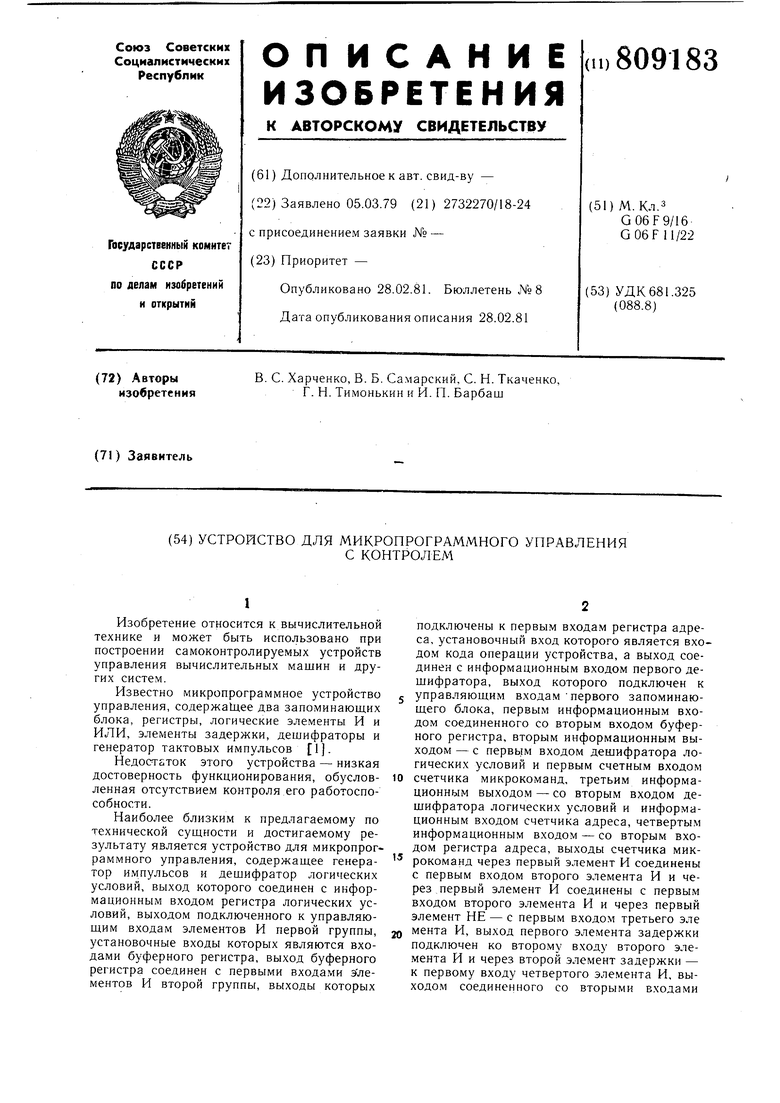

На фиг. 1 изображена схема устройства; на фиг. 2 и 3 - примеры выполнения микропрограмм с искаженным начальнь1м адресом и числом микрокоманд.

Устройство содержит .дешифратор 1 логических условий, регистр 2 логических условий, первую и вторую группы 3 и 4 элементов И, буферный регистр 5, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И 6-14, регистр 15 адреса, первьш и второй дешифраторы 16 и 17, первый и второй запоминающие блоки 18 и 19, дешифратор 20 идентификаторов, счетчик 21 идентификаторов, счетчик 22 микрокоманд, счетчик 23 адреса, первый, второй, третий и четвертый элементы НЕ 24-27, элемент ИЛИ 28, первый, второй и третий элементы 29-31 задержки, триггер 32, генератор 33 импульсов вход 34 логических условий, вход 35 кода операции, первый, второй, третий и четвертый информационные выходы 36-39 первого запоминающего блока, информационный вход 40 и управляющий выход 41 второго запоминающего блока.

На фиг. 2 и 3 обозначен адрес, по которому считывается i-тая микрокоманда а (i 1,23), справа от адреса указывается значение идентификатора (О или 1) для данной микрокоманды, адрес первой микрокоманды А , число микрокоманд Nj, число линейных участков или единичных значений идентификатора в последовательности nj(j 1,2) и параметры, аналогичные искаженной линейной последовательности.

Устройство работает следующим образом В исходном состоянии все элементы памяти находятся в нуле. Код операции поступает на вход 35 регистра 15 и задает адрес S соответствующей ячейки в запоминающем блоке 18.

Первый импульс генератора 30 через от. крытый элемент И 10, элемент 29 задержки и элемент 7 производит установку в нуль регистра 5 и регистра 2, а также через первый дещифратор 16 производится считывание первого информационного слова из запоминающего блока 18. С выхода 36 запоминающего блока 18 косвенный адрес первой микрокоманды очередной последовательносJ ти записывается в регистр 5. С выхода 37 в счетчиках 22 записывается число микрокоманд в первой линейной последовательности микропрограммы. С выхода 38 в счетчик 23 записывается адрес первой микрокоманды этой последовательности, одновремено но сигналы с выхода 37 и 38 поступают на входы дешифратора 1, который формирует признак проверяемых логических условий и записывает его в регистр 2, эти сигналы поступают также на вход дешифратора 20, который формирует код числа идентификаторов в выполняемой последовательности и производит запись кода в счетчик 21. Если последовательность состоит из одного линейного участка, в счетчик 21 записывается единица. В противном случае в счетчик 21 0 заносится число последовательно записанных в запоминающем блоке 19 линейных участков, из которых состоит выполняемая последовательность. Сигнал с выхода 39 запоминающего блока 18 устанавливает в нуль регистр 15. Второй импульс генератора 33 через элемент И 10 и элемент И 8 открывает дешифратор 17, и из запоминающего блока 19 начинается считывание микрокоманд. При считывании каждой микрокоманды из блока 19 содержимое счетчиков 22 и адреса 23 соответственно уменьшается и увеличивается на единицу. При считывании последней микрокоманды первого линейного участка содержимое счетчика 21 уменьшается на единицу и из запоминающего блока 19 продолжается считывание микро команд. При считывании последней микрокоманды последнего линейного участка последовательности единичны.м сигналов идентификатора обнуляется счетчик 21 и на выходе элемента И 12 появляется единичный сигнал. Одновременно с обнулением счетчика 21 происходит обнуление счетчика 22 и на выходе элемента И 16 также появляется единичный сигнал. Если последовательность микрокоманд, считываемых из запоминающего блока, состоит из одного линейного участка, то обнуление счетчиков 21 и 22 происходит при появлении первого единичного значения идентификатора. При правильном функционировании устройства обнуление счетчиков 21 и 22 происходит одновременно. Элементы И 13 и 14 закрыты нулевыми сигналами с выходов элементов НЕ 27 и 26 соответственно, а элемент И 11 -нулевым сигналом с выхода элемента НЕ 25, инвертирующим единичное значекие идентификаторов. Поэтому на выходе элемента ИЛИ 28 сигнал .отсутствует и триггер 32 остается в нулевом состоянии. Очередной импульс через открытый элемент 9 поступает на элементы 4 группы 4, и в регистр 15 из регистра 5 записывается адрес очередного информационного слова. Этот адрес формируется в регистре 5 в зависимости от кода, записанного в регистре 2, и значений логических условий, поступающих на вход 34 группы 3 элементов И. По следующему тактовому импульсу происходит установка в ну.ть через открытый элемент И 7 регистра 2 и регистра 5 и запуск дешифратора 16. Из запоминающего блока 18 считывается информация от очередной линейной последовательности и работа устройства продолжается аналогично описанному. Работа устройства при возникновении в нем отказе. При искажении адреса первой микрокоманды очередной линейной последовательности, котора-я может произойти вследствие отказа в запоминающем блоке 8 на выходе 38, счетчике 23 или дещифраторе 17, микропрограммное устройство управления перейдет к выполнению непредусмотренной линейной последовательности микрокоманд. Поскольку из запоминающего блока 19 будет считываться последовательность-с другим, начальны.м адресом, то число и момент появления, единичных значений идентификаторов на выходе 41 не будет соответствовать числу микрокоманд, записанному в счетчик 22. В этом случае обнуление счетчиков 22 И 21 произойдет неодповремсши). что i;pn ведет к появлению единичного сигна.1п ii;i выходе одного из э.чсмеитов И 13 м.чи -4 и последующему срабутывянию триггера 32 Предположим, из запоминаюпхего б/кжа 1 должна быть считана последовательность микрокоманд с параметрами . Q. Nf 10, П( 2. Пусть в результате отказа адрес первой микрокоманды исказился и А, QS-. Тогда после считывания из запоминающего блока 19 микрокоманды с адресом U13 счетчик 21 обнулится, а в счетчике 22 останется код, равный единице. Это приведет к тому, что на входах элемента И 13 появятся единичные сигналы, поступающие с выхода элемента И 12 и элемента НЕ 27. В результате через элемент ИЛИ 28 поступит сигнал отказа, который установит триггер 32 в единичное оосостояние. Триггер 32 нулевым сигналом со своего нулевого выхода закроет элементы И 9, 10 и 7, и генератор 33 прекратит подачу тактовых импульсов. После этого устройство переходит в режим повторного выполнения микропрограммы или локализации отказа. Устройство работает аналогично и в другом случае, когда адрес первой микрокоманды Ai Qie AI . Тогда после считывания микрокоманды с адресом QIC произойдет обнуление счетчика 21, а в счетчике 22 будет записан код, равный четырем. Работа устройства при искажении информации о числе микрокоманд, которое может произойти вследствие отказа в запоминай щем блоке 18 на выходе 37, счетчике 22, счетчике 23, дещифраторе 17 или запоминающем блике 19 на выходе 41. Отказы указанных узлов приведут к выполнению укороченной или удлиненной микропрограммы, а это в свою очередь-к неодновременному обнулению счетчиков 22 и 23. Предположим, что вместо микропрограммы с параметрами .t 0., N1 13, п 3 вып олняется микропрограмма с парамет рами AI Q.«, N 1.4, п 3. Такое искажение может произойти из-за того, что в результате отказа в запоминающем блоке 18 на выходе 37 в счетчик 22 был записан код NI 14 Nt, в счетчике 22 был пропущен один импульс (не уменьшен код, записанный в счетчике после считывания очередной микрокоманды, в результате отказа счетчика 23 или дешифратора 17 или на выходе 1 запоминающего блока 19 была пропущена одна микрокоманда. Появление любой з указанных причин приведет к тому, что после считывания микрокоманды с адресом f3 произойдет обнуление счетчика 21, а в четчик 22 будет записан код, равный единие. В результате элемент И 13 сформирует игнал отказа, который приведет к срабатыанию триггера 32. При выполнении микропрограммы, в котоой число микрокоманд меньше требуемого (Nz 4 Na), после считывания микрокоманды с адресом произойдет обнуление счетчика 22 до прихода микрокоманды с единичным значением идентификатора и обнуления счетчика 21. При этом с выхода элемента И 6 и элемента НЕ 26 на входы элемента И 14 поступят единичные сигналы, что приведет к срабатыванию триггера 32. В случае возникновения отказов, приводящих к другим искажениям параметров выполняемой микропрограммы, обнуление счетчиков 21 и 22 происходит также неодновременно, что фиксируется схемой контроля. В процессе функционирования микропрограммного устройства управления возможен отказ в работе дешифратора 20 или счетчика 21, что приводит к его преждевременному обнулению или сохранению устойчивого ненулевого состояния. Если в процессе функционирования произошло преждевременное обнуление счетчика 21, то на выходе элемента И 12 появляется единичный сигнал, который поступает на вход элемента И 11, на другой вход которого поступает единичный сигнал с элемента НЕ 25. На выходе элемента И 11 формируется сигнал управления, который поступает на первый вход элемента ИЛИ 28 и далее на единичный вход триггера 32. Элемент И 11 формирует сигнал отказа также в ситуации когда произошло одновременное обнуление счетчиков 21 и 22 при нулевом значении идентификатора. Такая ситуация возникает при кратных отказах в двух и более узлах устройства. Таким образом, в предлагаемом микропрограммном устройстве управления осуществляется контроль правильности функционирования основных узлов и соответствия выполняемых микропрограмм. Кроме того, средства контроля в устройстве являются самопроверяемыми и позволяют блокировать работу устройства и фиксировать соетояние элементов памяти в момент обнаружения отказа. Это позволяет существенно повысить надежность микропрограммного устройства управления. Формула изобретения Устройство для микропрограммного управления с контролем, содержащее генератор импульсов и дешифратор логических условий, выход которого соединен с информационным входом регистра логических условий, выходом подключенного к управляющим входам элементов И первой группы, установочные входы которых являются входами логических условий устройства, а выходы соединены с первыми входами буферного регистра, выход буферного регистра соединен с первыми входами элементов И второй группы, выходы которых подключены к первым входам регистра адреса, установочный вход которого является входом кода one рации устройства, а выход соединен с информационным входом первого дешифратора, выход которого подключен к управляющему входу первого запоминающего блока, первым информационным выходом соединенного со вторым входом буферного регистра, вторым информационным выходом - с первым входом дешифратора логических условий И, первым счетным входом счетчика микрокоманд, третьим информационным выходом - со вторым входом дешифратора логических условий и информационным входом счетчика адреса, четвертым информационным выходом - со вторым входом регистра адреса, выходы счетчика микро1(оманд через первый элемент И соединены с первым входом второго элемента И и через первый элемент НЕ - с первым входом третьего элемента И, выход первого элемента задержки подключен ко второму входу элемента И и через второй элемент задержки - к первому входу четвертого элемента И, выходом соединенного со вторыми входами элементов И второй группы, выход второго элемента И подключен к установочным входам регистра логических условий, буферного регистра, первого дешифратора и счетчика адресов, выходом соединенного с первым информационным входом второго дешифратора, выход которого подключен к управляющему входу второго запоминающего блока, информационный вход которого является информационным входом устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит третий элемент задержки, триггер, элемент ИЛИ, пятый, шестой, седьмой, восьмой и девятый элементы И, второй, третий и четвертый элементы НЕ, счетчик идентификаторов дешифратор идентификааторов, первый и второй информационные входы которого соединены соответственно со вторым и третьим информационными выходами первого запоминающего блока, а выход - с информационным входом счетчика идентификаторов, обнуляющий вход которого подключен к управляющему выходу второго запоминающего блока и через второй элемент НЕ к первому входу шестого элемента И, а выходы через седьмой элемент И - ко второму входу шестого, к первому входу восьмого элементов И и ко входу третьего элемента НЕ, выход которого соединен с первым входом девятого элемента И, выход первого элемента И подключен ко вторым входам четвертого и девятого элементов И и через четвертый элемент НЕ - ко второму входу восьмого элемента И, выходы щестого, восьмого и девятого элементов И соединены с соответствующими входами элемента ИЛИ выходом подключенного к входу триггера, инверсный выход которого подсоединен к третьему входу второго, третьему входу четвертого и первому входу пятого элементов И, второй вход пятого элемента И подключен к выходу генератора импульсов, а

выход - ко входу первого элемента задержки и .второму входу третьего элемента И, выходом соединенного со вторым информационным входом второго дешифратора и через третий элемент задержки - со вторым счетным входом счетчика микрокоманд.

А,-°ч

n,--w 4

, 2

А, а,

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

№ 437072, кл. G Об F 9/12. 1575 2 Авторское свидетельство СССР

по заявке № 2472560, кл. G 06 F 9/16,

13

HZ-S

n,i

,

. f, j

Авторы

Даты

1981-02-28—Публикация

1979-03-05—Подача