Изобретение относится к вычислительной технике и может быть использовано в аппаратуре контроля работы запоминающих устройств.

Цель изобретения - повьппение надежности устройства.

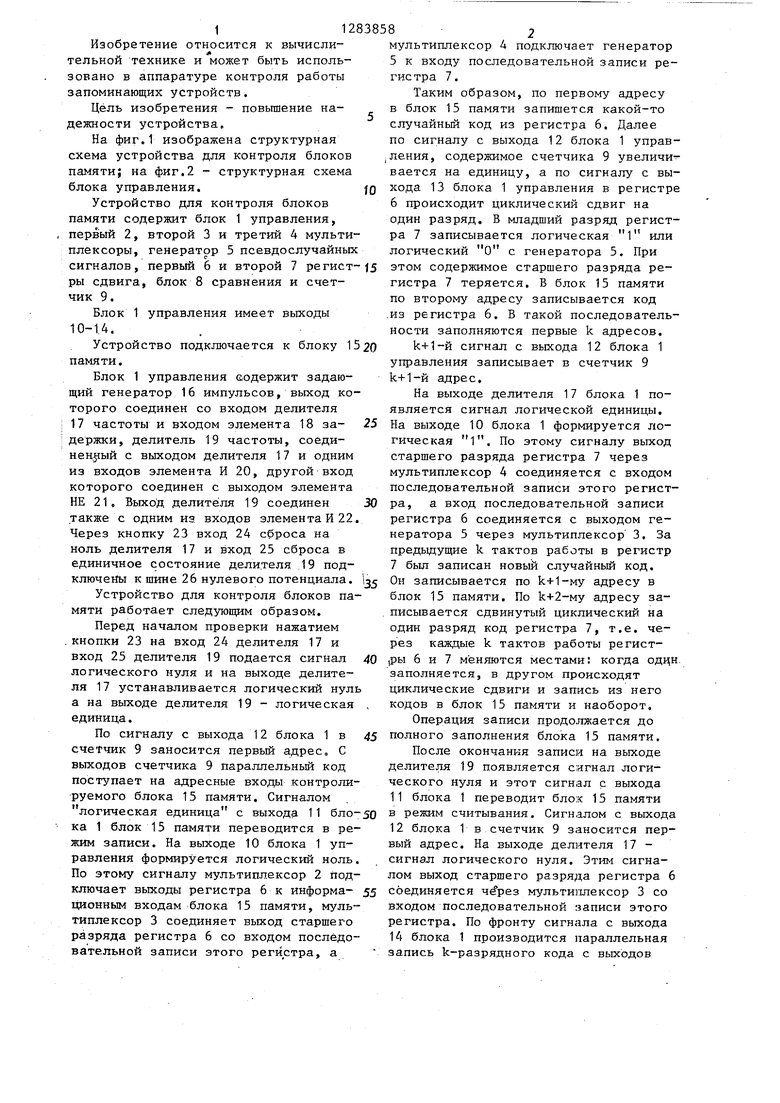

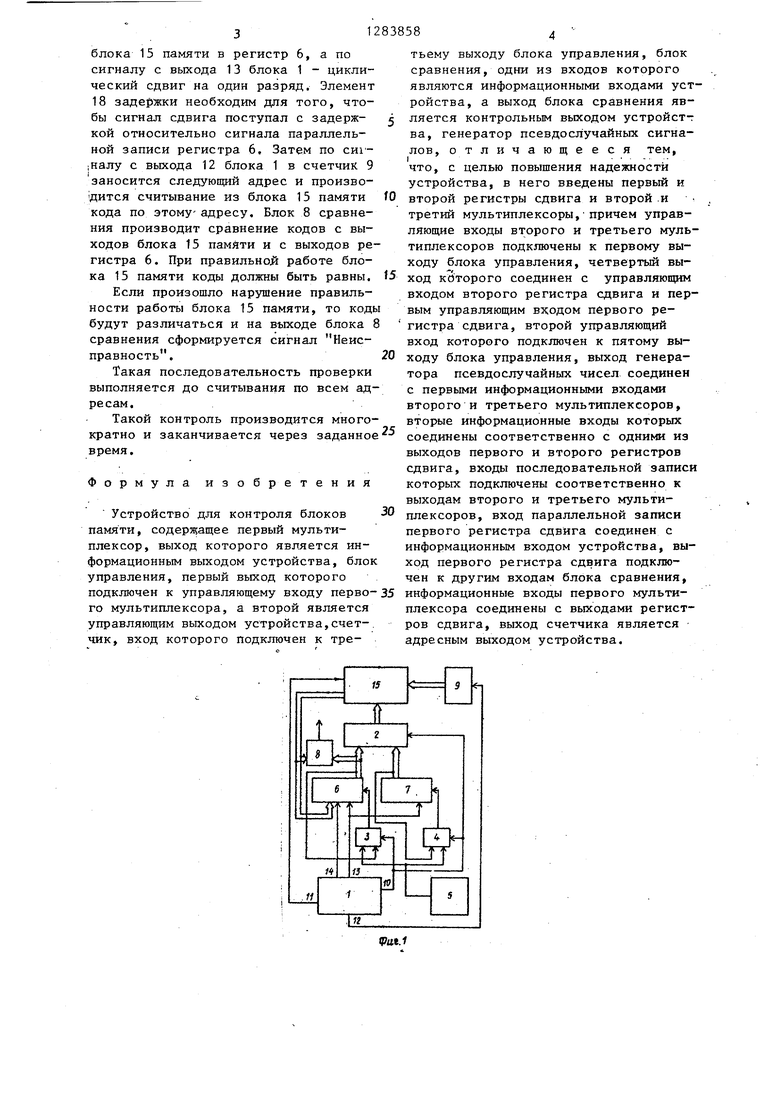

На фиг.1 изображена структурная схема устройства для контроля блоков памяти; на фиг.2 - структурная схема блока управления.

Устройство для контроля блоков памяти содержит блок 1 управления, , первый 2, второй 3 и третий 4 мультиплексоры, генератор 5 псевдослучайньпс

fO

мультиплексор 4 подключает генератор

5к входу последовательной записи регистра 7.

Таким образом, по первому адресу в блок 15 памяти запишется какой-то случайньй код из регистра 6. Далее по сигналу с выхода 12 блока 1 управ- |Ления, содержимое счетчика 9 увеличивается на единицу, а по сигналу с выхода 13 блока 1 управления в регистре

6происходит циклический сдвиг на один разряд, В младший разряд регистра 7 записывается логическая 1 или логический О с генератора 5. При

сигналов, первый 6 и второй 7 регнет-f5 этом содержимое старшего разряда реры сдвига, блок 8 сравнения и счетчик 9.

Блок 1 управления имеет выходы 10-1.4.

Устройство подключается к блоку 1520 памяти.

Блок 1 управления еодержит задающий генератор 16 импульсов, выход которого соединен со входом делителя 17 частоты и входом элемента 18 задержки , делитель 19 частоты, соеди- нен,51ый с выходом делителя 17 и одним из входов элемента И 20, другой вход которого соединен с выходом элемента НЕ 21, Выход делителя 19 соединен также с одним из входов элемента И 22 Через кнопку 23 вход 24 сброса на ноль делителя 17 и вход 25 сброса в единичное состояние делителя 19 подгистра 7 теряется. В блок 15 памяти по второму адресу записывается код из регистра 6, В такой последовательности заполняются первые k адресов,

k+1-й сигнал с выхода 12 блока 1 управления записывает в счетчик 9 k+1-й адрес,

На выходе делителя 17 блока 1 появляется сигнал логической единицы, 25 На выходе 10 блока 1 формируется логическая 1. По этому сигналу выход

30

старшего разряда регистра 7 через мультиплексор 4 соединяется с входом последовательной записи этого регистра, а вход последовательной записи регистра 6 соединяется с выходом генератора 5 через мультиплексор 3. За предьщущие k тактов работы в регистр 7 бьш записан новый случайный код, ключейы к шине 26 нулевого потенциала, Он записывается по k+1-му адресу в Устройство для контроля блоков па- блок 15 памяти. По k+2-му адресу замяти работает следующим образом,

Перед началом проверки нажатием кнопки 23 на вход 24 делителя 17 и вход 25 делителя 19 подается сигнал логического нуля и на выходе делителя 17 устанавливается логический нуль а на выходе делителя 19 - логическая единица,

По сигналу с выхода 12 блока 1 в счетчик 9 заносится первый адрес, С выходов счетчика 9 параллельньй код поступает на адресные входы контролируемого блока 15 памяти. Сигналом

логическая единица с выходэ 11 бло-50 режим считывания. Сигналом с выхода

ка 1 блок 15 памяти переводится в ре-12 блока 1 в счетчик 9 заносится пержим записи. На выходе 10 блока 1 уп-вый адрес. На выходе делителя 17 равления формируется логический ноль.сигнал логического нуля. Этим сигнаПо этому сигналу мультиплексор 2 под-лом выход старшего разряда регистра 6

ключает выходы регистра 6 к информа- 55соединяется мультиплексор 3 со

ционным входам блока 15 памяти, муль-входом последовательной записи этого

типлексор 3 соединяет выход старшегорегистра. По фронту сигнала с выхода

разряда регистра 6 со входом послёдо-14 блока 1 производится параллельная

вательной записи этого регистра, а запись k-разрядного кода с выходов

мультиплексор 4 подключает генератор

5к входу последовательной записи регистра 7.

Таким образом, по первому адресу в блок 15 памяти запишется какой-то случайньй код из регистра 6. Далее по сигналу с выхода 12 блока 1 управ- |Ления, содержимое счетчика 9 увеличивается на единицу, а по сигналу с выхода 13 блока 1 управления в регистре

6происходит циклический сдвиг на один разряд, В младший разряд регистра 7 записывается логическая 1 или логический О с генератора 5. При

гистра 7 теряется. В блок 15 памяти по второму адресу записывается код из регистра 6, В такой последовательности заполняются первые k адресов,

k+1-й сигнал с выхода 12 блока 1 управления записывает в счетчик 9 k+1-й адрес,

На выходе делителя 17 блока 1 появляется сигнал логической единицы, На выходе 10 блока 1 формируется логическая 1. По этому сигналу выход

писывается сдвинутый циклический на один разряд код регистра 7, т.е, через каждые k тактов работы регист- 6 и 7 меняются местами: когда одцн. заполняется, в другом происходят циклические сдвиги и запись из него кодов в блок 15 памяти и наоборот. Операция записи продо.пжается до полного заполнения блока 15 памяти. После окончания записи на выходе делителя 19 появляется сигнал логического нуля и этот сигнал с выхода 11 блока 1 переводит блох 15 памяти

блока 15 памяти в регистр 6, а по сигналу с выхода 13 блока 1 - циклический сдвиг на один разряд. Элемент 18 задержки необходим для того, чтобы сигнал сдвига поступал с задержкой относительно сигнала параллельной записи регистра 6, Затем по си1- 1налу с выхода 12 блока 1 в счетчик 9 заносится следующий адрес и производится считывание из блока 15 памяти кода по этому адресу. Блок 8 сравнения производит сравнение кодов с выходов блока 15 памйти и с выходов регистра 6. При правильной работе блока 15 памяти коды должны быть равны.

Если произошло нарушение правильности работы блока 15 памяти, то коды будут различаться и на выходе блока 8 сравнения сформируется сигнал Неисправность.

Такая последовательность проверки выполняется до считывания по всем адресам.

Такой контроль производится много

кратно время.

и заканчивается через заданное

Формула изобретения

Устройство для контроля блоков памяти, содержащее первый мультиплексор, выход которого является информационным выходом устройства, блок управления, первый выход которого подключен к управляющему входу перво- го мультиплексора, а второй является управляющим выходом устройства,счет-. чик, вход которого подключен к тре

O 5

0

5

тьему выходу блока управления, блок сравнения, одни из входов которого являются информационными входами устройства, а выход блока сравнения яв- 5 ляется контрольным выходом устройств ва, генератор псевдослучайных сигналов, отличающееся тем, что, с целью повышения надежности устройства, в него введены первый и второй регистры сдвига и второй .и третий мультиплексоры, причем управляющие входы второго и третьего мультиплексоров подключены к первому выходу блока управления, четвертый выход которого соединен с управляющим входом второго регистра сдвига и первым управляющим входом первого регистра сдвига, второй управляющий вход которого подключен к пятому выходу блока управления, выход генератора псевдослучайных чисел соединен с первыми информационными входами второго и третьего мультиплексоров, вторые информационные входы которых соединены соответственно с одними из выходов первого и второго регистров сдвига, входы последовательной записи которых подключены соответственно к выходам второго и третьего мультиплексоров, вход параллельной записи первого регистра сдвига соединен с информационным входом устройства, выход первого регистра сдвига подключен к другим входам блока сравнения, информационные входы первого мультиплексора соединены с выходами регистров сдвига, выход счетчика является адресным выходом устройства.

5

0

Ф//

Редактор А,Ревин

Составитель В.Рудаков Техред А.Кравчук

Заказ 7А50/52 Тираж 589,Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

(PtiZ.2

Ко рр е кто р к симишин е ц

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для имитации объекта контроля | 1984 |

|

SU1188743A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1411809A1 |

| Устройство для определения области работоспособности радиоэлектронных схем | 1986 |

|

SU1386947A1 |

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре контроля работы запоминающих устройств. Цель изобретения - повышение надежности устройства. Устройство содержит три мультиплексора, генератор iпсевдослучайных сигналов, два регистра сдвига, блок сравнения, счетчик и блок управления. Контроль блока памяти заключается в последовательной записи по каждому адресу кодов, сформированных с помощью генератора псевдослучайных сигналов, с последующим их считыва- j нием и сравнением. 2 ил. (Л 00 со 00 СП 00

Авторы

Даты

1987-01-15—Публикация

1985-05-13—Подача