Изобретение относится к вычислительной технике, в частности к запоминающим устройствам статического типа с контролем на правильность их работы, и может быть использовано при конструировании запоми- наюндих устройств с коррекцией ошибок, например кодом Хемминга.

Цель изобретения - повышение надежности устройства.

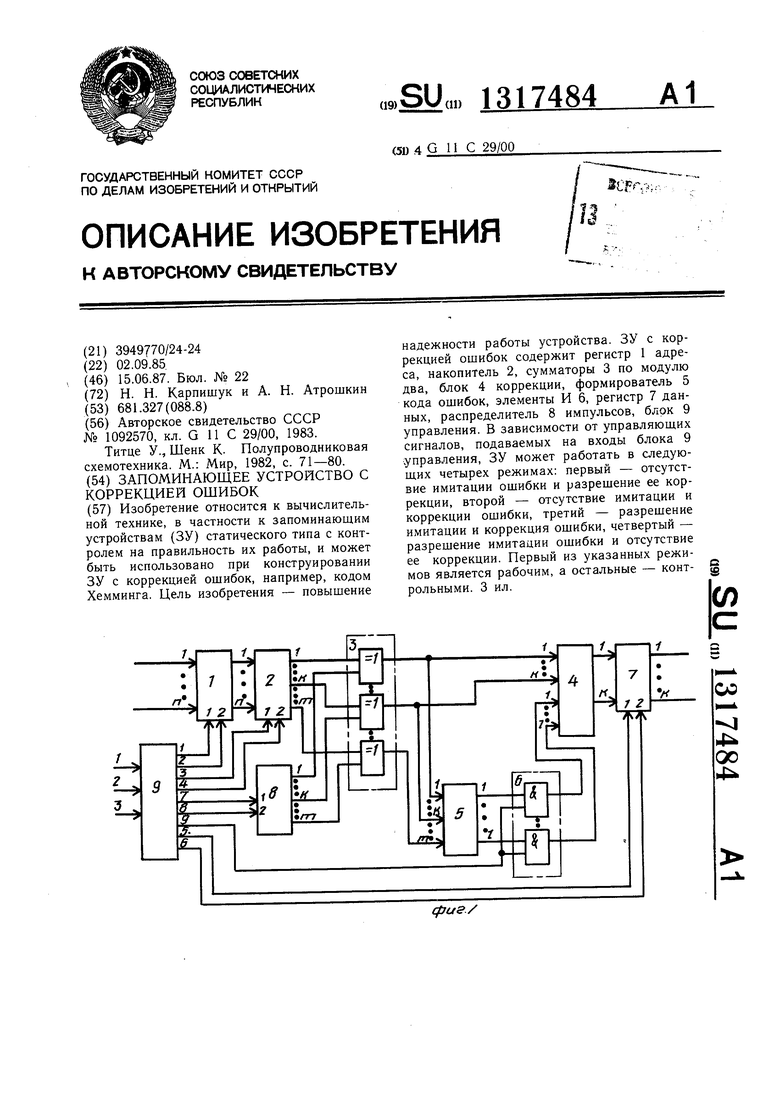

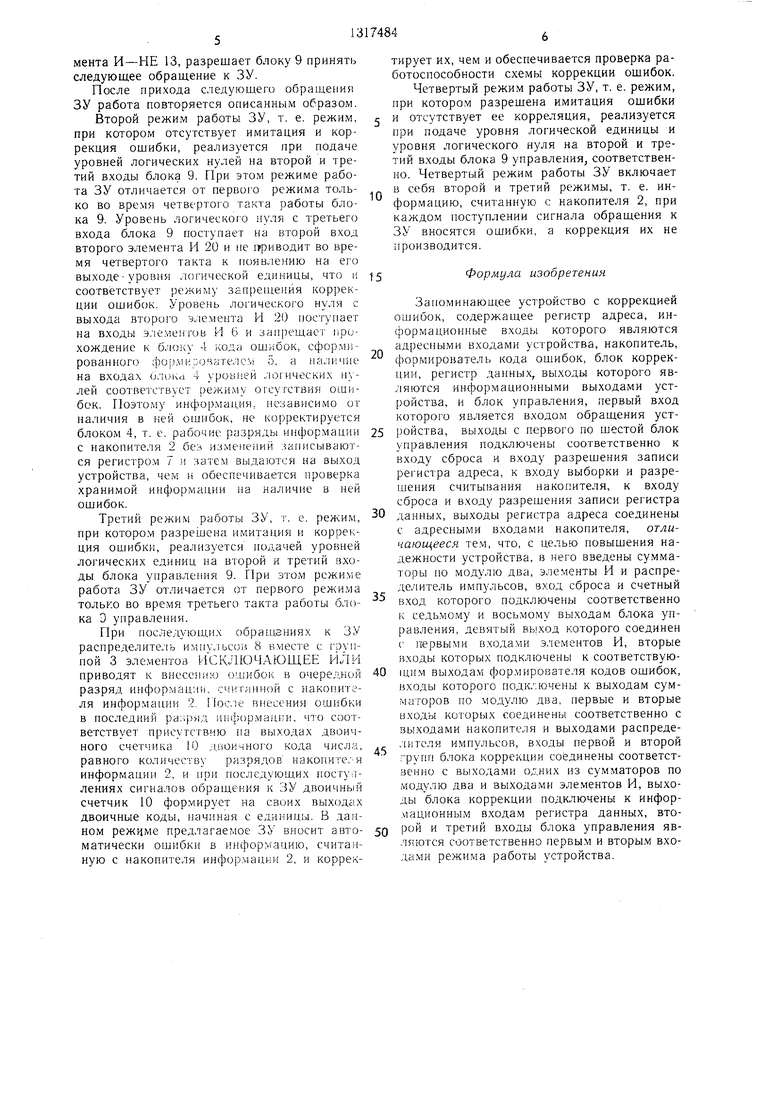

На фиг. 1 показана структурная схема запоминаюодего устройства; на фиг. 2 и 3 - структурные схемы распределителя импульсов и блока управления соответственно.

Запоминающее устройство с коррекцией ошибок содержит (фиг. 1) регистр 1 адреса, накопитель 2, сумматоры 3 по модулю два, блок 4 коррекции, формирователь 5 кода ошибок, элементы И 6, регистр 7 данных распределитель 8 импульсов, блок 9 управления.

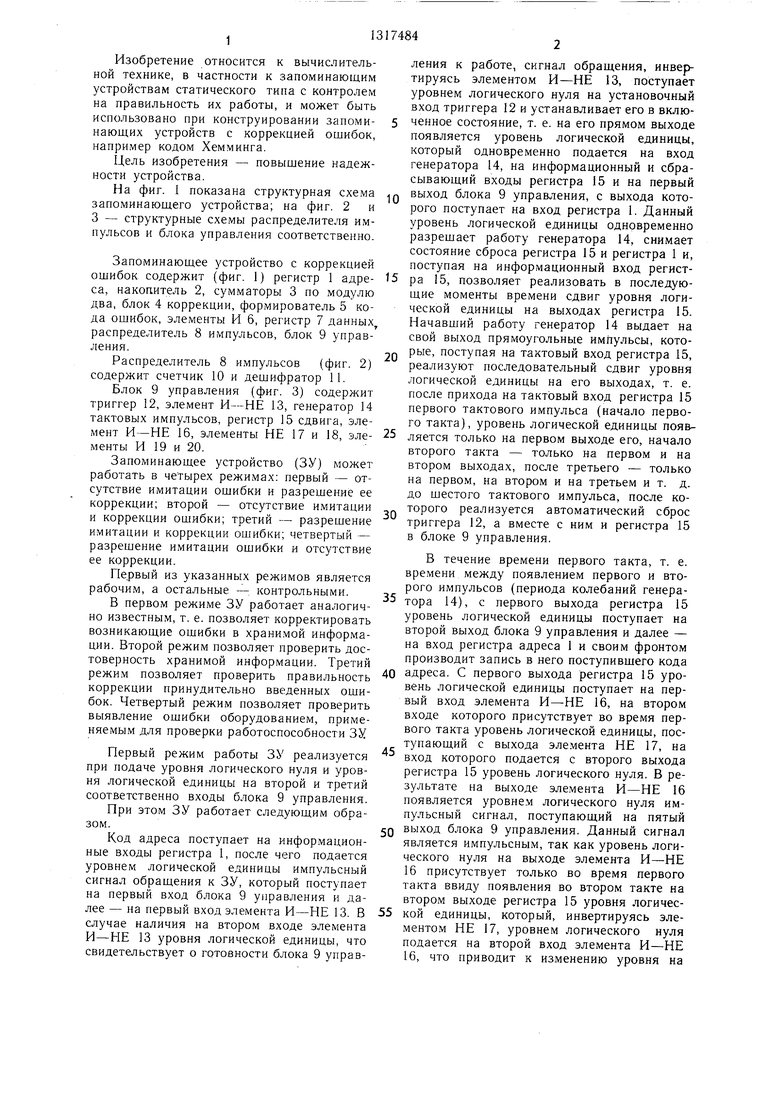

Распределитель 8 импульсов (фиг. 2) содержит счетчик 10 и дешифратор 11.

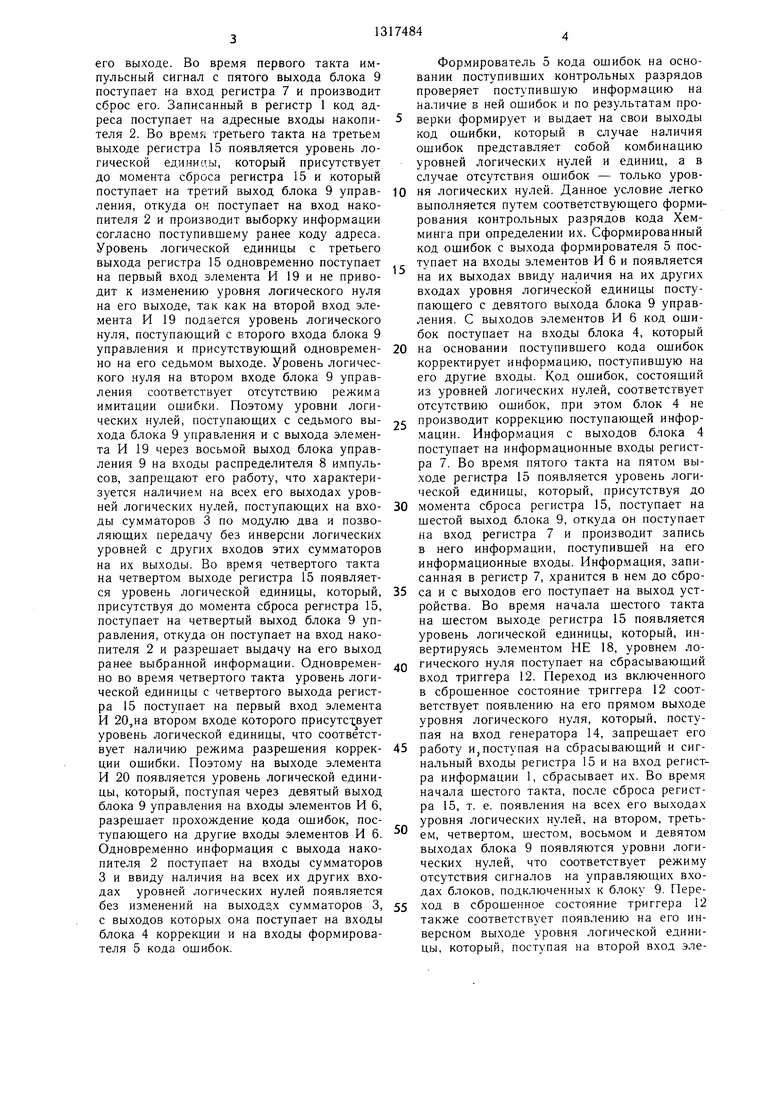

Блок 9 управления (фиг. 3) содержит триггер 12, элемент И-НЕ 13, генератор 14 тактовых импульсов, регистр 15 сдвига, элемент И-НЕ 16, элементы НЕ 17 и 18, элементы И 19 и 20.

Запоминающее устройство (ЗУ) может работать в четырех режимах: первый - отсутствие имитации ошибки и разрешение ее коррекции; второй - отсутствие имитации и коррекции ошибки; третий - разрешение имитации и коррекции ошибки; четвертый - разрешение имитации ощибки и отсутствие ее коррекции.

Первый из указанных режимов является рабочим, а остальные - контрольными.

В первом режиме ЗУ работает аналогично известным, т. е. позволяет корректировать возникающие ошибки в хранимой информации. Второй режим позволяет проверить достоверность хранимой информации. Третий режи.м позволяет проверить правильность коррекции принудительно введенных ошибок. Четвертый режим позволяет проверить выявление ошибки оборудованием, применяемым для проверки работоспособности ЗУ

Первый режим работы ЗУ реализуется при подаче уровня логического нуля и уровня логической единицы на второй и третий соответственно входы блока 9 управления.

При этом ЗУ работает следующим образом.

Код адреса поступает на информационные входы регистра 1, после чего подается уровнем логической единицы импульсный сигнал обращения к ЗУ, который поступает на первый вход блока 9 управления и далее - на первый вход элемента И-НЕ 13. В случае наличия на втором входе элемента И-НЕ 13 уровня логической единицы, что свидетельствует о готовности блока 9 управления к работе, сигнал обращения, инвертируясь элементом И-НЕ 13, поступает уровнем логического нуля на установочный вход триггера 12 и устанавливает его в включенное состояние, т. е. на его прямом выходе появляется уровень логической единицы, который одновременно подается на вход генератора 14, на информационный и сбрасывающий входы регистра 15 и на первый

Q выход блока 9 управления, с выхода которого поступает на вход регистра 1. Данный уровень логической единицы одновременно разрешает работу генератора 14, снимает состояние сброса регистра 15 и регистра 1 и, поступая на информационный вход регист5 ра 15, позволяет реализовать в последующие моменты времени сдвиг уровня логической единицы на выходах регистра 15. Начавший работу генератор 14 выдает на свой выход прямоугольные импульсы, котоQ рые, поступая на тактовый вход регистра 15, реализуют последовательный сдвиг уровня логической единицы на его выходах, т. е. после прихода на тактовый вход регистра 15 первого тактового импульса (начало первого такта), уровень логической единицы появ5 ляется только на первом выходе его, начало второго такта - только на первом и на втором выходах, после третьего - только на первом, на втором и на третьем и т. д. до шестого тактового импульса, после ко торого реализуется автоматический сброс триггера 12, а вместе с ним и регистра 15 в блоке 9 управления.

В течение времени первого такта, т. е. времени между появлением первого и второго импульсов (периода колебаний генера5 тора 14), с первого выхода регистра 15 уровень логической единицы поступает на второй выход блока 9 управления и далее - на вход регистра адреса 1 и своим фронтом производит запись в него поступившего кода

0 адреса. С первого выхода регистра 15 уровень логической единицы поступает на первый вход элемента И-НЕ 16, на втором входе которого присутствует во время первого такта уровень логической единицы, поступающий с выхода элемента НЕ 17, на вход которого подается с второго выхода регистра 15 уровень логического нуля. В результате на выходе элемента И-НЕ 16 появляется уровнем логического нуля импульсный сигнал, поступающий на пятый

0 выход блока 9 управления. Данный сигнал является импульсным, так как уровень логического нуля на выходе элемента И-НЕ 16 присутствует только во время первого такта ввиду появления во втором такте на втором выходе регистра 15 уровня логичес5 кой единицы, который, инвертируясь элементом НЕ 17, уровнем логического нуля подается на второй вход элемента И-НЕ 16, что приводит к изменению уровня на

5

его выходе. Во время первого такта импульсный сигнал с пятого выхода блока 9 поступает на вход регистра 7 и производит сброс его. Записанный в регистр 1 код адреса поступает на адресные входы накопи- теля 2. Во время третьего такта на третьем выходе регистра 15 появляется уровень логической единицы, который присутствует до момента сброса регистра 15 и который поступает на третий выход блока 9 управ- ления, откуда он поступает на вход накопителя 2 и производит выборку информации согласно поступившему ранее коду адреса. Уровень логической единицы с третьего выхода регистра 15 одновременно поступает на первый вход элемента И 19 и не приводит к изменению уровня логического нуля на его выходе, так как на второй вход элемента И 19 подается уровень логического нуля, поступающий с второго входа блока 9 управления и присутствующий одновремен- но на его седьмом выходе. Уровень логического нуля на втором входе блока 9 управления соответствует отсутствию режима имитации ошибки. Поэтому уровни логических нулей, поступающих с седьмого вы- хода блока 9 управления и с выхода элемента И 19 через восьмой выход блока управления 9 на входы распределителя 8 импульсов, запрещают его работу, что характеризуется наличием на всех его выходах уровней логических нулей, поступающих на вхо- ды сумматоров 3 по модулю два и позволяющих передачу без инверсии логических уровней с других входов этих сумматоров на их выходы. Во время четвертого такта на четвертом выходе регистра 15 появляется уровень логической единицы, который, присутствуя до момента сброса регистра 15, поступает на четвертый выход блока 9 управления, откуда он поступает на вход накопителя 2 и разрешает выдачу на его выход ранее выбранной информации. Одновремен- но во время четвертого такта уровень логической единицы с четвертого выхода регистра 15 поступает на первый вход элемента И 20,на втором входе которого присутствует уровень логической единицы, что соответствует наличию режима разрещения коррек- ции ощибки. Поэтому на выходе элемента И 20 появляется уровень логической единицы, который, поступая через девятый выход блока 9 управления на входы элементов И 6, разрещает прохождение кода ошибок, поступающего на другие входы элементов И 6. Одновременно информация с выхода накопителя 2 поступает на входы сумматоров 3 и ввиду наличия на всех их других входах уровней логических нулей появляется без изменений на выход2;Х сумматоров 3, с выходов которых она поступает на входы блока 4 коррекции и на входы формирователя 5 кода ошибок.

Формирователь 5 кода ошибок на основании поступивших контрольных разрядов проверяет поступившую информацию на наличие в ней ошибок и по результатам проверки формирует и выдает на свои выходы код ошибки, который в случае наличия ошибок представляет собой комбинацию уровней логических нулей и единиц, а в случае отсутствия ошибок - только уровня логических нулей. Данное условие легко выполняется путем соответствующего формирования контрольных разрядов кода Хем- минга при определении их. Сформированный код ощибок с выхода формирователя 5 поступает на входы элементов И 6 и появляется на их выходах ввиду наличия на их других входах уровня логической единицы поступающего с девятого выхода блока 9 управления. С выходов элементов И 6 код ошибок поступает на входы блока 4, который на основании поступившего кода ошибок корректирует информацию, поступившую на его другие входы. Код ошибок, состояший из уровней логических нулей, соответствует отсутствию ошибок, при этом блок 4 не производит коррекцию поступающей информации. Информация с выходов блока 4 поступает на информационные входы регистра 7. Во время пятого такта на пятом выходе регистра 15 появляется уровень логической единицы, который, присутствуя до момента сброса регистра 15, поступает на шестой выход блока 9, откуда он поступает на вход регистра 7 и производит запись в него информации, поступившей на его информационные входы. Информация, записанная в регистр 7, хранится в нем до сброса и с выходов его поступает на выход устройства. Во время начала щестого такта на щестом выходе регистра 15 появляется уровень логической единицы, который, инвертируясь элементом НЕ 18, уровнем логического нуля поступает на сбрасывающий вход триггера 12. Переход из включенного в сброшенное состояние триггера 12 соответствует появлению на его прямом выходе уровня логического нуля, который, поступая на вход генератора 14, запрешает его работу и поступая на сбрасывающий и сигнальный входы регистра 15 и на вход регистра информации 1, сбрасывает их. Во время начала шестого такта, после сброса регистра 15, т. е. появления на всех его выходах уровня логических нулей, на втором, третьем, четвертом, шестом, восьмом и девятом выходах блока 9 появляются уровни логических нулей, что соответствует режиму отсутствия сигналов на управляющих в.хо- дах блоков, подключенных к блоку 9. Переход в сброшенное состояние триггера 12 также соответствует появлению на его инверсном выходе уровня логической единицы, который, поступая на второй вход элемента И-НЕ 13, разрешает блоку 9 принять следующее обращение к ЗУ.

После прихода следующего обращения ЗУ работа повторяется описанным образом.

Второй режи1М работы ЗУ, т. е. режим, при котором отсутствует имитация и коррекция ощибки, реализуется при подаче уровней логических нулей на второй и третий входы блока 9. При этом режиме работа ЗУ отличается от первого режима только во время четвертого такта работы блока 9. Уровень логического нуля с третьего входа блока 9 поступает на второй вход второго элемента И 20 и не « риводит во время четвертого такта к появлению на его выходеуровня логической единицы, что и соответствует режиму запрещения коррекции ощибок. Уровень ло1-ического нуля с выхода второго элемента И 20 поступает на входы элементов И 6 и запрещает г.ро- хождение к блслчу 4 кода ощибок, сформированного фо)Л иоонателсл1 5, а на;п- чие на входах 6, Rjivd 4 уров1:ен ;101 ических нулей соответствует режиму отсутствия ошибок. Поэтому информация, независимо от наличия в ней ощибок, не корректируется блоком 4, т. е. рабочие разряды информации с накопителя 2 без изменений записываются регистром 7 и затем выдаются на выход устройства, чем и обеспечивается проверка хранимой информации па наличие в ней ощибок.

Третий режим работы ЗУ, г. е. режим, при котором разрешена имитация и коррекция ошибки, реализуется нодачей уровней логических единиц на второй и третий входы блока управления 9. Г1ри этом режи.ме работа ЗУ отличается от первого режима только во время третьего такта работы блока Э управления.

При последующих обращениях к ЗУ распределитель им |у;|ьсо . 8 вместе с гоуп- пой 3 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ приводят к внесению ошибок в очередной разряд ипфор.мацмн. считанной с накопителя информации 2. iloc.ie внесения ошибки в носледний разряд lUiipopMauin-, что соответствует присутств цо па выходах двоичного счетчика 10 ;июичного кода числа, равного количеству разрядов накопите; я информации 2, и при последующ,их iiocryri- лениях сигналов обращения к ЗУ двоичный счетчик 10 фор.мирует на своих выхода,х двоичные коды, начиная с единицы. В данном режиме предлагаемое ЗУ вносит автоматически ощибки в информацию, считанную с накопителя информации 2, и коррек0

0

5

0

5

0

5

0

тирует их, чем и обеспечивается проверка работоспособности схемы коррекции ошибок. Четвертый режим работы ЗУ, т. е. режим, при котором разрешена имитация ошибки и отсутствует ее корреляция, реализуется при подаче уровня логической единицы и уровня логического нуля на второй и третий входы блока 9 управления соответственно. Четвертый режим работы ЗУ включает в себя второй и третий режимы, т. е. информацию, считанную с накопителя 2, при каждом поступлении сигнала обращения к ЗУ вносятся ощибки, а коррекция их не производится.

Формула изобретения

Заноминающее устройство с коррекцией ошибок, содержащее регистр адреса, информационные входы которого являются адреср)ыми входами устройства, накопитель, формирователь кода ошибок, блок коррек- пии, регистр данных, выходы которого являются информационными выходами устройства, и блок управления, первый вход которого является входом обращения устройства, выходы с первого по шестой блок управления подключены соответственно к входу сброса и входу разрешения записи регистра адреса, к входу выборки и разрешения считьпаания накопителя, к входу сброса и входу разрещения записи регистра данных, выходы регистра адреса соединены с адресными входами накопителя, отличающееся тем, что, с целью повыщения надежности устройства, в него введены су.мма- торы но моду,шо два, элементы И и распределитель импульсов, вход сброса и счетный вход которого подключены соответственно к седь.мому и вось.мому выходам блока управления, девятый выход которого соединен г первыми входами элементов И, вторые входы которых подключены к соответствую- 1ЦИМ выходам формирователя кодов ощибок, входы которого подк. :ючены к выходам сумматоров по модулю два, первые и вторые входы которых соединены соответственно с выходами накопителя и выходами распреде- ,тителя импульсов, входы первой и второй гругщ блока коррекции соединены соответственно с выходами одних из сумматоров по модулю два и выходами эле.ментов И, выходы блока коррекции подключены к информационным входам регистра данных, второй и третий входы блока управления являются соответственно первым и вторы.м входами режима работы устройства.

фиа2

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1495855A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1354248A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ) статического типа с контролем на правильность их работы, и может быть использовано при конструировании ЗУ с коррекцией ошибок, например, кодом Хемминга. Цель изобретения - повышение 2 3 надежности работы устройства. ЗУ с коррекцией ошибок содержит регистр 1 адреса, накопитель 2, сумматоры 3 по модулю два, блок 4 коррекции, формирователь 5 кода ошибок, элементы И 6, регистр 7 данных, распределитель 8 импульсов, блок 9 управления. В зависимости от управляющих сигналов, подаваемых на входы блока 9 управления, ЗУ может работать в следующих четырех режимах: первый - отсутствие имитации ошибки и разрешение ее коррекции, второй - отсутствие имитации и коррекции ошибки, третий - разрешение имитации и коррекция ошибки, четвертый - разрешение имитации ошибки и отсутствие ее коррекции. Первый из указанных режимов является рабочим, а остальные - контрольными. 3 ил. i (Л 00 NU 00 4;;: cpus/

1

2

17

16

L

12

74

3 4

5

С R

18

6

19

7

-в

20

фиг.З

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника | |||

| М.: Мир, 1982, с | |||

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

Авторы

Даты

1987-06-15—Публикация

1985-09-02—Подача