(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Устройство микропрограммного управления | 1980 |

|

SU960814A1 |

| Микропрограммное устройство управления | 1981 |

|

SU985790A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896621A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Устройство микропрограммного управления | 1980 |

|

SU896622A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства управления микропрограммной ЭВМ.

Известно микропрограммное устройство управления, содержащее два запоминающих блока, регистр логических условий, счетчики, дещифраторы, регистры, логические элементы И, НЕ, элементы задержки и генератор тактовых импульсов 1.

Недостатком этого устройства является низкая экономичность, которая обусловлена больщим объемом памяти запоминающих блоков, вызванным хранением больщого числа повторяющихся операционных микрокоманд.

Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является устройство, содержащее регистр логических условий, группы элементов И, буферный регистр, адресный регистр, первый дещифратор и первый запоминающий блок, щифрато, генератор тактовых импульсов, счетчик микрокоманд 2.

Недостатком данного устройства является низкая экономичность, которая обусловлена больщим объемом запоминающих блоков.

Цель изобретения - повыщение экономичности устройства.

Эта цель достигается тем, что микропрограммное устройство управления, содержащее регистр логических условий, выход которого соединен с первым входом первого блока элементов И, второй вход которого является входом логических усовий устройства, выход первого блока элементов И соединен с первым информационным входом буферного регистра, второй информационный вход и выход которого соединены соответственно с выходом номера следующей последовательности первого блока памяти и с первым входом второго блока элементов И, второй вход и выход которого соединены соответственно с выходом первого элемента И и с информационным входом регистра адреса, входы сброса и кода операции которого соединены соответственно с выходом сброса первого блока памяти и входом кода операции устройства, выход регистра адреса соединен с информационным входом- первого дещифратора, вход запуска которого соединен с ВЫХОДОМ второго элемента И и с входами установки в нуль счетчика адреса, регистфа логических условий и буферного регистра, выход первого дешифратора соединен с входом первого блока памяти, выходы номера текущей последовательности и логических условий которого соединены соответственно с входом шифратора и информационным входом регистра логических условий, первый и второй выходы шифратора соединены соответственно с информационными входами счетчиков микрокоманд и адреса, группа выходов счетчика микрокоманд соединена с группой входов третьего элемента И, выход которого соединен с первыми входами первого и второго элементов И и через первый элемент НЕ с первым входом четвертого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов и через первый и второй элементы задержки соединен со вторым входом первого элемента И, счетный вход счетчика микрокоманд через второй элемент НЕ соединен со счетным входом счетчика адреса и с первым выходом второго блока памяти, второй выход и вход которого соединены соответственно с выходами устройства и второго дешифратора, первый вход которого соединен с выходом первого элемента задержки и вторым входом второго элемента И, содержит третий дешифратор, третий блок памяти, регистр адреса операционных микрокоманд, два триггера, сумматор по модулю два, пятый и шестой элементы И, третий элемент задержки, причем первый вход третьего дешифратора соединен с выходом счетчика адреса, а выход третьего дешифратора - со входом третьего блока памяти, выход которого соединен с первым информационным входом регистра адреса операционных микрокоманд, второй информационный вход которого соединен со вторым входом третьего дешифратора и выходом четвертого элемента И, первый разрядный выход регистра адреса операционных микрокоманд соединен со вторым входом второго дешифратора, первый вход которого соединен с нулевым входом первого триггера, второй разрядный выход регистра адреса операционных микрокоманд соединен с первым входом сумматора по модулю два, второй вход которого соединен с единичным выходом первого триггера, единичный вход которого соединен с выходом пятого элемента И, первый вход которого соединен с первым выходом второго блока памяти, а второй вход - с выходом второго элемента задержки и через третий элемент задержки с первым входом шестого элемента И, второй вход которого соединен с выходом сумматора по модулю два, а выход шестого элемента И соединен с единичным входом второго триггера, единичный выход которого соединен с управляющим входом генератора тактовых импульсов.

Сущность изобретения состоит в повышении экономичности устройства путем однократной записи операционных микрокоманд во втором блоке памяти и организации контроля правильности их считывания.

В третьем блоке памяти записаны адреса микрокоманд, выполняемых в различных линейных последовательностях. Количество этих адресов равно количеству микрокоманд в микропрограмме. Адрес очередной выполняемой микрокоманды хранится в регистре адреса операционных микрокоманд, куда он считывается из третьего блока памяти. Во втором блоке памяти хранятся операционные микрокоманды, которые ,отличаются друг от друга. Порядок считывания операционных микрокоманд в соответствии с кодом последовательности считываемых из первого блока памяти, определяется последовательностью адресов, считываемых из третьего блока памяти. В операционных микрокомнадах, которые являются последними в линейных последовательностях, а также в соответствующих им адресах в дополнительном разряде ( поле идентификатора) записывается единица, в остальных - нуль. Сущность принципа контроля состоит в сравнении признаков операционнх микрокоманд и их адресов. Введение первого триггера и соединение его единичного входа с выходом пятого элемента И позволяет запомнить признак считанной из второго блока памяти очередной микрокоманды и выполняемой линейной последовательности и позволяет блокировать работу устройства. Введение сумматора по модулю два необходимо для анализа сигналов со вторых выходов регистра адреса операционных микрокоманд и второго блока памяти и формирования сигнала отказа.

Сигнал отказа формируется, если из второго блока памяти считывается операционная микрокоманда, которая является последней в линейной последовательности до считывания соответствующего адреса из третьего блока памяти, или если после считывания из третьего блока памяти адреса последней микрокоманды в последовательности соответствующая операционная микрокоманда не будет считана из второго блока памяти.

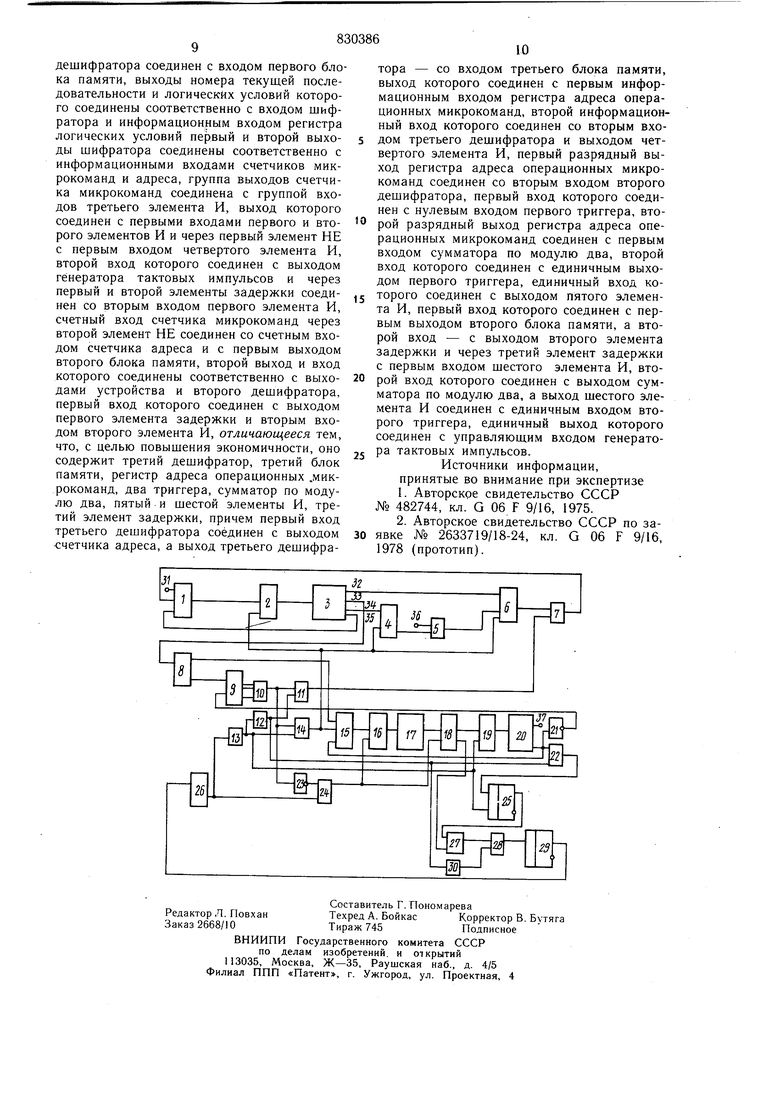

На чертеже представлена функциональная схема микропрограммного устройства управления.

Устройство содержит регистр 1 адреса, первый дещифратор 2, первый блок 3 памяти, регистр 4 логических условий, первый блок 5 элементов И, буферный регистр 6, второй блок 7 элементов И, шифратор 8, счетчик 9 микрокоманд, третий элемент И 5 10, первый элемент И 11, второй элемент 12 задержки, первый элемент 13 задержки, второй элемент И 14, счетчик 15 адреса, третий дешифратор 16, третий блок 17 памяти.

регистр 18 адреса операционных микрокоманд, второй дешифратор 19, второй блок 20 памяти, второй элемент НЕ 21, пятый элемент И 22, первый элемент НЕ 23, четвертый элемент И 24, первый триггер 25, генератор 26 тактовых импульсов, сумматор 27 по модулю два, шестой элемент И 28, второй триггер 29, третий элемент 30 задержки, вход 31 кода операции устройства, первый-четвертьш выходы 32-35 первого блока памяти соответственно вход 36 логических условий устройства, второй выход 37 второго блока памяти.

В первом блоке 3 памяти записывается адресная часть микрокоманды, которая считываетЬя в следующем виде: с выхода 32 - номер следующей последовательности, с выхода 33 - номер текущей посредовательности, с выхода 34 - код проверяемых логических условий, с выхода 35 - сигнал сброса регистра 1.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии. Код (номер) операции поступает через вход 31 в регистр 1 и задает адрес соответствующей ячейки в первом блоке 3 памяти. Генератор 2 тактовых импульсов через первый элемент 13 задержки при наличии разрешающего сигнала с выхода элемента И 10, соответствующего нулевому состоянию счетчика 9 микрокоманд, осуществляет установку в нуль счетчика 15 адреса, регистра 4 логических условий и буферного регистра 6, а также запуск первого дешифратора 2. По сигналу с дешифратора 2 из соответствующей ячейки памяти блока 3 памяти сосчитываются: код номера последующей выполняемой линейной последовательности, который с выхода 32 поступает на первый вход буферного регистра 6, код номера текущей выполняемой последовательности, который поступает с выхода 33 на вход щифратора 8, код проверяемых логических условий, который поступает н.а вход регистра 4 логических- условий с выхода 34, сигнал с выхода 35 производит установку в нуль регистра 1. Сигнал с выхода генератора 26 тактовых импульсов через второй элемент 12 задержки- и через первый элемент И 11 при наличии на его первом входе разрещающего сигнала, соответствующего нулевому состоянию счетчика 9 микрокоманд, поступает на вход второго блока 7 элементов И и производит запись кода номера последующей линейной последовательности с выхода буферного регистра 6 в регистр 1. После считывания адресной части микрокоманды и записи в счетчик 9 микрокоманд кода числа микрокоманд показания счетчика отличны от нуля. Сигнал на выходе элемента И 10 принимает нулевое значение и через первый элемент НЕ 23 открывает элемент И 24.

Вторым тактовым импульсов с выхода генератора 26 тактовых импульсов происходит запуск третьего дешифратора 16 и подтверждение нулевого состояния регистра 18 адреса операционных микрокоманд. После считывания адреса операционной ,микрокоманды из третьего блока 17 памяти он поступает на регистр 18 адреса операционных микрокоманд и на его втором входе появляется единичный сигнал, который поступает на первый вход сумматора 27 по модулю два, на второй вход которого поступает нулевой сигнал с единичного выхода первого триггера 25. Сигнал с выхода первого элемента 13 задержки запускает второй дешифратор 19 и подтвержтает нулевое состояние первого триггера 25. Из второго блока 20 памяти начинается считывание операционной микрокоманды, после чего на первом его выходе появляется единичный сигнал, который поступает на первый вход пятого элемента И 22 и на второй вх счетчика 15 адреса, производя смену адреса очередной микрокоманды. Сигнал с выхода второго элемента 12 задержки поступает на вход элемента И 22, и на выходе этого элемента появляется единичный сигнал, который производит установку в единичное состояние первого триггера 25, в результате чего на второй вход сумматора 27 по модулю два поступает единичный сигнал. Этим же сигналом (с выхода второго элемента 12 задержки) осуществляется опрос шестого элемента И 28 через третий элемент 30 задержки. В результате считывания операционной микрокоманды из второго блока 20 памяти на выходе сумматора 27 по модулю два появляется нулевой сигнал, и сигнал отказа в этом случае не формируется.

Следующим тактовым импульсов с выхода генератора 26 тактовь х. импульсов происходит запуск третьего дешифратора 16 и обнуление регистра 18 адреса операционных микрокоманд, в результате чего на его втором выходе появляется нулевой сигнал. Этот же тактовый импульс через первый элемент 13 задержки осуществляет запуск второго дешифратора 19 и установку в нуль первого триггера 25.

После этого работа схемы происходит аналогично описанному выше. Если считывается из третьего блока 17 памяти адрес микрокоманды, являющейся последней в выполняемой последовательности, то на втором выходе регистра 18 адреса операционных микрокоманд появляется нулевой сигнал. Этот сигнал поступает на первый вход сумматора 27 по модулю два, на второй вход которого поступает нулевой сигнал с единичного выхода первого триггера 25.

После считывания операционных микрокоманд из второго блока 20 памяти на его втором выходе появляется нулевой сигнал, который поступает на первый вход пятого элемента И 22 к через второй элемент НЕ 21 производит уменьшение на единицу содержимого счетчика 9 микрокоманд. Сигнал с выхода генератора 26 тактовых импульсов через первый элемент 13 задержки и второй элемент 12 задержки поступает на вход пятого элемента И 22 и на вход третьего элемента 30 задержки. При этом установки первого триггера 25 в единичное состояние не происходит и на второй вход сумматора 27 по модулю два поступает нулевой сигнал. В результате чего разрешается дальнейшая работа устройства. После считывания из второго блока 20 памяти последнего участка линейной последовательности счетчика 9 микрокоманд обнуляется и на выходе элемента И 10 появляется единичный сигнал. По тактовому импульсу, проходяшему через элементы 13 и 12 задержки, элемент И 11 адрес следующей адресной команды передается из буферного регистра 6 в регистр 1 адреса через блок 7 элементов И. Следующий импульс с генератора тактовых импульсов 26 через элемент 13 задержки и элемент И 14 обнуляет счетчик 15 адреса, регистры 4 и 6. Кроме того, по этому импульсу в зависимости от содержимого регистра 1 адреса дешифратор 2 осуществляет считывание очередной адресной микрокоманды блока 3 памяти и работа устройства продолжается аналогично описанному выше. В процессе функционирования предлагаемого микропрограммного устройства управления отказы в его работе проявляются в считывании лишней операционной микрокоманды из второго блока 20 памяти, в том, что из второго блока 20 памяти считываются не все операционные микрокоманды. Устройство позволяет фиксировать эти отказы слелующим образом. Предположим, что в регистре 18 адреса операционных микрокоманд записан адрес последней в выполняемой последовательности микрокоманды. В эт,ом случае на втором его выходе появляется нулевой сигнал, который поступает на первый вход сумматора 27 по модулю два. Если после считывания операционной микрокоманды из второго блока 20 памяти оказалось, что считанная операционная микрокоманда не является последней, то на втором выходе второго блока 20 памяти появляется единичный сигнал, который поступает на первый вход пяТОГО элемента И 22. Сигнал с выхода генератора 26 тактовых импульсов через первый и второй элементы задержки 13 и 12 соответственно поступает на второй вход пятого элемента И 22 и на вход третьего элемента 30 задержки. В этом случае происходит установка в единичное состояние первого триггера 25 и на второй вход сумматора 27 по модулю два 27 поступает единичный сигнал. Единичный сигнал с его выхода поступает на второй вход шестого элемента И 28, на первый вход которого поступает сигнал с выхода третьего элемента 30 задержки. В результате формируется сигнал отказа, второй триггер 29 устанавливается в единичное состояние и блокирует работу генератора 16 тактовых импульсов. Если в регистре 18 адреса операционных микрокоманд записан адрес очередной не последней в последовательности, операционной микрокоманды, то на втором его выходе появляется единичный сигнал, который поступает на первый вход сумматора 27 по модулю два. Если после этого из второго блока 20 памяти считывается операционная микрокоманда, которая является последней в выполняемой последовательности, то по тактовому импульсу с выхода генератора 16 тактовых импульсов через первый и второй элементы задержки 13 и 12 соответственно установка в единицу первого триггера 25 не происходит, и на второй вход сумматора 27 по модулю два поступает нулевой сигнал. В результате на оба входа шестого элемента И 28 поступают единичные сигналы с выхода сумматора 27 по модулю два и с выхода третьего элемента 30 задержки и сформируется сигнал отказа, по которому триггер 29 блокирует работу устройства. Таким образом, предлагаемое устройство позволяет существенно повысить экономичность устройства и организовать контроль его функционирования. Это давет возможность строить микропрограммные устройства управления с повышенной функциональной надежностью. Формула изобретения Микропрограммное устройство управления, содержащее регистр логических условий, выход которого соединен с первым входом первого блока элементов И, второй вход которого является входом логических условий устройства, выход первого блока элементов И соединен с первым информационным входом буферного регистра, второй информационный вход и выход которого соединены соответственно с выходом- номера следующей последовательности первого блока памяти и с первым входом второго блока эле.ментов И, второй вход и выход которого соединены соответственно с выходом первого элемента И и с информационным входом регистра адреса, входы сброса и кода операции которого соединены соответственно с выходом сброса первого блока памяти и входом кода операции устройства, выход регистра адреса соединен с инфор.мационным входом первого дешифратора, вход запуска которого соединен с выходом второго элемента И и с входами установки в нуль счетчика адреса, регистра логических условий и буферного регистра, выход первого

Авторы

Даты

1981-05-15—Публикация

1979-07-30—Подача