К5

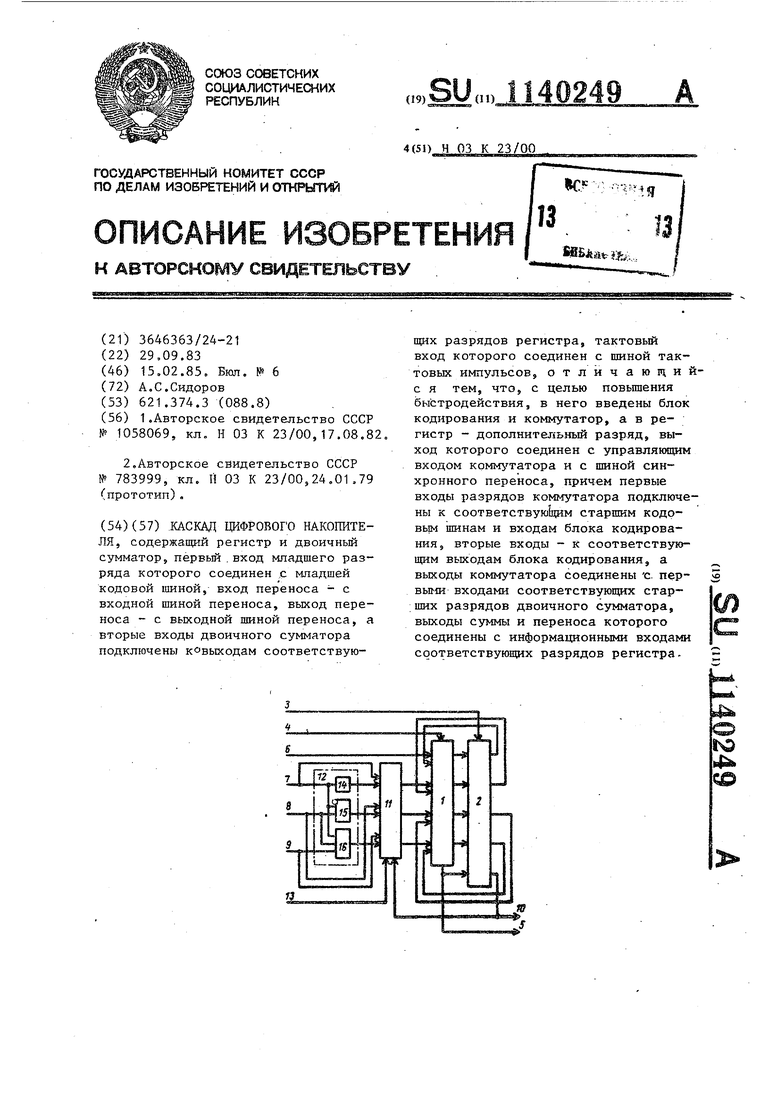

ISii. Изобретение относится к импульсной технике и может быть использовано в цифровых синтезаторах частоты. Известен цифровой накопитель, содержащий параллельный регистр, мультиплексор и два сумматора, первый вход первого из которых соединен с входной шиной, тактовый вход параллельного регистра соединен с пшной тактовых импульсов, а его выход - с вторым входом первого сумматора, выход которого соединен с первыми входами второго сумматора и мультиплексора, второй вход которого соединен с выходом переноса первого сумматора а третий - с выходом второго суммато ра, второй вход которого соединен с шиной вспомогательного входа, выход мультиплексора соединен с входом параллельного регистра lj . Однако это устройство обладает ограниченным быстродействием и дост точной сложностью (содержит два сумматора) . Наиболее близким по технической сущности к предлагаемому является каскад цифрового накопителя, содержащий параллельный регистр, первьй и второй двоичные сумматоры, причем первые входы первого двоичного сумматора соединены с кодовыми шинами, а вторые входы подключены к выходам соответствукнцих разрядов параллельного регистра, тактовый вход которого соединен с шиной тактовых импульсов, информационные входы параллельного регистра подключены к выходам суммы второго двоичного сумматора, входы которого подсоединены к выходам суммы и переноса первого двоичного сумматора 2 . Недостатком такого каскада цифрового накопителя является низкое быстродействие, определяемое суммой задержки переключения параллельного регистра и задержки прохождения сигнала через два последовательно соединенных двоичных сумматора. Кроме того, каскад имеет функциональные возможности так как не позволяет ;реализовать функцию двоичного цифро вого накопителя. Цель изобретения - повьЩ1ение быстродействия каскада цифрового на копителя . Поставленная цель достигается тем, что в каскад цифрового накопителя, содержащий регистр и двоичный сумматор, первый вход младшего младшей кодода которого соединен с вой шиной, вход переноса - с входной шиной переноса, выход переноса - с выходной шиной переноса, а вторые входы двоичного сумматора подключены к выходам соответствуюощх разрядов регистра, тактовый вход которого соединен с шиной тактовых импульсов, введены блок кодирования и коммутатор, а в регистр - дополнит ел ьньпЧ разряд, выход которого соединен с управляющим входом коммутатора и с шиной синхронного переноса, причем первые входы разрядов коммутатора подключены к соответствующим старшим кодовым шинам и входам блока кодирования, вторые входы -,к соответствующим выходам блока кодирования, а выходы коммутатора соединены с первыми входами соответствующих старших разрядов двоичного сумматора, выходы суммы и переноса которого соединены с информационными входами соответствующих разрядов регистра. / На чертеже изображена структурная электрическая схема каскада цифрового накопителя. Каскад цифрового накопителя содержит двоичный сумматор 1 (параллельный с последовательным переносом), регистр 2, (параллельный), шину 3 тактовых импульсов, входную и выходную 5 шины переноса, младшую кодовую шину 6, старшие кодовые пшны 7-9, шину 10 синхронного переноса, коммутатор 11, блок 12, кодирования, шину 13 выбора модуля пересчета каскада цифрового накопителя. Блок 12 содержит .инвертор 14, элемент 15 исключающее ИЛИ-НЕ и элемент 16 ИЛИ. В устройстве тактовый вход регистра 2 подключен к шине 3, вход переноса младшего разряда двоичного сумматора 1 соединен с шиной 4, выход переноса старшего разряда двоичного сумматора 1 соединен с шиной 5 и с информационным входом дополнительного разряда регистра 2, первый вход младшего разряда двоичного сумматора 1 соединен с шиной 6, а первые входы старших разрядов двоичного сумматора соединены с соответствующими выходами коммутатора 11, управляюп1ий вход коммутатора 11 подключен к ршне- 10 и к выходу дополнительного разряда регистра 2, выходы остальных разрядов которого соединены с вторыми входами соответствующих разрядов двоичного сумматора 1, первые входы .коммутатора 11 подсоединены к шинам 7-9 и к выходам блока 12, вто рые входы коммутатора 11 подключены к вькодам блока 12, дополнительный управляющий вход коммутатора подсоединен к шине 13. Каскад хщфрового накопителя работает следую1щм образом. Тактовые импульсы подаются на шину 3 устройства, выходной сигнал сни мается с шины 5 или с шины 10 устрой При подаче на шину 13 потенциального сигнала с уровнем логического нуля вне зависимости от наличия или отсутствия сигнала синхронного пере носа на выходы коммутатора 11 передается информация с его первых входов. В результате с кодовых шин 6-9 входная информация в двоичном коде без изменения поступает непосредственно и через коммутатор 11 на перв входы двоичного сумматора 1, и устройство реализует функцию двоичного цифрового накопителя. При подаче на шину 13 потенциаль ного сигнала с уровнем логической единицы коммутатор 11 начинает реагировать на сигнал синхронного пере носа, поступающий на его управляющий вход. Устройство работает следующим образом. Входная информация в двоично-деся тичном коде 1-2-4-8, соответствующая значениям чисел от О до 9, поступает на кодовые шины 6-9. В блоке 12 осуществляется операция перекодирования равнозначная прибавлению к входной информации фиксированного числа 6. При отсутствии сигнала синхронного переноса входная информация с кодовьк шин 6-9 без изменения поступает непосредственно, а также через первые входы и выходы коммутатора 11 на первые входы двоичного сумматора 1. При возникновении сигнала синхрон ного переноса на выходы коммутатора 11 передается информация с его вторых входов. При этом на первые входы двоичного сумматора 1 поступает информация в двоично-десятичном коде с избытком 6, соответствующая числам 494 от 6 до 15.. В результате устройство реализует функцию десятичного накопителя. При реализации устройства на однотипных логических элементах время переключения коммутатора не превышает время формирования сигнала переноса первого младшего разряда двоичного сумматора. При этом коммутация кодов на первых входах второго и последующих старших разрядов двоичного сумматора не оказывает влияния на время формирования выходных сигналов параллельного двоичного сумматора с последовательным переносом. В результате быстродействие каскада цифрового накопителя при модуле пересчета, равном 10, такое ж.е, как и при модуле пересчета, равном 16, т.е. определяется суммой задержки переключения параллельного регистра и задержки прохождения сигналов через двоичный сумматор. На основе устройства может быть построен многокаскадный параллель- ный цифровой накопитель с синхронным групповым переносом. Для этого шина 4 переноса каждого последующего старшего каскада должна быть подключена- к шине 10 синхронного переноса предьщущего каскада, а шины 3 всех каскадов - объединены. Особенностью работы такого, накопителя является то, что максимальная тактовая частота устройства определяется быстродействием одного каскада и не уменьшается с ростом числа каскадов. Цифровой накопитель с синхронным переносом может быть использован в системах, к которым не предъявлены особые требования к величине задержки формирования сигнала синхронного переноса, например, в декадных генераторах псевдорегулярной последовательности импульсов - в системах прямого синтеза частоты, а также в качестве блока дробных разрядов делителя, частоты с дробным переменным коэффициентом деления - в систе- мах косвенного синтеза частоты. Быстродействие предпагаемого устройства в полтора раза выше аналогичного показателя прототипа. Это объяс-. няется тем, что быстродействие базового объекта определяется суммой задержек прохождения сигнала через три приблизительно равных по быстродей$1140249б

ствию функциональных узла - парал- Изобретение имеет широкие функлельный регистр и два двоичных сум-циональные возможности, так как

матора. Быстродействие предлагаемо-предлагаемьш каскад цифрового накого каскада цифрового накопителя опре-пителя путем довольно простого педеляется йуммой йадержки прохождения 5реключения позволяет реализовать как

сигналов только через один двоичныйфункцию десятичного, так и функцию

сумматорами параллельный регистр.двоичного накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерный накапливающий сумматор | 1984 |

|

SU1190380A1 |

| Устройство для сложения чисел с переменным основанием системы счисления | 1990 |

|

SU1714590A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Устройство для сложения чисел с переменным основанием системы счисления | 1985 |

|

SU1310809A1 |

| Система цифровой передачи и приема сигналов цветного телевидения | 1978 |

|

SU764150A1 |

КАСКАД ЦИФРОВОГО НАКОПИТЕЛЯ, содержащий регистр и двоичньй сумматор, первьй . вход младшего разряда которого соединен с младшей кодовой шиной, вход переноса - с входной шиной переноса, выход переноса - с выходной шиной переноса, а вторые входы двоичного сумматора подключены к выходам соответствуюпщх разрядов регистра, тактовый вход которого соединен с шиной тактовых импульсов, отличающийс я тем, что, с целью повьш1ения быстродействия, в него введены блок кодирования и коммутатор, а в регистр - дополнительный разряд, выход которого соединен с управлянкцим входом комм татора и с шиной синхронного переноса, причем первые входы разрядов коммутатора подключены к соответствуюЬщм старшим кодрвьм шинам и входам блока кодирования, вторые входы - к соответствующим выходам блока кодирования, а выходы коммутатора соединены с. первыми входами соответствующих старших разрядов двоичного сумматора, выходы суммы и переноса которого соединены с информационными входами соответствующих разрядов регистра.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-02-15—Публикация

1983-09-29—Подача