Изобретение относится к вычислительной технике и может быть испольовано в цифровых накопителях, делителях с переменным коэффициентом деления j а также для формирования дискретной сетки частот.

Известно устройство, в состав ко- : торого входят три регистраt переключатель кодов, триггер, генератор тактовых импульсов, элемент ИЛИ и суматор.

Недостатком данного устройства является невозможность его функциоирования в двоично-десятичной системе счисления. .

Наиболее близким к предлагаемому

стройству является устройство, соержащее в каждой тетраде два комбинациойных сумматора, мультиплексор, коммутатор, триггер и регистр, разрядные Егыходы f OTOporo соединены соответственно с информационными входами первой группы первого сумматора и с выходной шиной устройства, тактовый яход регистра каждой тетрады соединен с тактовым входом устройства и соответственно с входом установки риггера, единичный вход которогов каждой тетраде соединен с выходом ; переноса первого сумматора, разрядные выходы которого соединены соответственжэ с информационными входами регистра, информационные входы второй группы первого сумматора каждой тетрады соединены с разрядными выхог дами мультиплексора, информационные входы первой группы которого соединены соответственно с информационной шиной устройства и с информационными входами первой группы второго сумматора,, информационные входы второй группы которого соединены соответстsei Ho с шиной управления модулем устройства, а разрядные выходы второго сумматора каждой тетрады соединены с информационными входами второй группы мультиплексора, управляющий вход которого а кажой тетраде соединен с выходом коммутатора, управляющие входы ко мутатора каждой тетрйды соединены с входом выбора системы счисления устройства, первый информационный вход коммутатора каждой тетрады соединен с выходом соответствующего триггера, вторые информационные входы коммутаторов во всех тетрадах соединены с выходом триггера старшей (п-йХ тетрады, причем выходы переноса первого и второго комбинационных сумматоров i-й тетрады (где i 1,2,...,) соединены соответственно с входами переноса (1ч-1)-й тетрады.

Данное устройство может функционировать как в двоичной, так и в двоично-десятичной системах счисления, однако его недостатком является чрезмерная сложность.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем

5 что в устройство для сложения чисел с переменным основанием системы счисления , содержащее в каждой тетраде коммутатор, регистр и первый и второй комбинационные сумматоры, причем

0 разрядные выходы первого комбинационного сумматора соединены соответственно с информационными входами регистра, тактовый вход которого соединен с тактовым входом устройства,

5 выходная шина которого соединена с разрядными выходами регистра в каждой тетраде, информационные входы первой группы второго сумматора каждой тетрады соединены соответственно

0 с информационной шиной устройства, вход выбора системы счисления которого соединен с управляющим входом коммутатора в каждой тетраде, выходы переноса первого и второго комбинационных сумматоров i-й тетрады (где i 1,2,.о,п-1) соединены соответственно с входами переноса (1+1)-й тетрады, дополнительно в каждую его тетраду введена группа из четырех

0 элементов И, первые входы которых соединены соответственно с разрядами шины управления модулем устройства, выход коммутатора каждой тетрады соединен с вторыми входами элементов

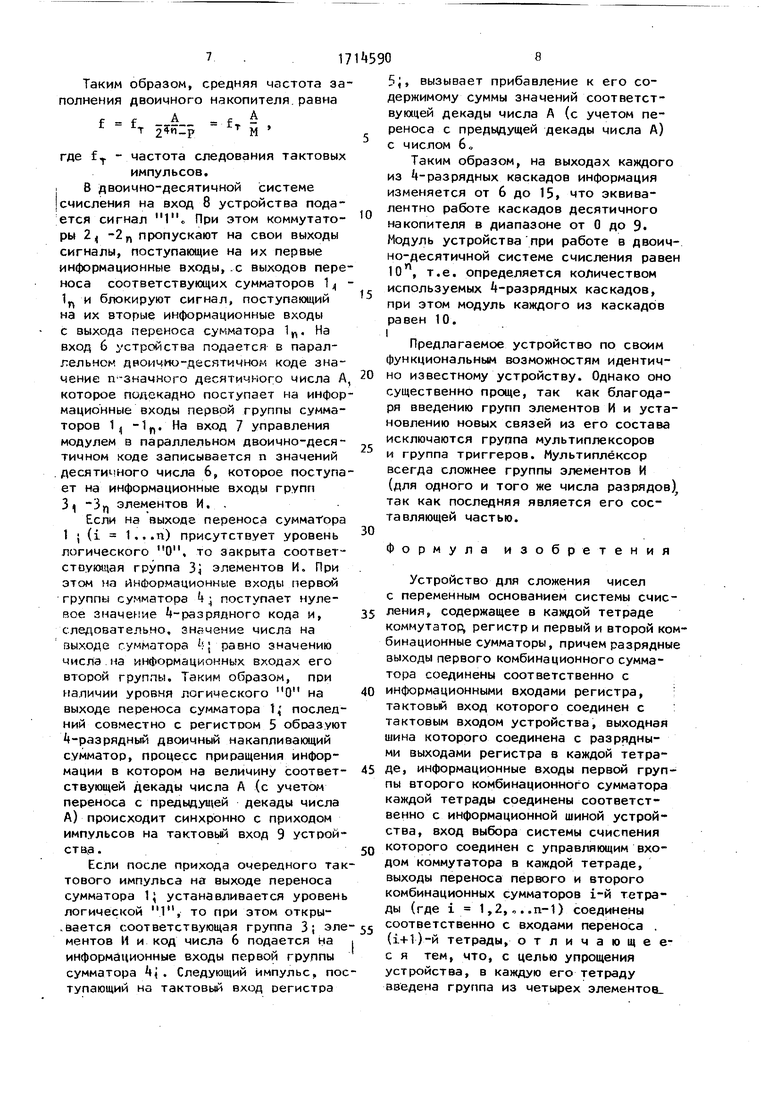

5 И группы, выходы которых соединены соответственно с информационными входами первой группы первого комбинационного сумматора, информационные входы второй группы которого соедиQ нены соответственно с разрядными выходами второго комбинационного сумматора. Информационные входы второй группы последнего соединены с разрядными выходами регистра, выход переноса второго комбинационного сумматора в каждой тетраде соединен с первым информационным входом коммутатора, вторые информационные входы которых во всех тетрадах соединены с выходом переноса второго комбинационного сумматора п-й тетрадыо Сущность изобретения заключается в том, что введение в состав устройства группы элементов И и установление новых связей позволяет организовать процесс сложения чисел с переменным основанием системы счисления без использования группы мультиплексоров и группы триггеров„ По сравнению с известным предлагае мое устройство отличается наличием новых элементов: групп элементов И в каждой из .тетрад устройства с их связпми с коммутатором, первым сумматором и шиной управления модулем устройства, а также новыми связями между сумматорами, регистром и коммутаторами в каждой из тетрад устройства На чертежеизображена структурная схема устройства для сложения чисел с переменным основанием системы счисления „ Устройство состоит из комбинацйонных сумматоров -1ц, коммутаторов 2 -2f, групп 3i -Зп элементов И, комбинационных сумматоров 4 , ре гистров , информационной шины 6, шины 7 управления модулем, входа 8 .выбора системы счисления, тактового входа 9 и выходной шины 10. Устройство работает следующим образом. В двоичной системе счисления на вход 8 устройства подается сигнал О При этом коммутаторы 2 -2 пропускают на свои выходы сигнал, поступаю щий на их вторые информационные вход с выхода переноса сумматора .1у и бло кируют сигналы, поступающие на их пе |Вые информационные входы, с выходов переноса остальных сумматоров 1„ -1лм Сигналы на выходах переноса комбинационных сумматоров 1 -1 и t/i п имеют потенциальный характер и, следовательно, могут изменять свой логический уровень только после прихода очередного тактового импульса на вход 9 устройства. На входе 6 устройства присутствует в двоичном параллельном коде Ц п-разрядное входное число А, которое разбивается на п групп по четыре разряда и подается на соответствующие информационные входы первых групп сумматоров -If,,причем младшие разряды числа А подаются на соответствующие входы сумматора На вход 1 06 7 устройства подается в параллельном двоичном коде k п-разрядное число Р 2 -М, где М - значение модуля. Число Р также разбивается на п групп по четыре двоичных разряда и поступает на информационные входы групп 3 3 элементов И, причем младшие разряды числа Р подаются н,а соответствующие входы группы 3 элементов И. Пусть на выходе переноса сумматора If, присутствует уровень логического Этот уровень через коммутаторы 2/, -2f, подается на управляющие входы всех групп 3, -3 элементов И, которые при этом ...закрываются и нулевое значение двоичных кодов с их выходов подается на информационные входы первой группы сумматоров 4 п- При этом выходной код сумматоров - равен коду на ин- . формационных входах их вторых групп, т.е« коду на разрядных выходах сумматоров 1 п Таким образом, при наличии уровня логического О на выходе переноса сумматора 1„ комбинационные сумматоры Ц -1« и регистры 5 5f) образуют единый ч п-разрядный двоичный накапливающий сумматор, процесс приращения информации в котором на величину входного числа А происходит синхронно с приходом тактовых импульсов на тактовые входы регистров 5 -5п. При достижении числом S в регистрах 5) 1-5 значения, при котором выполняется условие S+Ab2 , на выходе переноса сумматора 1 появляется уровень, логической 1, который через коммутаторы 2 -2 подается на управляющие входы всех групп 3 3 элементов И Последние при этом открываются, пропуская на информационные входы первой группы сумматоров k -k число Ро С приходом очередного тактового импульса на вход 9 устройства к содержимому регистров 5 5 ( прибавляется число А+Р, после .этого на выходе переноса сумматора 1rt устанавливается уровень логического О, группы 3 -Зц элементов И закрываются и возобновляется процес.с заполнения-емкости регистров 5 -5ц с ПОСТОЯННЫМприращением, равным числу АО Такой процесс продолжается до следующего переполнения содержимого . сумматоров 1/1 -1п т,е, до появления уровня логической 1 на выходе сумматора 1 я о 7 . 1 Таким образом, средняя частота за полнения двоичного накопителя.равна А f А т М где f - частота следования тактовых импульсов. В двоично-десятичной системе счисления на вход 8 устройства подается сигнал При этом коммутаторы 2 -2п пропускают на свои выходы сигналы, поступающие на их первые информационные входы,-с выходов пере носа соответствующих сумматоров 1 1у, и блокируют сигнал, поступающий на их вторые информационные входы с выхода переноса сумматора 1, На вход 6 устройства подается в параллельном дроичио-десятичном коде значение п-значного десятичного числа А которое подекадно поступает на инфор мационные входы первой группы сумматоров 1 -If,, На вход 7 управления модулем в параллельном двоично-десятичном коде записывается п значений десятичного числа 6, которое поступа ет на информационные входы групп 31) -3 элементов И. . Если на выходе переноса сумматора 1 ; (i 1,..п) присутствует уровень логического О, то закрыта соответствующая группа 3j элементов И. При этом на информационные входы первой группы сумматора k поступает нулевое значение -разрядного кода и, следовательно, знвмение числа на выходе сумматора :-| равно значению числа.на информационных входах его второй группы. Таким образом, при наличии уровня логического О на выходе переноса сумматора t, последний совместно с регистром 5 обоаз.уют А-разрядный двоичный накапливающий с.умматор, процесс приращения информации в котором на величину соответствующей декады числа А (с учетом переноса с предыдущей декады числа А) происходит синхронно с приходом импульсов на тактовьй вход 9 устройствэ. Если после прихода очередного так тового импульса на выходе переноса сумматора 1; устанавливается уровень логической 1, то при этом откры.веется соответствующая группа 3; эле ментов И и код числа 6 подается на информационные входы первой группы сумматора . Следующий импульс, по тупающий на тактовый вход регистра 08 5;, вызывает прибавление к его содержимому суммы значений соответствующей декады числа А (с учетом переноса с предьщущей декады числа А) с числом 6„ Таким образом, на выходах каждого из (-разрядных каскадов информация изменяется от 6 до 15, что эквивалентно работе каскадов десятичного накопителя в диапазоне от О до 9. Модуль устройства при работе в двоично-десятичной системе счисления равен Ю, т.е. определяется количеством используемых -разрядных каскадов, при этом модуль каждого из каскадов равен 10. Предлагаемое устройство по своим функциональным возможностям идентично известному устройству. Однако оно существенно проще, так как благодаря введению групп элементов И и установлению новых связей из его состава исключаются группа мультиплексоров и группа триггеров. Мультиплексор всегда сложнее группы элементов И (для одного и того же числа разрядов), так как последняя является его составляющей частью. Формула изобретения Устройство для сложения чисел с переменным основанием системы счисления, содержащее в каяадой тетраде коммутатор, регистр и первый и второй комбинационные сумматоры, причем разрядные выходы первого комбинационного сумматора соединены соответственно с информационными входами регистра, тактовьй вход которого соединен с : тактовым входом устройства, выходная шина которого соединена с разрядными выходами регистра в каждой тетраДе, информационные входы первой группы второго комбинационного сумматора каждой тетрады соединены соответственно с информационной шиной устройства, вход выбора системы счиспения которого соединен с управляющим входом коммутатора в каждой тетраде, выходы переноса первого и второго комбинационных сумматоров i-й тетрады (где i 1,2,О..П-1) соединены соответственно с входами переноса . (1+1)-й тетрады, отличающеес я тем, что, с целью упрощения устройства, в каждую его тетраду введена группа из четырех элементоа.

И, первые входы которых соединены соответственно с разрядами шины управления модулем устройства, выход коммутатора каждой тетрады соединен с вторыми входами элементов И группы выходы которых соединены соответственно с информационными входами первой группы первого комбинационного сумматора, информационные входы второй группы которого соединены соответственно с разрядными выходами второго комбинационного сумматора, информационные входы второй группы которого соединены соответственно с разрядными выходами регистра, выход переноса второго комбинационного сумматора в каждой тетраде соединен с первым информационным входом коммутатора, вторые информационные входы которых во всех тетрадах соединены с выходом переноса второго коибинационного сумматора п-й тетрады.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения чисел с переменным основанием системы счисления | 1985 |

|

SU1310809A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для умножения | 1982 |

|

SU1229758A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых накопителях, делителях с переменным коэффициентом деления, а также формирования дискрет-| ной сетки частот. Цель изобретения -: упрощение устройства. Устройство для сложения чисел с переменным основанием системы счисления содержит п пер-, вых комбинационных сумматоров 1, п коммутаторов 2, п групп из четырех элементов И 3, п вторых комбинационных сумматоров Л, п регистров 5, информационную шину 6, шину 7 управления модулем, вход 8 выбора системы счисления, тактовый вход 9 и выходную шину 10, соединенные между собой функционально. 1 ил. •'у^^ ел ю о

| Питатель-распределитель медицинских таблеток | 1957 |

|

SU116916A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| i (Sk) УСТРОЙСТВО для СЛОЖЕНИЯ ЧИСЕЛ с ' ПЕРЕМЕННЫМ ОСНОВАНИЕМ СИСТЕМЫ СЧИСЛЕ-^ НИЯ | |||

Авторы

Даты

1992-02-23—Публикация

1990-03-19—Подача