(Л

00

Х)

ГчЭ

ГЖ1

Изобретение относится к автоматике, в частности к передаче информации, и мо- |кет быть использовано для передачи цифровых сообщений от территориально уда- Ленных или большого числа малоактивных локализованных источников, информация от которых может передаваться по любому из заданного множества выходных каналов.

Целью изобретения является увеличение быстродействия устройства за счет полного

та 8 задержки поступает на первый управляющий вход коммутатора 3 и на входы источников I. Элемент 8 служит для задержки сигнала на время, необходимое для срабатывания входящих в устройство элементов.

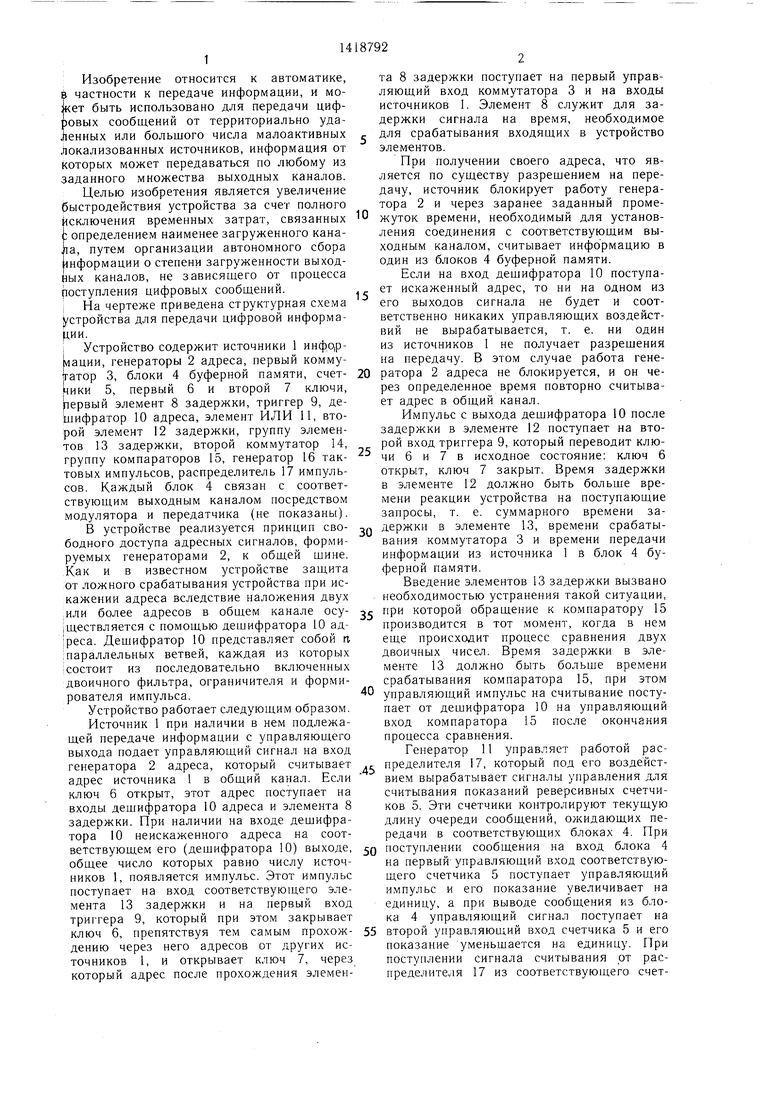

При получении своего адреса, что является по существу разрещением на передачу, источник блокирует работу генератора 2 и через заранее заданный промеk определением наименее загруженного кана- iia, путем организации автономного сбора Информации о степени загруженности выход- йых каналов, не зависящего от процесса поступления цифровых сообщений. ; На чертеже приведена структурная схема устройства для передачи цифровой информации.

; Устройство содержит источники 1 информации, генераторы 2 адреса, первый комму15

iin „

исключения временных затрат, связанных жуток времени, необходимый для установления соединения с соответствующим выходным каналом, считывает информацию в один из блоков 4 буферной памяти.

Если на вход дещифратора 10 поступает искаженный адрес, то ни на одном из его выходов сигнала не будет и соответственно никаких управляющих воздействий не вырабатывается, т. е. ни один из источников 1 не получает разрещения на передачу. В этом случае работа генератор 3, блоки 4 буферной памяти, счет- 20 ратора 2 адреса не блокируется, и он че- ики 5, первый 6 и второй 7 ключи, рез определенное время повторно считыва- ервый элемент 8 задержки, триггер 9, де- ет адрес в общий канал. Шифратор 10 адреса, элемент ИЛИ 11, вто-Импульс с выхода дещифратора 10 после

рой элемент 12 задержки, группу элемен- задержки в элементе 12 поступает на вто- тов 13 задержки, второй коммутатор 14, рой вход триггера 9, который переводит клю- группу компараторов 15, генератор 16 так- чи 6 и 7 в исходное состояние: ключ 6 товых импульсов, распределитель 17 импульсов. Каждый блок 4 связан с соответствующим выходным каналом посредством модулятора и передатчика (не показаны). В устройстве реализуется принцип свободного доступа адресных сигналов, формируемых генераторами 2, к общей щине. Как и в известном устройстве защита от ложного срабатывания устройства при искажении адреса вследствие наложения двух

или более адресов в общем канале осу- jc при которой обращение к компаратору 15 ществляется с помощью дещифратора 10 ад- производится в тот момент, когда в нем

еще происходит процесс сравнения двух двоичных чисел. Время задержки в элементе 13 должно быть больще времени

30

открыт, ключ 7 закрыт. Время задержки в элементе 12 должно быть больще времени реакции устройства на поступающие запросы, т. е. суммарного времени задержки в элементе 13, времени срабатывания коммутатора 3 и времени передачи информации из источника 1 в блок 4 буферной памяти.

Введение элементов 13 задержки вызвано необходимостью устранения такой ситуации,

ipeca. Дещифратор 10 представляет собой п :параллельных ветвей, каждая из которых 1СОСТОИТ из последовательно включенных двоичного фильтра, ограничителя и формирователя импульса.

Устройство работает следующим образом. Источник 1 при наличии в нем подлежащей передаче информации с управляющего выхода подает управляющий сигнал на вход

40

срабатывания компаратора 15, при этом

управляющий импульс на считывание поступает от дещифратора 10 на управляющий вход компаратора 15 после окончания процесса сравнения.

Генератор 11 управляет работой расгенератора 2 адреса, который считывает .с. пределителя 17, который под его воздейст- адрес источника 1 в общий канал. Если вием вырабатывает сигналы управления для ключ 6 открыт, этот адрес поступает на считывания показаний реверсивных счетчи- входы дещифратора 10 адреса и элемента 8 ков 5. Эти счетчики контролируют текущую задержки. При наличии на входе дещифра- длину очереди сообщений, ожидающих пе- тора 10 неискаженного адреса на соот- редачи в соответствующих блоках 4. При ветствующем его (дешифратора 10) выходе, о поступлении сообщения на вход блока 4 общее число которых равно числу источ- на первый управляющий вход соответствую- ников 1, появляется импульс. Этот импульсщего счетчика 5 поступает управляющий

поступает на вход соответствующего эле- импульс и его показание увеличивает на мента 13 задержки и на первый вход единицу, а при выводе сообщения кз триггера 9, который при этом закрывает ка 4 управляющий сигнал поступает на ключ 6, препятствуя тем самым прохож- 55 второй управляющий вход счетчика 5 и его дению через него адресов от других ис- показание уменьшается на единицу. При точников 1, и открывает ключ 7, через поступлении сигнала считывания от рас- который адрес после прохождения элемен- пределителя 17 из соответствующего счетта 8 задержки поступает на первый управляющий вход коммутатора 3 и на входы источников I. Элемент 8 служит для задержки сигнала на время, необходимое для срабатывания входящих в устройство элементов.

При получении своего адреса, что является по существу разрещением на передачу, источник блокирует работу генератора 2 и через заранее заданный проме „

задержки в элементе 12 поступает на вто- рой вход триггера 9, который переводит клю- чи 6 и 7 в исходное состояние: ключ 6

при которой обращение к компаратору 15 производится в тот момент, когда в нем

открыт, ключ 7 закрыт. Время задержки в элементе 12 должно быть больще времени реакции устройства на поступающие запросы, т. е. суммарного времени задержки в элементе 13, времени срабатывания коммутатора 3 и времени передачи информации из источника 1 в блок 4 буферной памяти.

Введение элементов 13 задержки вызвано необходимостью устранения такой ситуации,

срабатывания компаратора 15, при этом

управляющий импульс на считывание поступает от дещифратора 10 на управляющий вход компаратора 15 после окончания процесса сравнения.

чика 5 считывается информационная посылка, содержащая адресную часть, которая соответствует адресу данного счетчика 5 и связанного с ним блока 4 буферной памяти, и информационную часть, представ- ляющую собой выраженное в двоичной форме содержимое данного счетчика 5. Эта посылка поступает далее на соответствующий вход компаратора 14.

Алгоритм работы цифрового компаратора 15 следующий. Поступающее на вход ком- паратора 15 двоичное число, которым в данном случае является информационная часть посылки счетчика 5, сравнивается с другим двоичным числом, которое было признано

соответствуюиим информационным входам коммутатора, выходы которого соединены с входами соответствующих блоков буферной памяти, первые выходы которых являются выходами устройства, вторые и третьи выходы блоков буферной памяти соединены соответственно с первыми и вторыми входами соответствующих счетчиков, вторые выходы источников информации через соответствующие генераторы адреса подключены к информационному входу первого ключа, выход которого соединен с входом дешифратора и через первый элемент задержки с информационным входом второго ключа, выход которого соединен с входами источника инфорнаименьшим на предыдущем такте работы 15 „ации и первым управляющим входом ком- компаратора 15. Если поступивщее двоичное число больше или равно ранее записанному, то содержимое компаратора 15 не изменяется, в противном случае вместо старого минимального двоичного числа запи-ШРРГ

сывается новое. Под воздействием управляю- 20 „„.„...„й

щего сигнала, поступающего от дешифратора 10 адреса, считывается только адрес наименьшего двоичного числа, который поступает на второй управляющий вход коммутатора 3.

Таким образом, на управляющие входы коммутатора 3 поданы как адрес источника 1, затребовавшего канал связи, так и адрес наименее загруженного (или одного из наименее загруженных) канала. После срабатывания коммутатора 3 сообщение ис- 30 точника 1 переписывается в соответствующий данному каналу блок 4 буферной памяти.

мутатора, триггер, первый и второй выходы которого подключены к управляющим входам первого и второго ключей соответственно, генератор тактовых импульсов, отличаю- с целью повыщения

быстродействия устройства, в него введены матричный коммутатор, группа элементов задержки, группа компараторов, второй элемент задержки, элемент ИЛИ, распределитель импульсов, выходы которого 25 подключены к третьим входам счетчиков, выходы которых соединены с входами матричного коммутатора, выходы которого подключены к первым входам компараторов группы, выходы которых объединены и подключены к второму управляющему входу компаратора, выход генератора тактовых импульсов соединен с входом распределителя импульсов, выходы дешифратора адреса соединены с соответствующими входами элемента ИЛИ и через соответствующие элементы задержки группы с вторыми входами соответствующих компараторов, выход элемента ИЛИ соединен с первым входом и через второй элемент задержки с вторым входом триггера.

Формула изобретения

Устройство для передачи цифровой информации, содержащее источники информации, первые выходы которых подключены к

соответствуюиим информационным входам коммутатора, выходы которого соединены с входами соответствующих блоков буферной памяти, первые выходы которых являются выходами устройства, вторые и третьи выходы блоков буферной памяти соединены соответственно с первыми и вторыми входами соответствующих счетчиков, вторые выходы источников информации через соответствующие генераторы адреса подключены к информационному входу первого ключа, выход которого соединен с входом дешифратора и через первый элемент задержки с информационным входом второго ключа, выход которого соединен с входами источника инфор„ации и первым управляющим входом ком- ШРРГ

5 „ации и первым управляющим входом ком- ШРРГ

0 „„.„...„й

0

мутатора, триггер, первый и второй выходы которого подключены к управляющим входам первого и второго ключей соответственно, генератор тактовых импульсов, отличаю- с целью повыщения

быстродействия устройства, в него введены матричный коммутатор, группа элементов задержки, группа компараторов, второй элемент задержки, элемент ИЛИ, распределитель импульсов, выходы которого 5 подключены к третьим входам счетчиков, выходы которых соединены с входами матричного коммутатора, выходы которого подключены к первым входам компараторов группы, выходы которых объединены и подключены к второму управляющему входу компаратора, выход генератора тактовых импульсов соединен с входом распределителя импульсов, выходы дешифратора адреса соединены с соответствующими входами элемента ИЛИ и через соответствующие элементы задержки группы с вторыми входами соответствующих компараторов, выход элемента ИЛИ соединен с первым входом и через второй элемент задержки с вторым входом триггера.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи цифровой информации | 1983 |

|

SU1141436A1 |

| Адаптивное телеизмерительное устройство | 1975 |

|

SU608186A1 |

| Адаптивная телеизмерительная система | 1987 |

|

SU1494023A1 |

| Система радиосвязи с подвижными объектами | 1986 |

|

SU1401626A1 |

| Адаптивный коммутатор системы телеизмерений | 1985 |

|

SU1309071A1 |

| Устройство для отображения полутонового изображения на экране телевизионного приемника | 1988 |

|

SU1522273A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для программного управления транспортным механизмом | 1983 |

|

SU1087959A1 |

| Программируемый источник питания | 1988 |

|

SU1597875A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

Изобретение относится к автоматике, касается,в частности, передачи цифровой информации, и предназначено для передачи цифровых сообщений от рассредоточенных объектов, от которых информация может передаваться по любому из заданного числа каналов. Целью изобретения является повышение быстродействия устройства. Для достижения цели в устройство введены элемент ИЛИ 11, второй элемент 12 задержки, распределитель 17 импульсов, матричный коммутатор 14, группа 15 компараторов. Использование данного устройства обеспечивает автономность процесса сбора информации о степени загруженности выходных каналов от процесса поступления требований на передачу от источников информации и исключение временных затрат на определение наименее загруженного выходного канала. 1 ил.

| Устройство для передачи цифровой информации | 1983 |

|

SU1141436A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-19—Подача