чика, а второй вход элемента ИЛИ с выходом второго счетчика, при этом в каждом из блоков задержки фронта информационные входы первых счетчи-, ков являются информационными входами соответствующего блока задержки, управляющий вход оперативного запоминающего устройства является первым дополнительным , а адресные входы оперативного запоминающе го устройства являются вторым дополнительным входом соответствующего блока задержки фрон та.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2004 |

|

RU2269866C2 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Программируемый генератор импульсов | 1980 |

|

SU949785A1 |

| Устройство для счета количества изображений объекта | 1987 |

|

SU1494021A1 |

| Устройство для обработки сообщений | 1990 |

|

SU1803919A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1285493A1 |

УСТРОЙСТВО ЗАДЕРЖКИ, содержащее датчик кода, генератор, формирователь тактовых импульсов и блок задержки переднего фронта, первьй вход которого подключен к входу устройства и входу датчика кода, второй вход - к выходу формирователя тактовых импульсов, третий вход - к выходу генератора и входу формирователя тактовых импульсов, причем блок задержки переднего фронта состоит из первого и второго счетчиков, оперативного запоминающего устройства и узла управления, первый, второй и третий входы которого являются соответственно первым, вторьм и третьим входами блока задержки переднего фронта, а выход соединен со счетным входом первого счётчика, разрядные выходы которого соединены с информационными входами оперативного запоминакщего устройства, выходы которого соединены с информационнымивходами второго счетчика, о т л и ч.а ю щ е е с я тем, что, с целью расширения диапазона задержек при сохранении длительности задерживаемых импульсов, в него дополнительно введены элемент НЕ, триггер, блок формирования адреса и блок задержки заднего фронта, идентичный блоку задержки переднего фронта, причем выходы блоков задержки переднего и заднего фронтов подключены к соответствующим входам триггера, выход которого является выходом устройства, первый вход блока задержки заднего фронта через элемент НЕ подключен к входу устройства, одноименные вторые, третьи, а также первые и вторые дополнительные входы блоков задержки переднего и заднего фронтов объединены (Л и подключены также соответственно: с вторые - к управляющему входу блока формирования адреса, первый дополнительный - к второму выходу формирователя тактовых импульсов, второй дополнительный - к адресному выходу блока формирования адреса, первые информационные выходы датчика кода 4 подключены к объединенным информациlik онньм входам блоков задержки переднего и заднего фронтов, а вторые - к 00 00 информационным входам блока формирования адреса, в каждый .из блоков задержки переднего и заднего фронтов дополнительно введен элемент ИЛИ. выход которого является выходом со ответствующего блока задержки фронта, первый вход элемента ИЛИ подключен к выходу старшего разряда первого счетчика, объединенного с четвёртым входом соответствующего узла управ- ления, третий вход которого соединен также со счетным входом второго счет

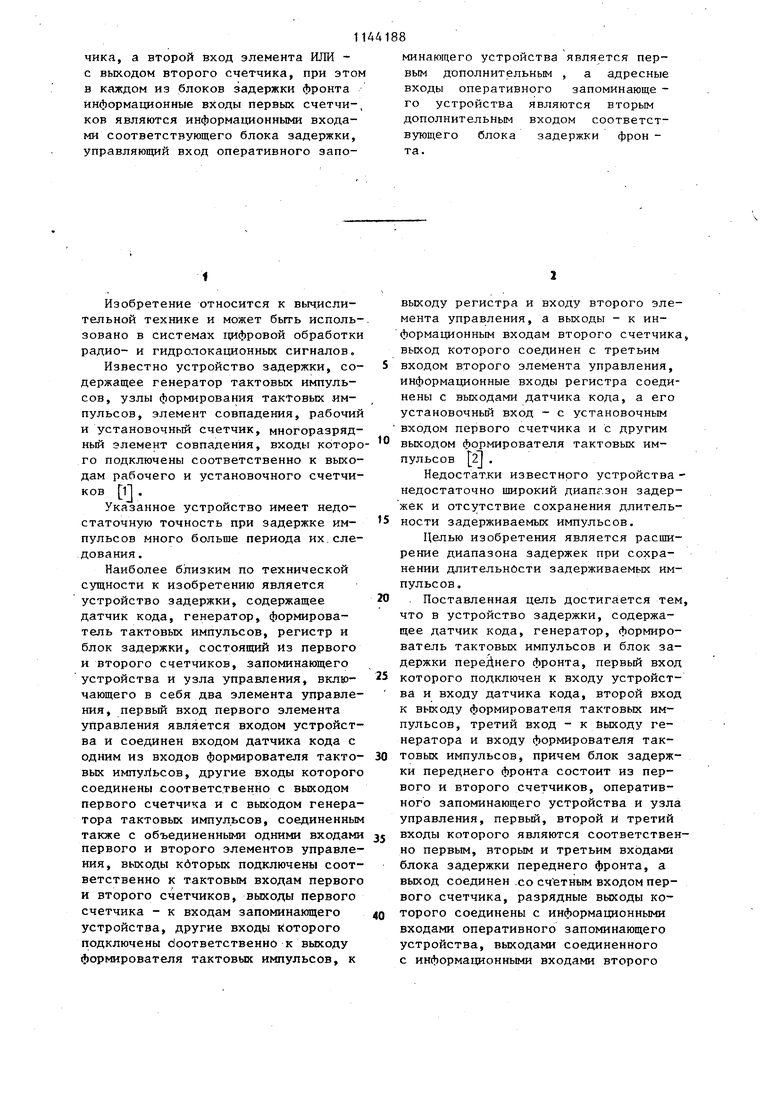

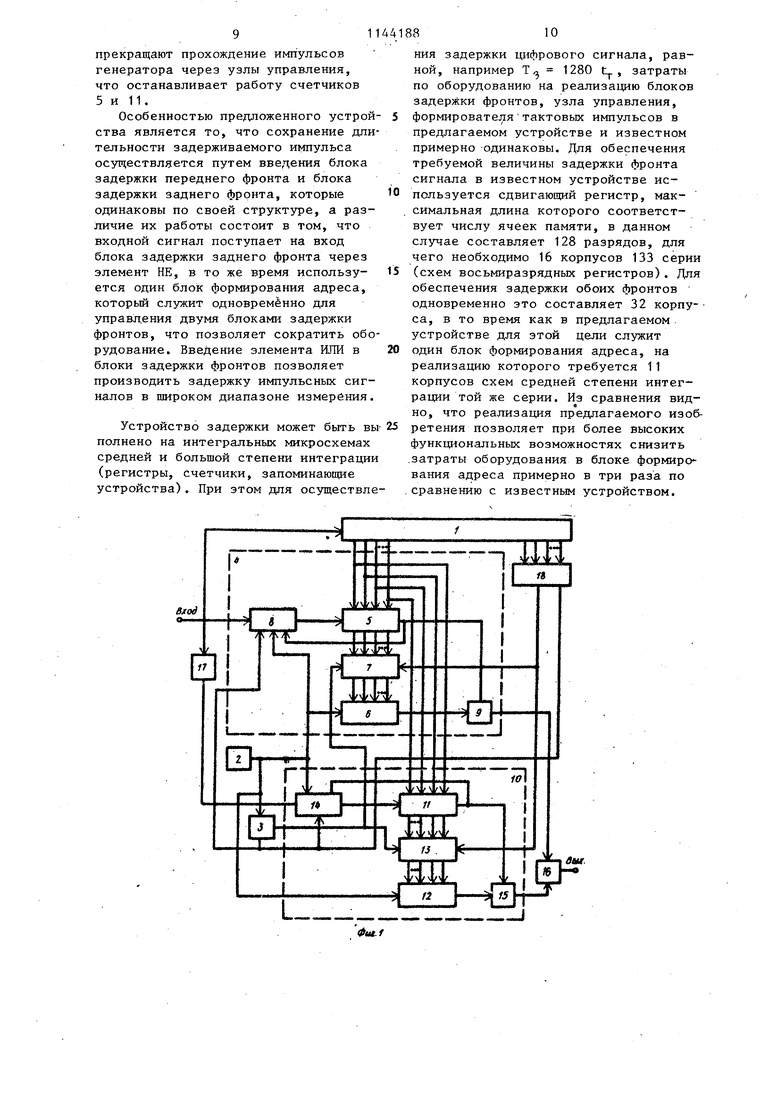

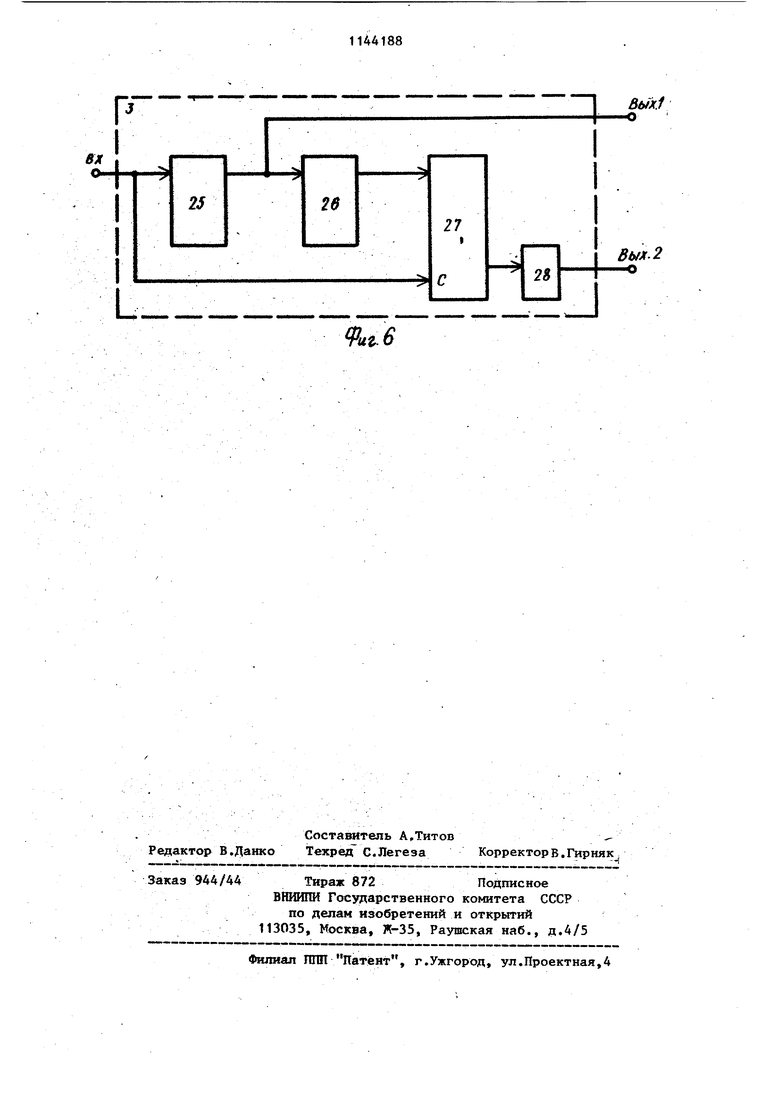

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки радио- и гидролокационных сигналов. Известно устройство задержки, содержащее генератор тактовых импульсов, узлы формирования тактовых импульсов, элемент совпадения, рабочий и установочный счетчик, многоразрядный элемент совпадения, входы которо го подключены соответственно к выходам рабочего и установочного счетчиков Л , Указанное устройство имеет недостаточную точность при задержке импульсов много больше периода их.следования . Наиболее близким по технической сущности к изобретению является устройство задержки, содержащее датчик кода, генератор, формирователь тактовых импульсов, регистр и блок задержки, состоящий Из первого и второго счетчиков, запоминающего устройства и узла управления, включающего в себя два элемента управления, первый вход первого элемента управления является входом устройства и соединен входом датчика кода с одним из входов формирователя тактовых импульсов, другие входы которого соединены соответственно с выходом первого счетчика и с выходом генератора тактовых импульсов, соединенным также с объединенными одними входами первого и второго элементов управления, выходы кйторых подключены соответственно к тактовым входам первого и второго счетчиков, выходы первого счетчика - к входам запоминающего устройства, другие входы которого подключены с оответственно к выходу формирователя тактовых импульсов, к выходу регистра и входу второго элемента управления, а выходы - к информационным входам второго счетчика, выход которого соединен с третьим входом второго элемента управления, информационные входы регистра соединены с выходами датчика кода, а его установочный вход - с установочным входом первого счетчика и с другим выходом формирователя тактовых импульсов z. Недостатки известного устройства недостаточно широкий диапазон задержек и отсутствие сохранения длительности задерживаемых импульсов. Целью изобретения является расщирение диапазона задержек при сохранении длительности задерживаемых импульсов, , Поставленная цель достигается тем, что в устройство задержки, содержащее датчик кода, генератор, формирователь тактовых импульсов и блок задержки переднего фронта, первый вход которого подключен к входу устройства и входу датчика кода, второй вход к выходу формирователя тактовых импульсов, третий вход - к ВЫХОДУ генератора и входу формирователя тактовых импульсов, причем блок задержки переднего фронта состоит из первого и второго счетчиков, оперативного запоминающего устройства и узла управления, первый, второй и третий входы которого являются соответственно первым, вторым и третьим входами блока задержки переднего фронта, а выход соединен .со счетным входом первого счетчика, разрядные выходы которого соединены с информационными входами оперативного запоминающего устройства, выходами соединенного с информационными входами второго счетчика, введены элемент НЕ, триггер, блок формирования адреса и блок задержки заднего фронта, идентичный блоку задержки переднего фронта при чем выходы блоков задержки переднего и заднего фронтов подключены к соответствующим входам триггера, выход которого является выходом устройства, первый вход блока задержки задне го фронта через элемент НЕ подключен к входу устройства, одноименные вторые, третьи и вторые дополнительные входы блоков задержки переднего и заднего фронтов объединены между и подключены также соответствец ю : вторые - к управляющему входу блока формирования адреса, первый дополнитепьньй - к второму выходу формирова теля тактовых импульсов, второй дополнительньй - к адресному выходу блока формирования адреса, первые информационные выходы датчика кода подключены к объединенным информационным входам блоков задержки переднего и заднего фронтов, а вторые - к информационным входам блока формирования адреса, в каждьй из блоков задержки переднего и заднего фронтов дополнительно введен элемент ИЛИ, выход которого является выходом соответствукнцего блока задержки фронта, первьй вход элемента ИЛИ подключен к выходу старшего разряда первого счетчика, объединенного с четвертым входом соответствующего узла управления, третий вход которого соединен также со счетным входом второго счетчика, а второй вход элемента ИЛИ - с выходом второго счетчика, при этом в каждом из блоков задержки фронта информационные входы первых счетчиков являются информационными входами соответствующего блока задержки, управляющий вход оперативного запоминакщего устройства является первым дополнительным, а адресные входы оперативного sanovaiнающего устройства являются вторым дополнительным входом соответствующе го блока задержки фронта. I На фиг. 1 приведена структурная электрическая схема предложенного устройства задержки; на фиг. 2 структурная схема блока формирования адреса; на фиг. 3 - таблица, поясня ющая работу блока формирования адре са; на фиг. 4 - временная диаграмма работы устройства задержки; на фиг.5 схема узла управления; на фиг. 6 схема формирователя тактовых импульсов. Устройство задержки содержит датчик 1 кода, генератор 2, формирователь 3 тактовых импульсов, блок 4 задержки переднего фронта,, первый вход которого подключен к входу устройства и входу датчика 1 кода, второй вход - к выходу формьгрователя 3 тактовых импульсов, третий вход - к выходу генератора 2 и входу формирователя 3 тактовых импульсов,, блок 4 задержки переднего фронта, в который входят nepBbrii 5 и второй 6 счетчики, оперативное запоминающее устройство 7 и узел 8 управления, первьй, второй и третий входы которого являются соответственно первым, вторым и третьим входами блока 4 задержки переднего фронта , а выход соединен со счетным входом первого счетчика 5, разрядные выходы которого соединены с информационными входами оперативного запоминающего устройства 7, выходы которого соединены с информационными входами второго счетчика 6, элемент ИЛИ 9, выход которого является выходом блока 4 задержки переднего фронта, первьй вход элемента ИЛИ подключен к выходу старшего разряда первого счетчика 5, объединенному с четвертым входом узла 8 управления, третий вход которого соединен также со счетным входом второго счетчика 6, а второй вход элемента ИЛИ 9 - с выходом второго счетчика 6. Устройство задержки содержит также блок 10задержки заднего фронта идентичньй блоку задержки переднего фронта, содержащий первьй 11 и второй 12 счетчики, оперативное запоминающее устройство 13 и узел 14 . управления, входы которого являются соответствукнцими входами блока 10 задержки заднего фронта, а выход сое динен со счетным входом первого счетчика 11, разрядные выходы которого соединены с информационными входами оперативного запоминаю1цего устройства 13, выходами соединенного с информационными входами второго счетчика 12, элемент ИЛИ 15, выход которого является выходом блока 10 задержки заднего фронта, первый вход элемента ИЛИ 15 подключен к выходу старшего разряда первого счетчика 11,

объединенного с четвертым входом соотв€ тствуннцего узла управления, третий вход которого соединен также со счетным входом второго счетчика 12

Выходы блоков переднего и заднего фронтов подключены к соответствующим входам триггера 16, выход которого является выходом устройства, первьй вход блока 10 задержки заднего фронта через элемент НЕ 17 подключен к входу устройства, одноименные вторые, третьи, а также первые и вторые дополнительные входы блоков задержки переднего 4 и заднего 10 фронтов объединены между собой и подключены также соответственно: вторые к управляющему входу блока 18 формирования адреса, первый дополнительный - к второму входу формирователя 3 тактовых импульсов, второй допелнитель.ный -.к адресному выходу блока 18 формирования адреса, первые информационные выходы датчика 1 кода подключены и объединены информационным входам блоков задержки переднего 4 и заднего 10 фронтов, а вторые - к информационным входам блока 18 формирования адреса.

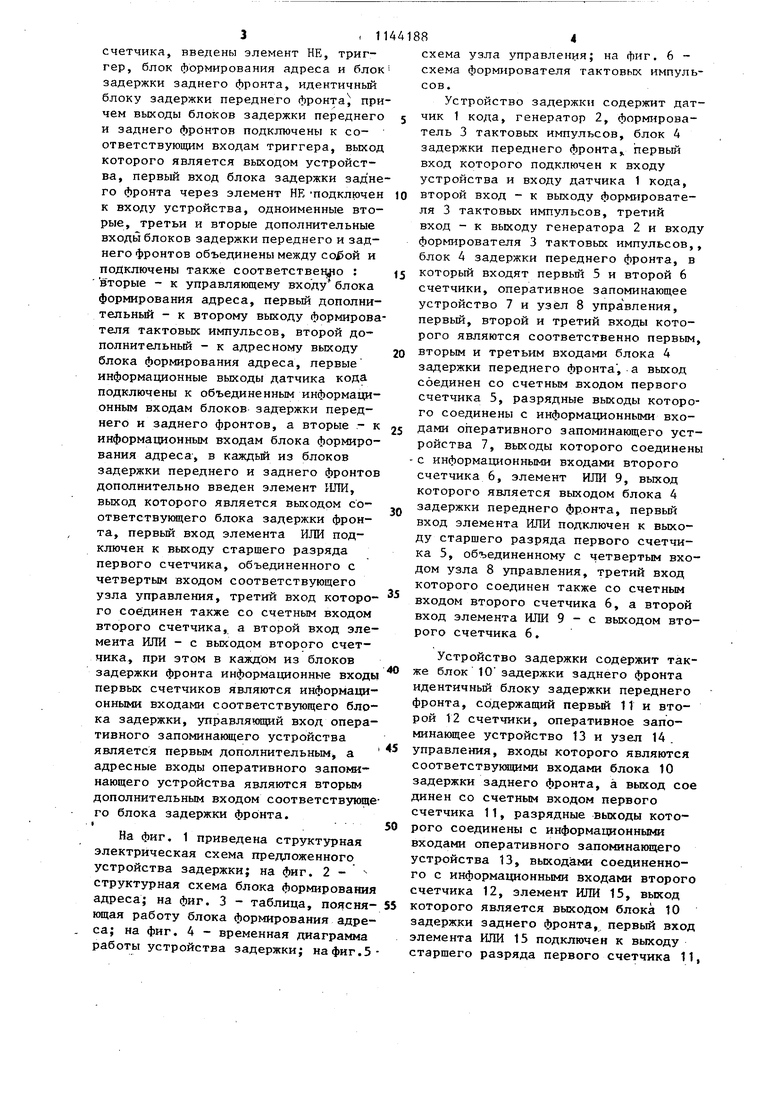

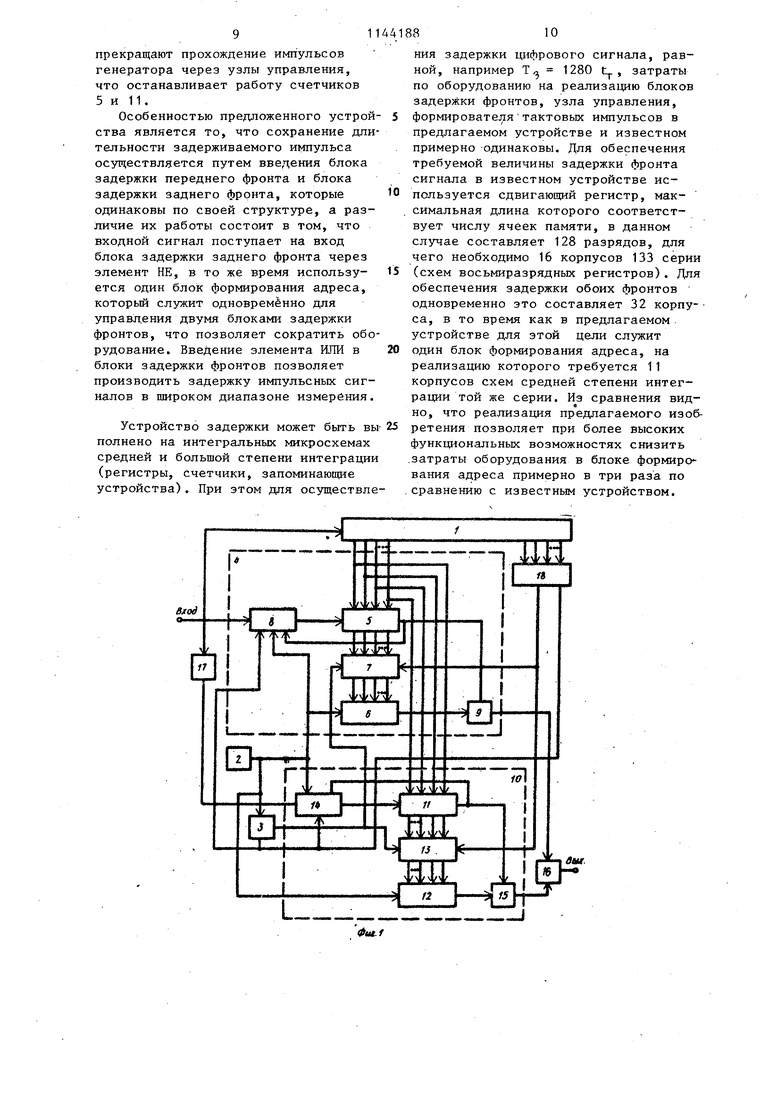

Информационными входами блоков задержки переднего 4 и заднего 10 фронтов являются информационные входы соответствующих первых счетчиков 5 и 11, управляющий вход оперативного запоминающего устройства в каждом из блоков задержки является первым дополнительным, а адресные входы оперативного запоминающего устройства - вторым дополнительным входом соответствующего блока задержки фронта. Блок 18 формирования адреса (фиг. 2) содержит суммирующий счетчи 19, эычитатель 20, первьй 21 и вто-. рой 22 элементы И, элемент ИЛИ 23 и элемент НЕ 24.

Информа1дионные выходы суммирующего счетчика 19 соединены с входами вычитателя 20, а также с входами элемента И 21, управляющий вход которого соединен с выходом элемента НЕ 24, выход которого соединен-с суммирующим входом счетчика 19, а также с управляющим входом элемента И 22 и является управляющим входом блока 18 .формирования адреса. Информационные выходы вычитателя 20 соединены с входами элемента И 22, выходы которого соединены с первыми входами элемента ИЖ 23, вторые входы

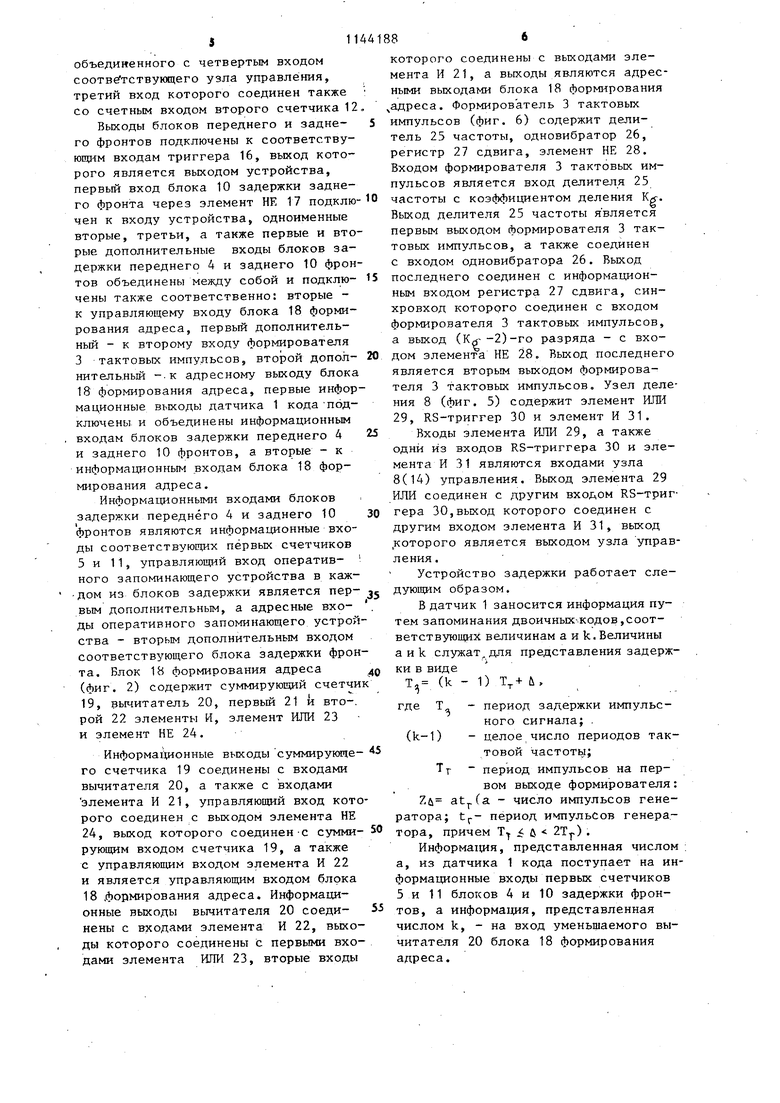

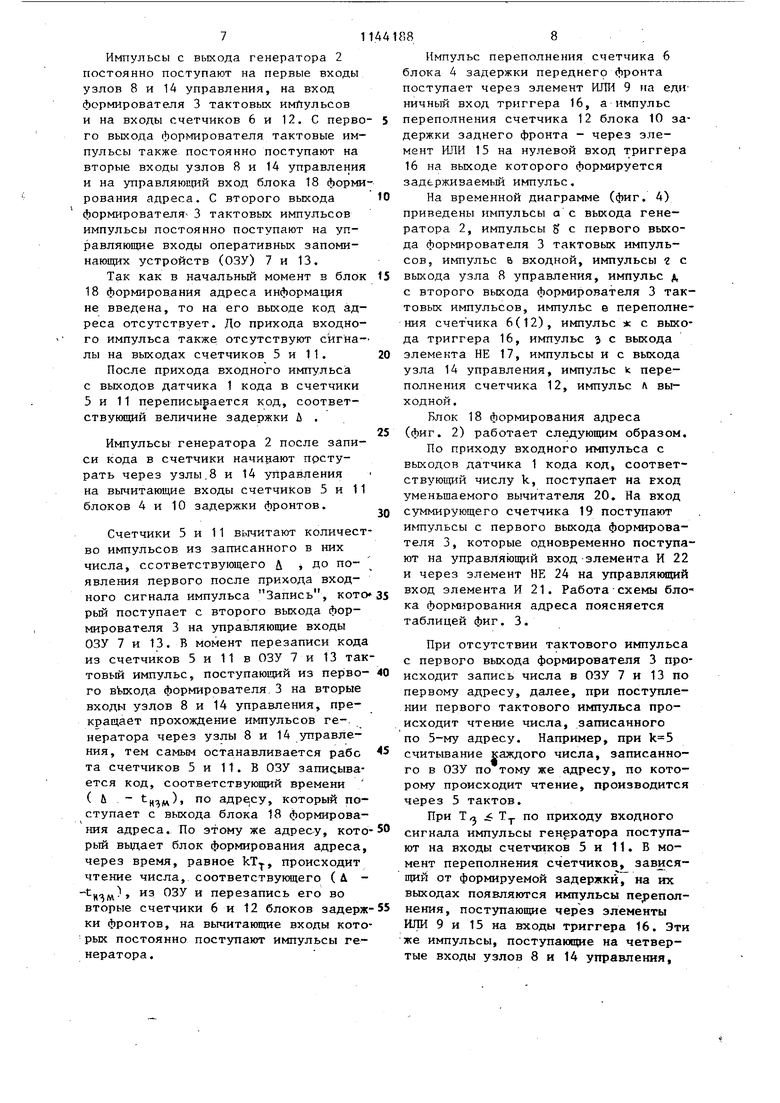

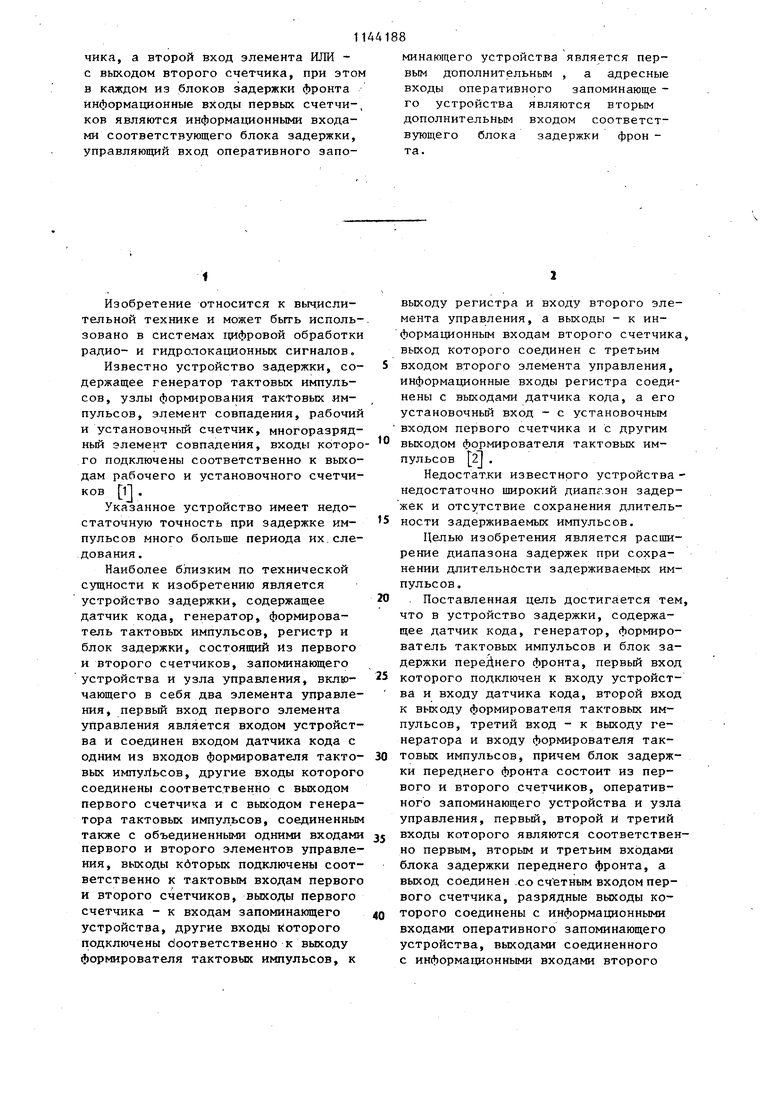

которого соединены с выходами элемента И 21, а выходы являются адресными выходами блока 18 формирования .адреса. Формирователь 3 тактовых импульсов (фиг. 6) содержит делитель 25 частоты, одновибратор 26, регистр 27 сдвига, элемент НЕ 28. Входом формирователя 3 тактовых импульсов является вход делителя 25 частоты с коэффициентом деления Kg-. Выход делителя 25 частоты является первым вьсходом формирователя 3 тактовых импульсов, а также соединен с входом одновибратора 26. Выход последнего соединен с информационным входом регистра 27 сдвига, синхровход которого соединен с входом формирователя 3 тактовых импульсов, а выход (Krf--2)-ro разряда - с входом элемента НЕ 28. Выход последнего является вторым выходом формирователя 3 тактовых импульсов. Узел деления 8 (фиг. 5) содержит элемент ИЛИ 29, RS-триггер 30 и элемент И 31.

Входы элемента ИЛИ 29, а также одни из входов RS-триггера 30 и элемента И 31 являются входами узла 8(14) управления. Выход элемента 29 ИЛИ соединен с другим входом RS-триггера 30,выход которого соединен с другим входом элемента И 31, выход которого является выходом узла управления.

Устройство задержки работает следующим образом.

В датчик 1 заносится информация путем запоминания двоичных-ксздов,соответствующих величинам а и k.Величины аии служат для представления задержки в виде T,j (k - 1) Ь.

где Т - период задержки импульсного сигнала; .

(k-1) - целое число периодов тактовой частоты;

Т г период импульсов на первом выходе формирователя Zu at(a - число импульсов генератора; t,-- период импульсов генератора, причем TY :6 U 2Т) .

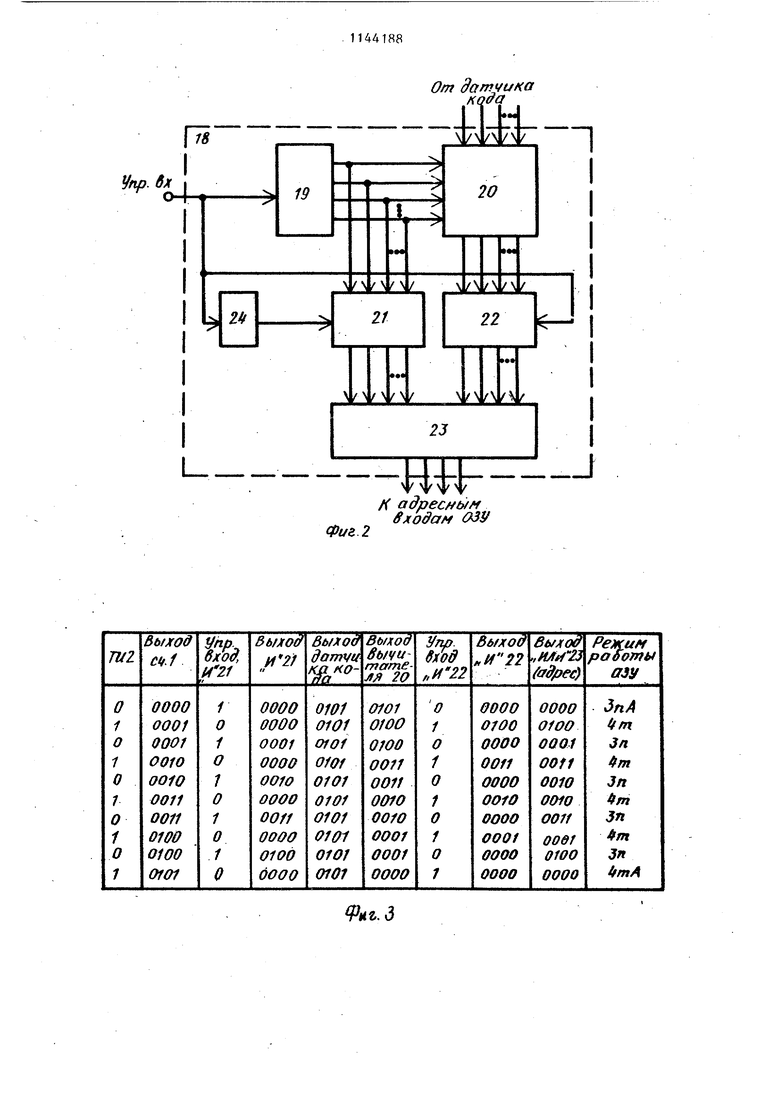

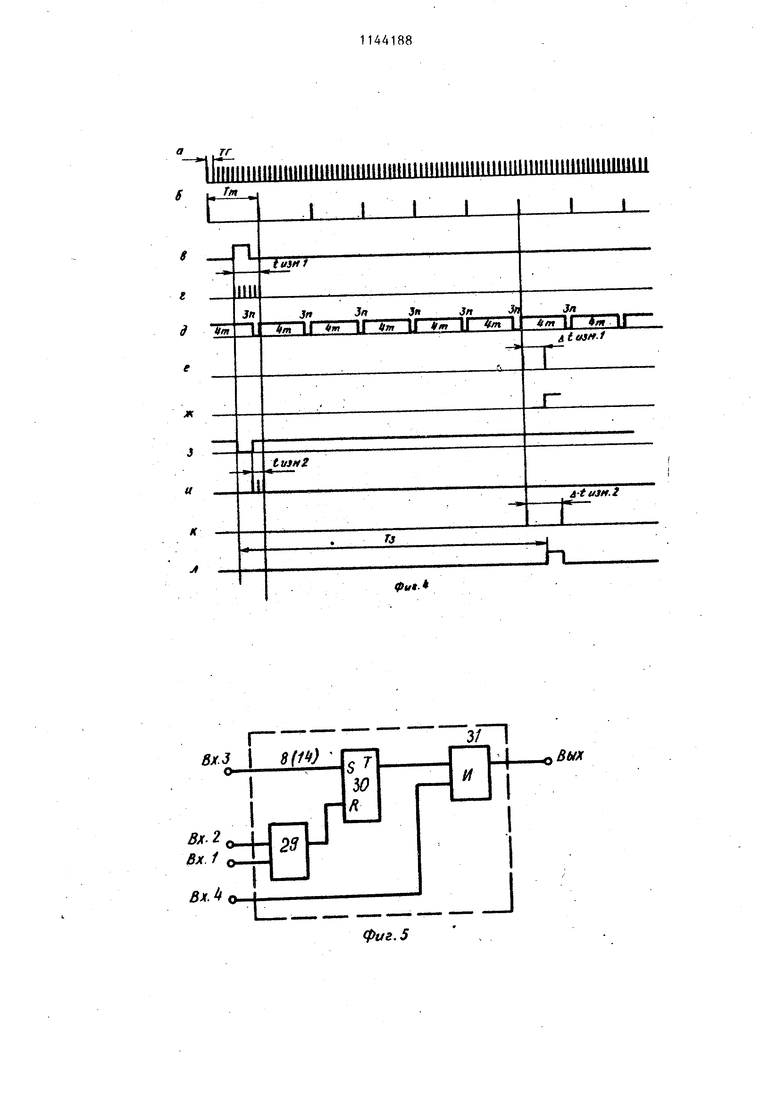

Информация, представленная числом а, из датчика 1 кода поступает на информационные входы первьк счетчиков 5 и 11 блоков 4 и 10 задержки фронтов, а информадщя, представленная числом k, - на вход уменьшаемого вычитателя 20 блока 18 формирования адреса. 7 Импульсы с выхода генератора 2 постоянно поступают на первые входы узлов 8 и 14 управления, на вход формирователя 3 тактовых ймПульсов и на входы счетчиков 6 и 12. С перво го выхода формирователя тактовые импульсы также постоянно поступают на вторые входы узлов 8 и 14 управления и на управляющий вход блока 18 форми рования адреса. С второго выхода формирователЯ 3 тактовых импульсов импульсы постоянно поступают на управляющие входы оперативных запоминающих устройств (ОЗУ) 7 и 13. Так как в начальньш момент в блок 18 формирования адреса информация не введена, то на его выходе код адреса отсутствует. До прихода входного импульса также отсутствуют сигналы на выходах счетчиков 5 и 11. После прихода входного импульса с выходов датчика 1 кода в счетчики 5 и 11 переписывается код, соответствуюпшй величине задержки Д . Импульсы генератора 2 после записи кода в счетчики начинают прстурать через узлы.В и 14 управления на вычитающие входы счетчиков 5 и 1 блоков 4 и 10 задержки фронтов. Счетчики 5 и 11 вычитают количест во импульсов из записанного в них числа, соответствующего Д , до появления первого после прихода входного сигнала импульса Запись, кот рый поступает с второго выхода формирователя 3 на управляющие входы ОЗУ 7 и 13. В момент перезаписи код из счетчиков 5 и 11 в ОЗУ 7 и 13 та товый импульс, поступающий из перво го вЬкода формирователя. 3 на вторые входы узлов В и 14 управления, прекращает прохождение импульсов ге-. нератора через узлы В и 14 управления, тем самым останавливается рабо та счетчиков 5 и 11. В ОЗУ записыва ется код, соответствующий времени ( & - t,jn), по адресу, который по ступает с выхода блока 18 формирова ния адреса. По этому же адрес-у, кот рый вьщает блок формирования адреса через время, равное kX, происходит чтение числа, соответствующего (А перезапись его во вторые счетчики 6 и 12 блоков задерж ки фронтов, на вычитающие входы кот рых постоянно поступают импульсы генератора. 88 Импульс переполнения счетчика 6 блока 4 задержки переднего фронта поступает через элемент ИЛИ 9 па единичный вход триггера 16, а импульс переполнения счетчика 12 блока 10 задержки заднего фронта - через элемент ИЛИ 15 на нулевой вход триггера 16 на выходе которого формируется задерживаемый импульс. На временной диаграмме (фиг. 4) приведены импульсы а с выхода генератора 2, импульсы 5 с первого выхода формирователя 3 тактовых импульсов, импульс в входной, импульсы 1 с выхода узла 8 управления, импульс д, с второго выхода формирователя 3 тактовых импульсов, импульс е переполнения счетчика 6(12), импульс с выхода триггера 16, импульс з с выхода элемента НЕ 17, импульсы и с выхода узла 14 управления, импульс k переполнения счетчика 12, импульс л выходной. Блок 18 формирования адреса (фиг. 2) работает следующим образом. По приходу входного импульса с выходов датчика 1 кода код, соответствующий числу k, поступает на ЕХОД уменьшаемого вычитателя 20, На вход суммирующего счетчика 19 поступают импульсы с первого выхода формирователя 3, которые одновременно поступают на управляюпщй вход элемента И 22 и через элемент НЕ 24 на управляюпщй вход элемента И 21. Работа-схемы блока формирования адреса поясняется таблицей фиг. 3. При отсутствии тактового импульса с первого выхода формирователя 3 происходит запись числа в ОЗУ 7 и 13 по первому адресу, далее, при поступлении первого тактового импульса происходит чтение числа, записанного по 5-му адресу. Например, при считывание каждого числа, записанного в ОЗУ по тому же адресу, по которому происходит чтение, производится через 5 тактов. При Т Т по приходу входного сигнала импульсы генератора поступают на входы счетчиков 5 и 11. В момент переполнения счетчиков, зависящий от формируемой задержки, на их выходах появляются импульсы переполнения, поступающие через элементы ИЛИ 9 и 15 на входы триггера 16. Эти же импульсы, поступающие на четвертые входы узлов 8 и 14 управления. прекращают прохождение импульсов генератора через узлы управления, что останавливает работу счетчиков 5 и 11. Особенностью предложенного устрой ства является то, что сохранение дли тельности задерживаемого импульса осуществляется путем введения блока задержки переднего фронта и блока задержки заднего фронта, которые одинаковы по своей структуре, а различие их работы состоит в том, что входной сигнал поступает на вход блока задержки заднего фронта через элемент НЕ, в то же время используется один блок формирования адреса, который служит одновременно для управления двумя блоками задержки фронтов, что позволяет сократить обо рудование. Введение элемента ИЛИ в блоки задержки фронтов позволяет производить задержку импульсных сигналов в широком диапазоне измерения Устройство задержки может быть в полнено на интегральных микросхемах средней и большой степени интеграци (регистры, счетчики, запоминающие устройства). При этом для осуществл

тЧ

11, 1. 1Ф,ДiLZj

аш. ния задержки цифрового сигнала, равной, например Т 1280 t , затраты по оборудованию на реализацию блоков задержки фронтов, узла управления, формирователятактовых импульсов в предлагаемом устройстве и известном примерно одинаковы. Для обеспечения требуемой величины задержки фронта сигнала в известном устройстве используется сдвигаюЕций регистр, максимальная длина которого соответствует числу ячеек памяти, в данном случае составляет 128 разрядов, для чего необходимо 16 корпусов 133 серии (схем восьмиразрядных регистров). Для обеспечения задержки обоих фронтов одновременно это составляет 32 корпуса, в то время как в предлагаемом устройстве для этой цели служит один блок формирования адреса, на реализацию которого требуется 11 корпусов схем средней степени интеграции той же серии. Из сравнения видно, что реализация предлагаемого изобретения позволяет при более высоких функциональных возможностях снизить затраты оборудования в блоке формиро вания адреса примерно в три раза по сравнению с известным устройством. Упр.вл О

L I-

2lf

f Фиг 2 От

22

1/ J/

/

/f adpec/fb/ff

входам ОЗУ

.З датчика кода тч а

г 9

зП

,Вых

фиг, 5 rr lliiiiiiiiiiiiituntUHiiiuiiintHiniiniiiiiiiiiiiiiiiiiiiiiiiiHiiiiiimuiii

%г.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Методы и схемы временной задержки импульсных сигналов | |||

| М., Советское радио, 1971, с | |||

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-03-07—Публикация

1982-10-12—Подача