Изобретение относится к вычислительной технике, в частности к уст- : ройствам сопряжения,и может быть использовано для ввода информации с предварительным вычислением систем булевых функций.

Цель изобретения - повьш1ение быстродействия ,

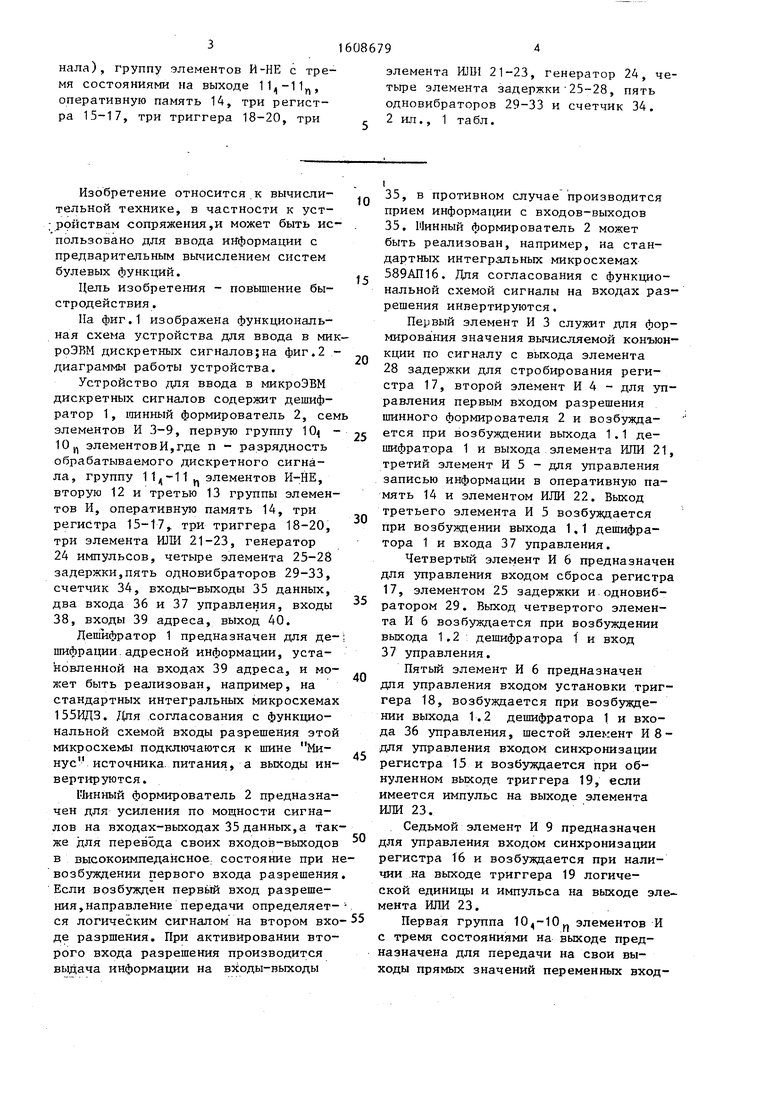

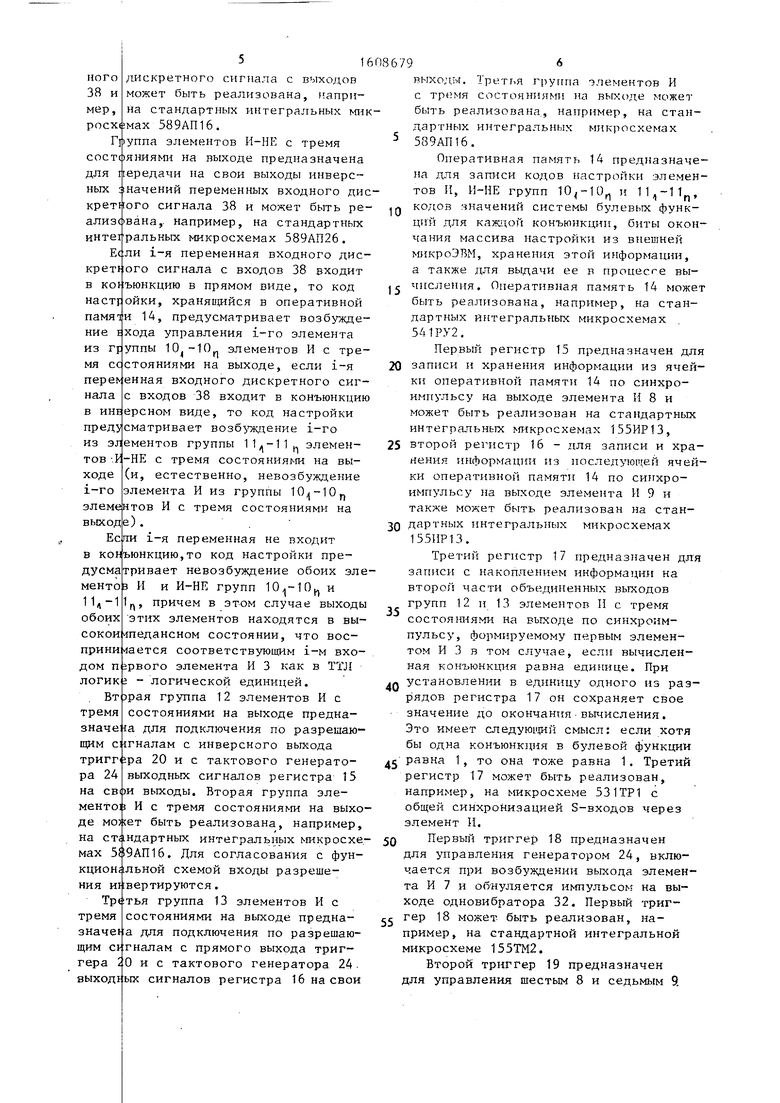

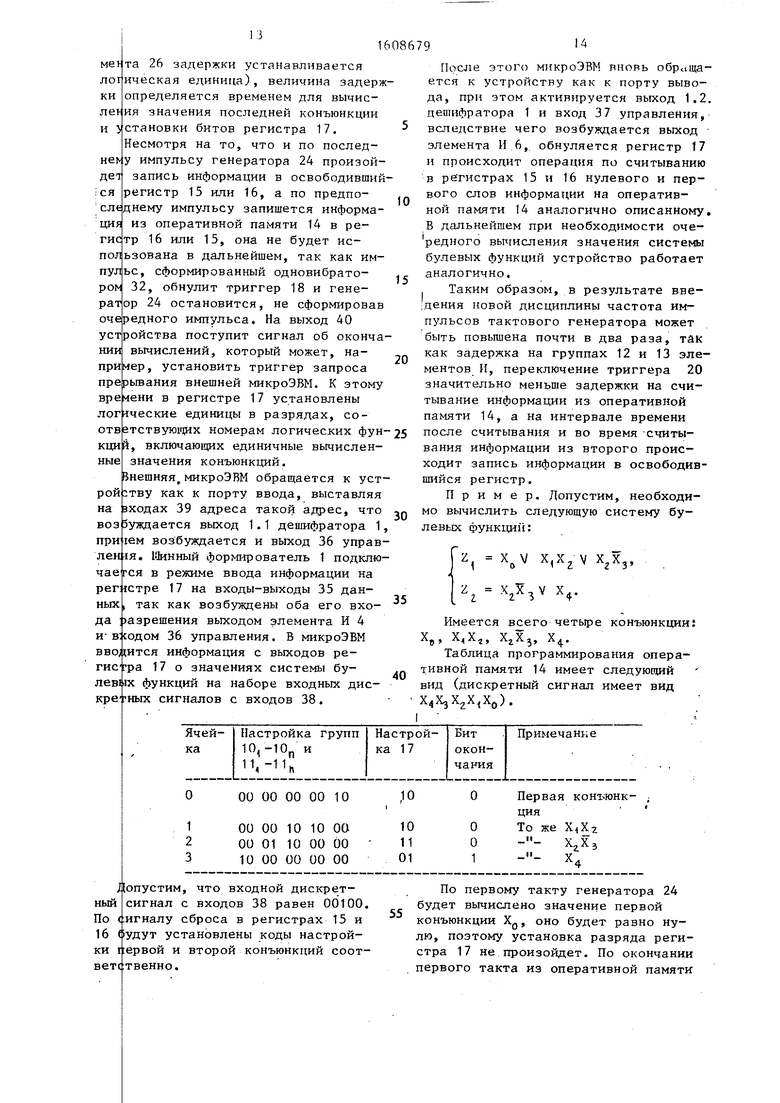

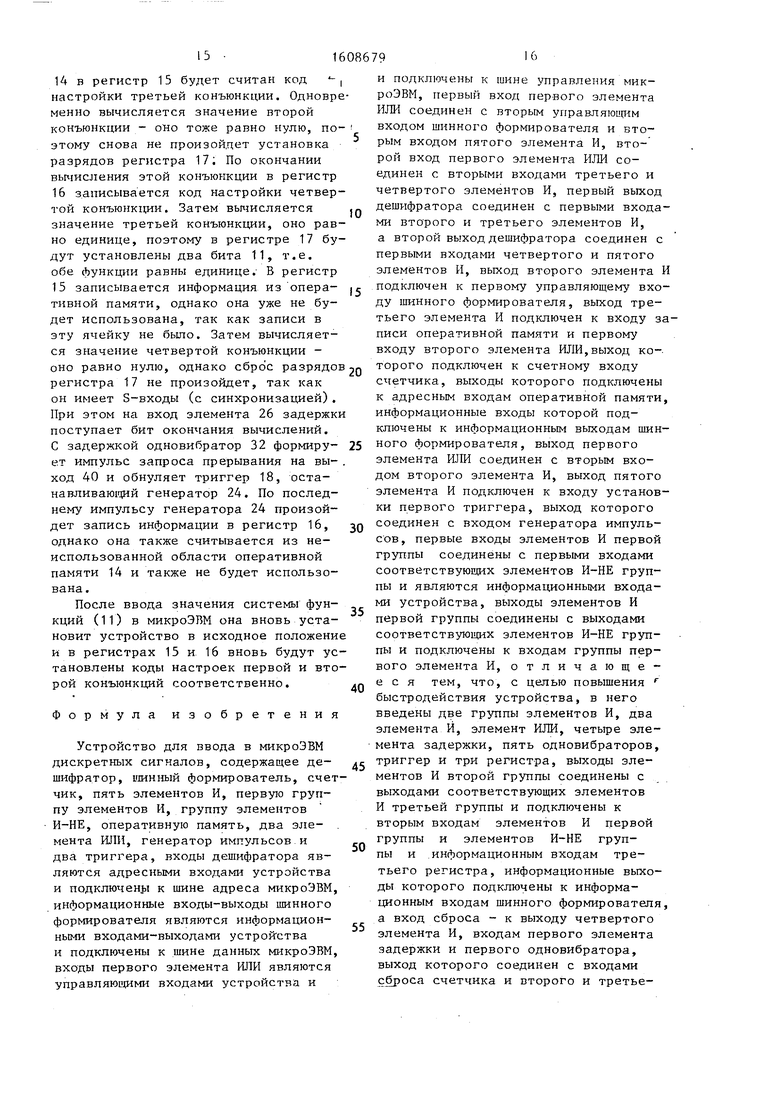

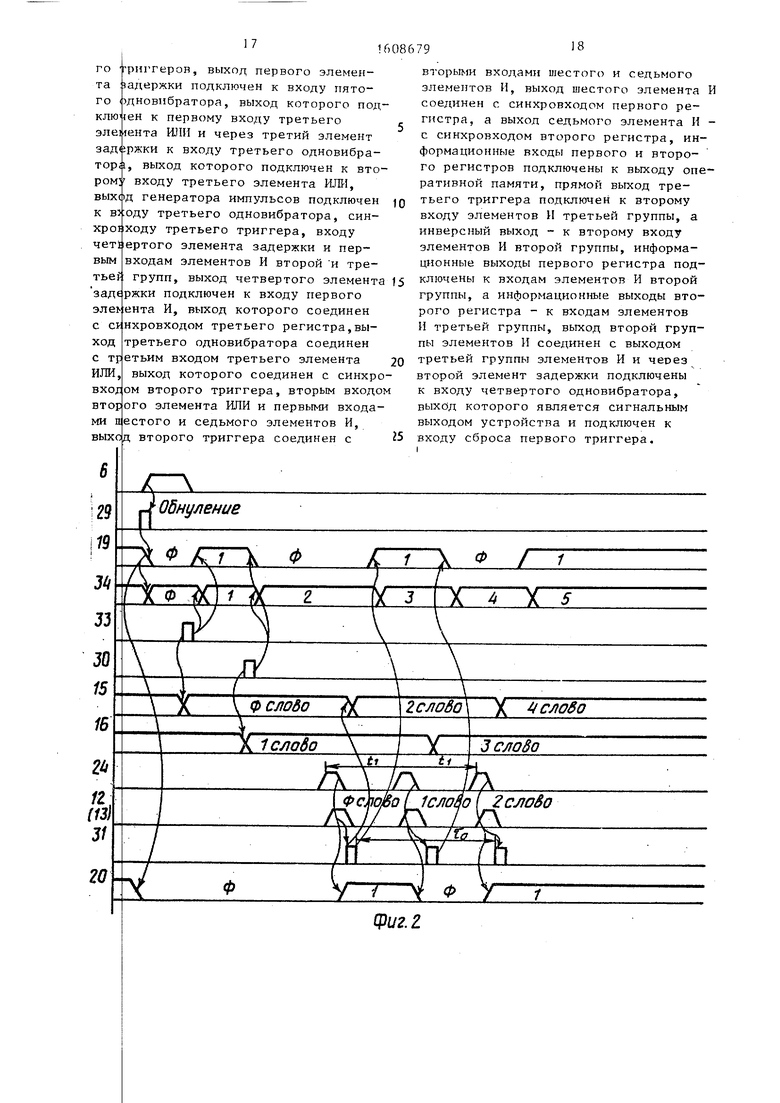

Па фиг.1 изображена функциональная схема устройства для ввода в мик роЭВМ дискретных сигналов;на фиг.2 - диаграммы работы устройства.

Устройство для ввода в микроЭВМ дискретных сигналов содержит дешифратор 1, шинный формирователь 2, сем элементов И 3-9, первую группу 0 10 элементов И, где п - разрядность обрабатываемого дискретного сигнала, группу 11д-11 элементов И-НЕ, вторую 12 и третью 13 группы элементов И, оперативную память 14, три регистра 15-17,. три триггера 18-20, три элемента ИЛИ 21-23, генератор 24 импульсов, четыре элемента 25-28 задержки,пять одновибраторов 29-33, счетчик 34, входы-выходы 35 данных, два входа 36 и 37 управления, входы 38, входы 39 адреса, выход 40.

Дешифратор 1 предназначен для дешифрации.адресной информации, установленной на входах 39 адреса, и мо- лсет быть реализован, например, на стандартных интегральных микросхемах 155ИДЗ, Для согласования с функциональной схемой входы разрешения этой микросхемы подключаются к шине Минус источника, питания, а выходы инвертируются.

Шинный формирователь 2 предназначен для усиления по мощности сигналов на входах-выходах 35 данных,а также для перевода своих входов-выходов в высокоимпедансное. состояние при нвозбуждении первого входа разрешения Если возбужден первый, вход разрешения, направление передачи определяется логическим сигналом на втором входе разршения. При активировании второго входа разрешения производится выдача информации на входы-выходы

10

5

0

5

0

5

0

5

0

5

35, в противном случае производится прием информации с входов-выходов 35. Шинный формирователь 2 может быть реализован, например, на стандартных интегральных микросхемах 589АП16. Для согласования с функциональной схемой сигналы на входах разрешения инвертируются.

Первый элемент И 3 служит для фор- мирова ния значения вычисляемой конъюнкции по сигналу с выхода элемента 28 задержки для стробирования регистра 17, второй элемент И 4 - для управления первым входом разрешения шинного формирователя 2 и возбуждается при возбуждении выхода 1.1 дешифратора 1 и выхода элемента ИЛИ 21, третий элемент И 5 - для управления записью информации в оперативную память 14 и элементом ИЛИ 22. Выход третьего элемента И 5 возбуддается при возбуждении выхода 1,1 дешифратора 1 и входа 37 управления.

Четвертый элемент И 6 предназначен для управления входом сброса регистра 17, элементом 25 задержки и.одновиб- ратором 29. Выход четвертого элемента И 6 возбуждается при возбуждении выхода 1.2 дешифратора 1 и вход 37 управления.

Пятый элемент И 6 предназначен дпя управления входом установки триггера 18, возбуждается при возбулзде- нии выхода 1.2 дешифратора 1 и входа 36 управления, шестой элемент И8- для управления входом синхронизации регистра 15 и возбуждается при обнуленном выходе триггера 19, если имеется импульс на выходе элемента ИЛИ 23.

Седьмой элемент И 9 предназначен для управления входом синхронизации регистра 16 и возбуждается при наличии на выходе триггера 19 логической единицы и импульса на выходе элемента ИЛИ 23.

Первая группа элементов И с тремя состояниями на выходе предназначена для передачи на свои выходы прямых значений переменных входного дискретного сигнала с выходов 38 и может быть реализована, например, на стандартных интегральных н589АП16.

уппа элементов И-НЕ с тремя яниями на выходе предназначен 1|1ередачи на свои выходы инверс 1Начений переменных входного д foro сигнала 38 и может быть р |вана,. например, на стандартны -ральных микросхемах 589АП26. Е4ли i-H переменная входного диого сигнала с входов 38 входит ко1 ъюнкцию в прямом виде, то код ойки, храняищйся в оперативной

14, предусматривает возбужде хода управления i-ro элемента

элементов И с тре ссстояниями на выходе, если i-я енная входного дискретного сиг с входов 38 входит в конъюнкци иНЕ(ерсном виде, то код настройки

возб ждение i-ro группы элемен- -НБ с тремя состояниями на вы- (и, естественно, невозбуждение элемента И из группы И с тремя состояниями на выходе)..

1-я переменная не входит

,то код настройки пре- невозбуждение обоих эл И и И-НЕ групп , и f,, причем в этом случае выход этих элементов находятся в высостоянии, что вос- 1ается соответствующим i-м вхо грвого элемента И 3 как в ТТЛ г - логической единицей. зрая группа 12 элементов И с состояниями на выходе предна- la для подключения по разрешаю 1гналам с инверсного выхода

20 и с тактового генерато- выходных сигналов регистра 15 )и выходы. Вторая группа эле- И с тремя состояниями на выхбыть реализована, например ндартных интегральных микросх 19АП16. Для согласования с фун- (льной схемой входы разреше- :вертируются.

;тья группа 13 элементов И с состояниями на выходе предна- а для подключения по разрешаю- гналам с прямого выхода триг- О и с тактового генератора 24 выход1 ых сигналов регистра 16 на свои

росх(мах Г

СОСТ(

для ных : крет( ализ интег Е(

крет в

настр памяти ние

из rplynoM мя

nepeN нала в

преду|сматривает из элементов тов -.V ходе i-ro элементов

ЕС пи в конъюнкцию, дусматривает ментор

1U-1

обоих

сокоиЦпедансном прини дом п логик Вт

тремя знача:

ЩИМ Ci

тригг фа ра 24 на CBI ментор де

на с т; мах 55 кционг кия И1 Тр

тремя значб

ЩИМ С1

гера

МО) сет

выходы. Третья груггпа элементов И с тремя состояниями }ia выходе может быть реализована., например, на стандартных интегральных микросхемах 589АП16.

Оперативная память 14 предназначена для записи кодов настройки элементов И, И-НЕ групп и , Q кодов значений системы булевых функций для кашкой конъюнкции, биты окончания массива настройки из внеБшей шткроЭВМ, хранения этой информации, а также для выдачи ее в процессе вы- и числения. Оперативная память 14 может быть реализована, например, на стандартных интегральных микросхемах 541РУ2.

Первый регистр 15 предназначен для 20 записи и хранения информации из ячейки оперативной памяти 14 по синхроимпульсу на выходе элемента И 8 и может быть реализован на стандартных интегральных М1кросхемах 155ИР13, 25 второй регистр 16 - для записи и хранения информации из последующей ячейки оперативной памяти 14 по синхроимпульсу на выходе элемента И 9 и также может быть реализован на стан- 30 дартных интегральных микросхемах 155ИР13.

Третий регистр 17 предназначен для записи с накоплением информации на второй части объединенных выходов групп 12 и 13 элементов И с тремя состояш-1ями на выходе по синхроимпульсу, формируемому первым элементом И 3 в том случае, если вычисленная конъюнкция равна единице. При установлении в единицу одного из разрядов регистра 17 он сохраняет свое - значение до окончашш вычисления . Это имеет следую111:ий смысл: если хотя бы одна конъюнкция в булевой функции 5 равна 1, то она тоже равна 1. Третий регистр 17 может быть реализован, например, на микросхеме 531ТР1 с общей синхронизацией S-входов хгерез элемент Н.

0 Первый триггер 18 предназначен для управления генератором 24, включается при возбуждении выхода элемента И 7 и об-нуляется импyльco на выходе одновибратора 32. Первый триг- J гер 18 может быть реализован, например, на стандартной интегральной микросхеме 155ТМ2.

Второй триггер 19 предназначен для управления шестым 8 и седьмым 9.

5

0

элементами И. Изменение состояния происходит по заднему фронту импульса на выходе элемента ИЛИ 23. Второй триггер 19 имеет счетный вход и может быть реализован, например, на стандартной интегральной микросхеме 1-55ТВ1.

Третий триггер 20 предназначен для управления группами 12 и 13 элементов с тремя состояниями на выходе Он также имеет счетный вход и может быть реализован, например, на стандартной интегральной микросхеме 155ТВ1.,

Первый элемент ИЛИ 21 предназначен для управления элементом И 4 при наличии активного уровня сигнала на одном из двух управляющих входах 36 и 37, второй элемент ИЛИ 22 - для управления счеттатм входом счетчика 34 по сигналам либо с выхода элемент И 5, либо элемента ИЛИ 23, третий элемент ИЛИ 23 - для управления элементами И 8 и 9 по сигналам с выходов одновибраторов 33, 30 или 31.

Генератор 24 предназначен для синхронизации работы устройства в режиме вычислений и может быть реализован, например, на трех элементах И-НЕ, резисторе и конденсаторе.

Первый элемент 25 задержки предназначен для задержки фронта импульса на выходе элемента И 6 на интервал времени, необходимый для надежного обнуления триггера 19 и счетчика 34, второй элемент 26 задержки - для задержки фронта импульса окончания вычислений на соответствующем разряде объединенных выходов групп 12 и 13 элементов И с тремя состояниями на выходе. Величина интервала определяется необходимостью надежного вычисления последней конъюнкции и записи информации в регистр 17.

Третий элемент 27 задержки предназначен для задержки фронта импульса на выходе одновибратора 33 на временной интервал, необходимый для надежной записи информадаи в регистр 15 и изменения состояния счетчика 34

Четвертый элемент 28 задержки предназначен для задержки фронта импульса на выходе генератора 24 на временной интервал, необходимый для надежного формирования сигналов на выходах групп 10(-11 элементов И и элементов И-НЕ перед строби- рованием элемента И 3.

0

5

0

5

0

5

0

5

0

5

Первый одновибратор 29 служит для формирования по переднему фронту импульса на выходе элемента И 6 короткого импульса обнуления триггеров 19 и 20 и счетчика 34. Он может быть реализован, например, на стандартной интегральной микросхеме 155АГ1, резисторе и конденсаторе.

Второй одновибратор 30 необходим для формирования второго импульса записи по сбросу в регистр 16 после формирования первого импульса одно- вибратором 33. Он также может быть реализован на стандартной интегральной микросхеме 155АГ1.

Третий одновибратор 31 предназначен для формирования импульса записи в освободившийся регистр из регистров 15 и 16 по заднему фронту тактового импульса генератора 24. Может быть реализован, например, на стандартной интегральной микросхеме 155АГ1.

Четвертый одновибратор 32 предназначен для формирования импульса сброса триггера 18 для окончания вычислений и сигнала на управляющий выход 40 при появлении на соответствующем выходе объединенных выходов групп 12 и 13 элементов И с тремя состояниями на выходе единичного бита окончания вычислений (помечающего лоследнюю конъюнкцию). Может быть реализован на микросхеме 155АГ1.

Пятый одновибратор 33 служит рля формирования первого импульса Записи по сбросу в регистр 15. Он ожет быть реализован, например, на стандартной интегральной микросхеме 155АГ1.

Счетчик 34 предназначен для адре- сации оперативной памяти 14 по импульсам с выхода элемента ИЛИ 22 и может быть реализован, например, на стандартных интегральных микросхемах 155ИЕ7.

Входы-выходы 35 данных предназначены для подключения шины данных стандартного параллельного интерфейса микроэвм.

,Первый вход 36 управления предназначен для подключения разряда ввода информации шины управления стандартного параллельного интерфейса микро- ЭВМ, второй вход 37 управления - для подключения разряда вывода информации шины управления стандартного параллельного интерфейса микэЭВМ, входы 38 - для подключения содного дискретного сигнала, входы адреса - для подключения шины еса стандартного параллельного 1терфейса микроЭВМ, вход 40 - для )рмирования импульса окончания вы- .ления, например, на линии запро- прерывания стандартного параллель )го интерфейса микроЭВМ. Устройство работает следую1цим образом,

вывода.

ботает ш:я Э вь

Р выход

ЕС

ар

Э1

рзет фс

рг 36 2

В режиме настройки устройство рааналогично известному. Внеш- по отношению к устройству микро iM обраршется к нему как к порту , выставляя на входах 39 ад- са такой код, что возб ждается

1.1 дешифратора 1, при этом збужден вход 37 управления, поэто тивируется выход элемента ИЛИ 21 элемента И 4, выход которого активипервый вход разрешения шинного фсрмирователя 2. По второму входу

зрешения (так как вход управления

не возбужден) шинный формировате переведен в режим выдачи информации с входов-выходов 35 данных на информационные входы оперативной па|мяти 14..

Кроме того, активируется выход элемента И 5, выход которого возбуждает вход записи оперативной памяти 14, и выданная из-микроЭВМ по входа вьходам информация записывается в нлевую ячейку. Счетчик 34 обнулен в хсциом положении по цепям (не показан) . Задним фронтом импульса на выходе элемента И 5 по окончании записи в нулевую ячейку через элемент ИЛИ 22 изменяется состояние счетчика 34, который адресует очередную (первую) ячейку оперативной памяти 14. В дальнейшем устройство работает аналогично. В оперативную память 14 записывается информация, содержащая тр1 поля: первое - коды настройки , элементов И и группы 11,-11 f, элементов И-НЕ .Эти коды аналогичны известным и кодируют конъюн стивные термы (или конъюнкции) зада шой системы булевых функций. Вто- ро 1 поле содержит единицы в разряда::, соответствующих номерам булевы с функций,содержащих данную конъюн . Третье поле (один бит) уста- на;шипается равным единице, если соответствующая конъюнкция - послед

15

jQ

25

OQ

35

0

5

0

5

няя. в осталылгх случаях этот бит равен нулю,

В режиме вычислений после записи информации в оперативную память 14 внеишяя микроэвм обращается к устройству как к цорту вывода, устанавливая на адресных входах 39 такой код, что возбуждается выход 1,2 дешифратора 1. Так как при этом возбужден вход 37 управления, то активируется выход элемента И 6. Обнуляется регистр 17, срабатывает одно- вибратор 29, формируя короткий импульс обнуления триггеров 19, 20 и счетчика 34. С задержкой, обусловленной элементом 25 задержки, и предназначенной для формирования временного интервала надежного обнуления триггера 19 и счетчика 34, формируется импульс одновибратором 33, передним фронтом которого через элемент ИЛИ 23 в регистр 15 записывается информация из нулевой ячейки оперативной памяти 14. Элемент И 8 подготовлен нулевым сигналом на выходе триггера 19. Задним фронтом импульс на выходе одновибратора 33 через элемент ИЛИ 23 изменяет состояние триггера 19 (устанавливается в состояние логической единицы), тем самым подготавливая элемент И 9 к строби- рованию регистра 18. Кроме того, происходит изменение состояния счетчика 34 через элемент ИЛИ 22, который адресует очередную - первую (после нулевой) ячейку оперативной памяти 14.

Все эти процессы происходят в интервале времени, меньшем величины задержки элемента 27 задержки. Поэтому по срабатывании одновибратора 30 формируется второй импульс записи, передним фронтом которого происходит запись информации из первой ячейки оперативной памяти 14 в регистр 16 через элемент ИЛИ 23 и элемент И 9. Задним фронтом этого импульса изменяется состояние счетчика 34 через элемент ИЛИ 22 и триггер 19. Таким образом, счетчик 34 адресует очередную - вторую (после нулевой и первой) ячейку оперативной памяти 14, а триггер 19 вновь обнуляется, тем самым подготавливая запись информации в регистр 15.

Устройство готово к вычислениям. Внешняя микроэвм, обращаясь к устройству как к порту ввода, адресует его по адресным входам 39, при этом во.збуждается выход 1.2 дешифратора. Так как активирован вход 36 управления, то возбуждается вькод элемента И 7. При возбутвдении выхода 1.2 дешифра- тора 1 как при возбуждении входа 36 управления, так и входа 37 управления шинный формирователь 1 не подключается к входам-выходам 35 данных и его входы-выходы находятся в высо- коимпедансном состоянии (первый вход разрешения шинного формирователя 1 не активирован). Следовательно, устанавливается триггер 18, обнуленный в исходном положении по цепям, не указанньш на фиг.1. Выход триггера 18 запускает генератор 24. При этом на группы элементов И и элементов И-НЕ, а также на информационные входы регистра 17 считывается информация из регистра 15 через группу 12 элементов И с высоким импедансом на выходе, так как ее второй вход разрешения активирован инверсным выходом обнулен- ного триггера 20. С задержкой, определяемой элементом 28 задержки и необходимой для окончания переходных процессов в группах lOi-lOn элементов И и 11,-11 элементов И-НЕ с тремя состояниями на выходе, активируется (п+1)-й вход элемента И 3.

При этом происходит обработка дискретного сигнала с входов 38 аналогично известному устройству. Если вычислительньп конъюнктивный терм покрывает (имплицирует) входной дискретный сигнал с входом 38, то выход элемента И 3 возбуждается. В этом случае выходы всех пар элемен- тов И и И-НЕ групп и 11д-11п активированы аналогично известному устройству. Передним фронтом импульса на выходе элемента И 3 в регистре 17 устанавливаются биты,соответствую щие единичным разрядам части информации на объединенных выходах группы 12 и 13 элементов И с тремя состояниями на выходе.

Таким образом, происходит формирование значений функций, включающие вычисленный-единичный конъюнктивный терм. Если конъюнктивный терм равен нулю, то установления разрядов (по входам установки 5) регистра 17 не происходит, так-как не возбуждается выход элемента ИЗ. Задним фронтом импульса генератора 24 изменяется

состояние триггера 20 (это происходит по окончании переходных процессов вычисления нулевого конъюнктивного терма), выход которого возбуждается и активирует второй вход разрешения группы 13 элементов И с тремя состояниями на выходе. Следующим импульсом генератора 24 аналогично описанному считывается информация из регистра 16 (1-е слово на фиг.2). Если соответствующая конъюнкция окажется равна единице, то в регистре 17 установятся биты, соответствующие номерам булевых функций, включающих эту конъюнкцию.

По заднему фронту предыдущего импульса, кроме того, срабатывает одновибратор 31, который формирует импульс записи, через элемент ИЛИ 23, записывающий информацию из второй ячейки оперативной памяти 14 в регистр 15 через элемент И 8. Задний фронт этого импульса изменяет состояние счетчика 34 через элемент ИЛИ 22 и триггер 19, выход которого подготавливает запись информации в регистр 16. Все это происходит после вычисления значения первого конъюнктивного терма. Аналогично описанному задним фронтом второго импульса генератора 24 изменяется состояние триггера 20,подготавливающего чтение из регистра 15, а также формируется импульс записи одновибратором 31 для записи информации из третьей яче ки памяти в освободившийся регистр 16 I Третьим импульсом генератора 24 . на объединенные выходы групп 12 и 13 элементов И с высоким импедансом на выходе выдается второе слово информации, находящееся в регистре 15, организуется установка битов в регистре 17 (если соответствующая . конъюнкция равна 1). Задним фронтом этого импульса изменяется состояние триггера 20, который готовит считывание из регистра 16, формируется импульс одновибратором 31,по которо- му записывается информация в освободившийся регистр 15, а задним фронтом этого импульса изменяется состояние триггера 19 и счетчика 34. В дальнейшем устройство работает аналогично .

В том случае, если на объединенны выходы групп 12 и 13 элементов И считана информация о последнем конъюнктивном терме (при этом на входе элемеь

логическая единица), величина задержки определяется временем для вычис- значения последней конъюнкции и установки битов регистра 17.

Несмотря на то, что и по послед- неку импульсу генератора 24 произойдет запись информации в освободивший- ;ся регистр 15 или 16, а по предпо- |следнему импульсу запишется информация из оперативной памяти 14 в регистр 16 или 15, она не будет использована в дальнейшем, так как импульс, сформированный одновибрато- ром 32, обнулит триггер 18 и генератор 24 остановится, не сформировав очередного импульса. На выход 40 уст ройства поступит сигнал об окончата 26 задержки устанавливается

нии

вычислений, который может, например, установить триггер запроса прерьгоания внешней микроЭВМ. К этому времени в регистре 17 установлены логические единицы в разрядах, совтствую1чих номерам логических фунотв

кциА, включающих единичные вычисленные значения конъюнкций.

| нeшняя, микроэвм обращается к устрой :тву как к порту ввода, выставляя на зходах 39 адреса такой адрес, что воз 5уждается выход 1.1 дешифратора 1, при 1ем возбуждается и выход 36 управ- лен1я, 111ИННЫЙ формирователь 1 подключается в режиме ввода информации на репстре 17 на входы-выходы 35 данных , так как возбуждены оба его входа :)азрешения выходом элемента И 4 и-в: сод ом 36 управления. В микроЭВМ вводится информация с выходов ре- гис фа 17 о значениях системы булев ix функций на наборе входных дис- сигналов с входов 38.

0

5

0

5

0

ricicJie этого микроэвм вновь обращается к устройству как к порту вывода, при этом активируется выход 1.2. дешифратора 1 и вход 37 управления, вследствие чего возбуждается выход элемента И 6, обнуляется регистр 17 и происходит операция по считыванию в регистрах 15 и 16 нулевого и первого слов информации на оперативной памяти 14 аналогично описанному, В дальнейшем при необходимости оче- редного вычисления значения системы булевых функций устройство работает аналогично.

Таким образом, в результате вве- ;дения новой дисциплины частота импульсов тактового генератора может быть повьпиена почти в два раза, так как задержка на группах 12 и 13 элементов И, переключение триггера 20 значительно меньше задержки на считывание информации из оперативной памяти 14, а на интервале времени после считывания и во время -считывания информации из второго происходит запись информации в освободившийся регистр.

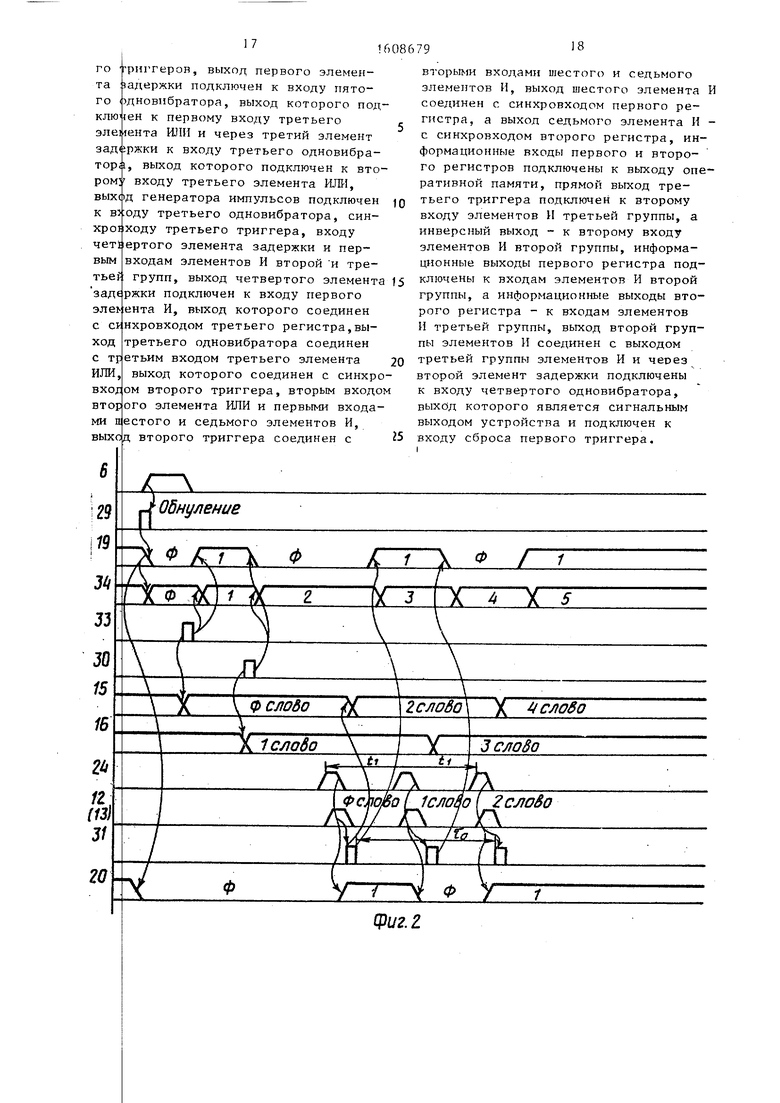

Пример. Допустим, необходимо вычислить следующую систему булевых функгш :

35

Имеется всего четыре конъюнкции

X

,

д, 14- ч

Таблица программирования оперативной памяти 14 имеет следующий вид (дискретный сигнал имеет вид )

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

Изобретение относится к вычислительной технике и может быть использовано для ввода информации с предварительным вычислением булевых функций. Целью изобретения является повышение быстродействия устройства. Устройство содержит дешифратор 1, шинный формирователь 2, с первого по седьмой элементы И 3 - 9, три группы элементов И с тремя состояниями на выходе 101 - 10N, 12, 13 (N - разрядность обрабатываемого дискретного сигнала), группу элементов И-НЕ с тремя состояниями на выходе 111 - 11N, оперативную память 14, три регистра 15 - 17, три триггера 18 - 20, три элемента ИЛИ 21 - 23, генератор 24, четыре элемента задержки 25 - 28, пять одновибраторов 29 - 33 и счетчик 34. 2 ил.

Допустим, что входной дискретный сигнал с входов 38 равен 00100. По (.игналу сброса в регистрах 15 и 16 Оудут установлены коды настройки 1:ервой и второй конъюнкций соответственно.

По первому такту генератора 24 будет вычислено значение первой конъюнкции Хд, оно будет равно нулю, поэтому установка разряда регистра 17 не произойдет. По окончании первого такта из оперативной памяти

14в регистр 15 будет считан код настройки третьей конъюнкции. Одновременно вычисляется значение второй конъюнкции - оно тоже равно нулю, поэтому снова не произойдет установка разрядов регистра 17; По окончании вьтисления этой конъюнкции в регистр 16 записывается код настройки четвертой конъюнкции. Затем вьмисляется значение третьей конъюнкции, оно равно единице, поэтому в регистре 17 будут установлены два бита 11, т.е.

обе функции равны единице. В регистр

15записывается информация из опера- тивной памяти, однако она уже не будет использована, так как записи в

эту ячейку не бьшо. Затем вычисляется значение четвертой конъюнкции - оно равно нулю, однако сбро с разрядов регистра 17 не произойдет, так как он имеет S-входы (с синхронизацией). При этом на вход элемента 26 задержки поступает бит окончания вычислений. С задержкой одновибратор 32 формиру- ет импульс запроса прерывания на вы- ход 40 и обнуляет триггер 18, оста- навливаю1чий генератор 24. По последнему импульсу генератора 24 произойдет запись информации в регистр 16, однако она также считывается из неиспользованной области оперативной памяти 14 и также не будет использована.

После ввода значения системы функций (11) в микроэвм она вновь установит устройство в исходное положение и в регистрах 15 и 16 вновь будут установлены коды настроек первой и второй конъюнкций соответственно,

Формула изобретения

Устройство для ввода в микроЭВМ дискретных сигналов, содержащее де- шифратор, ишнный формирователь, счетчик, пять элементов И, первую группу элементов И, группу элементов И-НЕ, оперативную память, два эле- .

мента ШШ, генератор импульсов и два триггера, входы дешифратора являются адресными входами устройства и подключены к шине адреса микроЭВМ, информационные входы-выходы шинного формирователя являются информационными входами-выходами устройства и подключены к шине данных микроЭВМ, входы первого элемента ИЛИ являются управляюидими входами устройства и

п

г

Q 5 о

Q

5

0

5

и подключены к шине управления микроЭВМ, первый вход первого элемента ИЛИ соединен с вторым управляюиа м входом шинного формирователя и вторым входом пятого элемента И, вто- рой вход первого элемента ИЛИ соединен с вторыми входами третьего и четвертого элементов И, первый выход дешифратора соединен с первыми входами вто рого и третьего элементов И, а второй выход дешифратора соединен с первыми входами четвертого и пятого элементов И, выход второго элемента И подключен к первому управляющему входу шинного формирователя, выход третьего элемента И подключен к входу записи оперативной памяти и первому входу второго элемента ИЛИ,выход ко-, торого подключен к счетному входу счетчика, выходы которого подключены к адресным входам оперативной памяти, информационные входы которой подключены к информационным выходам шинного формирователя, выход первого элемента ШШ соединен с вторым входом второго элемента И, выход пятого элемента И подключен к входу установки первого триггера, выход которого соединен с входом генератора импульсов, первые входы элементов И первой группы соединены с первыми входами соответствующих элементов И-НЕ группы и являются информационными входами устройства, выходы элементов И первой группы соединены с выходами соответствующих элементов И-НЕ группы и подключены к входам группы первого элемеьгта И, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены две группы элементов И, два элемента II, элемент ИЛИ, четыре элемента задержки, пять одновибраторов, триггер и три регистра, выходы элементов И второй группы соединены с выходами соответствующих элементов И третьей группы и подключены к вторым входам элементов И первой группы и элементов И-НЕ группы и информационным входам третьего регистра, информационные выходы которого подключены к информационным входам шинного формирователя, а вход сброса - к выходу четвертого элемента И, входам первого элемента задержки и первого одновибратора, выход которого соединен с входами с&роса счетчика и второго и третьегота го

КЛЮ

элемента

тора ром;

ВЫХ(

к в:

xpoi

чет

вым

тье

риггеров, выход первого элемен- шдержки подключен к входу пято- щновибратора, выход которого под leH к первому входу третьего

ИЛИ и через третий элемент задержки к входу третьего одновибравыход которого подключен к вто входу третьего элемента ИЛИ, |д генератора импульсов подключен :оду третьего одновибратора, син- 1ХОДУ третьего триггера, входу ертого элемента задержки и пер- входам элементов И второй и трегрупп, выход четвертого элемента задержки подключен к входу первого И, выход которого соединен с ci-нхровходом третьего регистра,выход третьего одновибратора соединен с третьим входом третьего элемента ИЛИ, выход которого соединен с синхро BXOjioM второго триггера, вторым входо второго элемента ИЛИ и первыми входами пестого и седьмого элементов И, выход второго триггера соединен с

20

вторыми входами шестого и седьмого элементов Н, выход шестого элемента соединен с синхровходом первого регистра, а выход седьмого элемента И с синхровходом второго регистра, информационные входы первого и второ- го регистров подключены к выходу оперативной памяти, прямой выход третьего триггера подключен к второму входу элементов И третьей группы, а инверсный выход - к второму входу элементов И второй группы, информационные выходы первого регистра подключены к входам элементов И второй группы, а информационные выходы второго регистра - к входам элементов И третьей группы, выход второй группы элементов И соединен с выходом третьей группы элементов И и через второй элемент задержки подключены к входу четвертого одновибратора, выход которого является сигнальным выходом устройства и подключен к входу сброса первого триггера.

| РАЗЪЕДИНИТЕЛЬ ДЛЯ ЭЛЕКТРИЧЕСКИХ ВОЗДУШНЫХ ЛИНИЙ ВЫСОКОГО НАПРЯЖЕНИЯ | 1927 |

|

SU13143A1 |

| Бюл | |||

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| свидетельство СССР кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-23—Публикация

1988-12-30—Подача