выми входами второй памяти и арифметического блока, второй вход которого соединен с выходом второй памяти, второй вход которой соединен с выходом третьего регистра, отличающаяся тем, что, с целью повышения гибкости и коэффициента использования оборудования, в нее введены группа сумматоров, третья память, два сумматора, дополнительны .регистр кода условий, семь регистров два узла загрузки, шесть шифраторов, группа триггеров, выходы регистров группы соединены с первыми входами соответствующих сумматоров группы, вторые входы которых соединены с выходом блока формирования ад раса, первым входом первого шифратора, третьими входами процессоров, третьим входом второго сумматора, и первыми входами третьего и четвертого сумматоров, второй вход последнего через восьмой регистр соединен с шиной обмена, соединенной таже с вторым входом третьего сумматора, входом девятого регистра и первым входом дополнительного регистра кода условий, выход ч которого через десятый регистр соединен с первым входом седьмого регистра,второй вход которого соединен с выходом третьего сумматора и входом одиннадцатого регистра, выход которого сое динен с первым входом третьей памяти, второй вход которой через двенадцатый регистр соединен с выходом четвертого сумматора, выход третьей памяти соединен с третьим входом третьего сумматора, выход девятого ргистра соединен с вторым входом первого шифратора, выход которого соединен с третьим -входом блока формирования адреса, четвертым входом каждого процессора и вторым входом буферной памяти, третий вход которой соединен с выходом второго шифратора, первые входы которого, тринадцатого регистра, третьего и четвертого шифраторов, выход пятого шифратора, первые входы и выход каждого узла загрузки и вход четырнадцатого регистра соединены с шиной управления, первый выход тринадцатого регистра соединен с вторыми входами второго и третьего шифраторов и регистров кода условий, второй выход тринадцатого регистра соединен с третьими входами второго и третьего шифраторов, третий выход тринадцатого

регистра соединен с пятым входом каж дого процессора, вторым входом четвертого шифратора и первым входом пятого шифратора, четвертый выход тринадцатого регистра соединен с четвертыми входами второго и третьего шифраторов, пятый выход тринадцатого регистра соединен с третьим входом первого шифратора и шестым входом каждого процессора, шестой выход тринадцатого регистра соединен с пятыми входами второго и третьего шифраторов, второй выход первого узла загрузки соединен с шестым входом второго шифратора и вторым входом второго узла загрузки, второй выход которого .соединен с шестым входом тр%тьего шифратора и вторым входом первогоузла загрузKtf, третьи выходы первого и второго узлов загрузки соединены соответственно с вторым и третьим входами тринадцатого регистра, выход третьего шифратора соединен с седьмым входом каждого процессора, восьмой вход которого через шестой шифратор соединен с выходом четырнадцатого регистра,второй выход и четвертый вход буферной памяти соединены соответственно с вторым входом пятого шифратора и выходом четвертого шифратора, четвертый вход микропрограммного устройства управления через соответствующий триггер группы соединен с выходом каждого процессора, выходы сумматоров группы соединены с четвертым входом блока формирования .адреса и девятым входом каждого процессора, а в каждый процессор введены буферная память, два шифратора, второй триггер, три регистра, коммутатор, причем,первый выход операционного блока соединен с третьим входом арифметического блока и первым входом первого шифратора, выход которого соединен с первыми входами коммутатора буферной памяти и входом четвертого регистра, выход которого соединен с выходом процессора, входом Bjoporo триггера, входом, первого регистра и четвертым входом операционного блока, пятый, вход которого соединен с восьмым входом процессора, девятый вход К(рторого соединен с шестым входом операционного блока, четвертым Входом арифметического блока и первым входом третьего регистра, второй вход которого соединен с третьим входом процессора, седьмым входом операционного блока и пятым входом арифметического блока, шестой вход которого соединен с первым вхдом второго триггера, второй вход которого соединен с третьим входом третьего регистра, шестой вход процессора соединен с вторым входом коммутатора, выход которого через пятый регистр соединен со своим третьим входом и входом первого шифратора, третий вход которого соединен с выходом первого триггера,четвертый вход процессора через шестой регистр соединен с четвертым входом коммутатора, пятый вход процессора соединен с входом второго шифратора, соединенного двусторонними связями с шиной управления, информационной шиной и буферной памятью, второй вход которой соединен с седьмым входом процессора, память и буферная память соединены двусторонней связью между собой.

2. Система по п. Т,отличают а я с я тем, что узел загрузки содержит счетчик, коммутатор,шифратор и регистр, причем, первый и второй выходы счетчика соединены с первым и вторым выходами узла, первый вход которого через последовательно соединенные регистр и шифратор соединены с первымвходом коммутатора второй вход которого является вторым входом узла, а третий вход соединен со вторым входом счетчика, выход коммутатора соединен с входом счетчика и третьим выходом узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Процессор ввода-вывода | 1980 |

|

SU934465A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

1

Изобретение относится к области вычислительной техники и может быть использовано в автоматизированных ситемах реального времени.

Известна многопроцессорная вычислительная система, содержащая однотипные процессоры, регистры,приоритетное устройство, регистр связей и блок команд l..

Недостатком этой вычислительной системы являются низкие эффективность и гибкость работы системы, отсутствие совмещения Арифметических и индексных операций, а также наличи одной общей памяти для операндов,адресов и постоянных величин.

Наиболее близкой к изобретению является многопроцессорная вычислительная система, содержащая про- цессоры, соединенные с шиной обмена, информационной шиной, шиной управления, а также между собой двусторонними связями, микропрограммное устройство управления, регистры, дешифратор, блок формирования адреса, регистр кода условий, арифметический блок и сумматорь 21 .

Недостатком известного технического решения является отсутствие независимого формирования адресов в процессорах из-за наличия одной общей памяти для хранения адресов, индексов и операндов, отсутствие

сверхоперативного запоминающего устройства в процессорах .Целью изобретения является повышение гибкости и коэффициента использования оборудования.

Цель достигается .тем, что в многопроцессорную вычислительную систему , содержащую процессоры, соединенные с шиной обмена, информационной шиной, шиной управления, а также между собой двусторонними связями, микропрограммное устройство управления, первый выход которого соединен с первыми входами регистра

кода условий и регистров группы,

вторые входы которых соединены с вторым выходом микропрограммного устройства управления, входами первых регистра, дешифратора, с первым входом арифметического блока и через второй регистр с первым входом первого сумматора,, выход которого соединен с первым входом блока формирования адреса, второй вход которого

.соединен с первым выходом третьего регистра, второй вход которого соединен с первым входом первой памяти, выход которого соединен с первым входом второго сумматора, выход

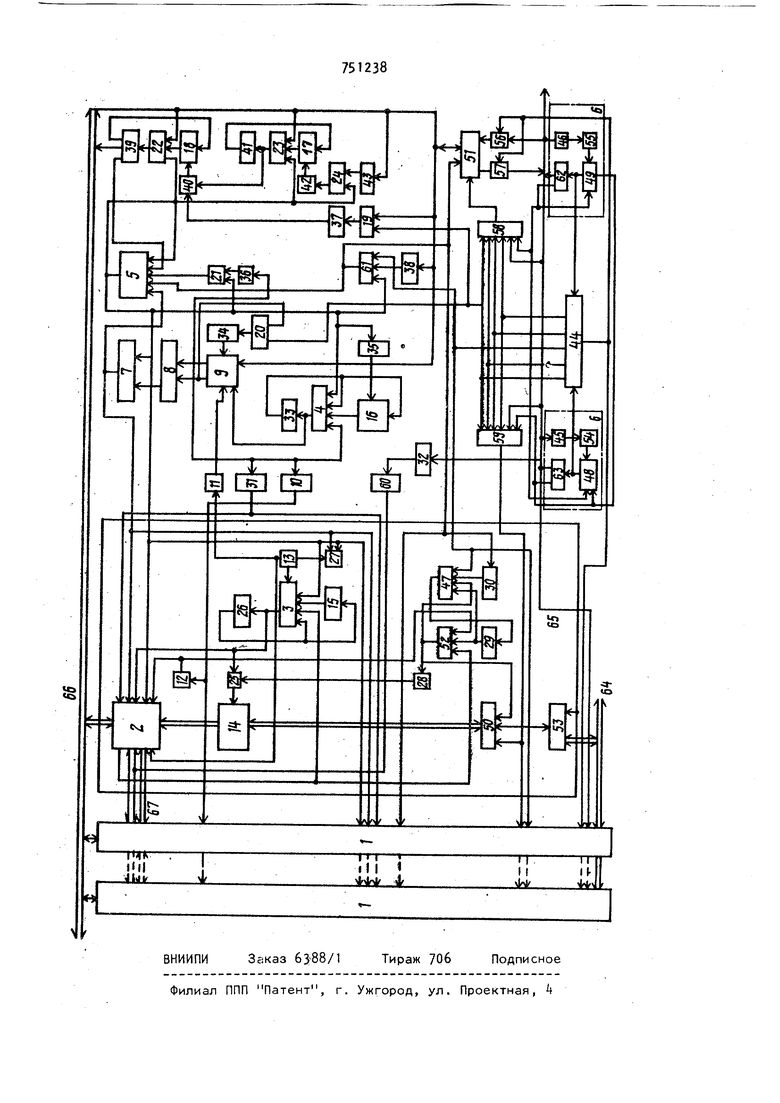

которого соединен с входом третьего регистра, выход арифметического блока соединен с первым входом микропрограммного устройства управления и чеiрез четвертый регистр со своим вторым входом и первым входом второй памяти, выход блока формирования адреса соединен с третьим входом арифметического блока, вторим входо первого сумматора,и через пятый регистр с вторым входом второй памяти, выход которой соединен с четвертым входом арифметического блока выход регистра код условий через шестой регистр соединен с вторым входом микропрограммного уст-, ройства управления, третий вход которого, вторёй вход второго суммато ра, первый вход и выход буферной па мяти и третий выход третьего регист ра соединен с шиной обмена, выходы первых дешифратора и регистра соеди ны с первым и вторым входами про- цессоров, второй вход первой памяти соединен с выходом седьмого регистра, а каждый процессор содержит операционный блок, соединенный двусторонними связями с шмной обмена и первой памятью, вход которой через первый регистр соединен с выходом арифметического блока, входом второго регистра и первым входом операционного блока, второй вход которого соединен с вторым входом процессора, первый вход которого соединен с первым входом триггера, выход которого соединен с третьим входом операционного блока, выход второго регистра соединен с п выми входами второй памяти и арифметического блока, второй вход которого соединен с выходЪм второй памяти, второй вход которой соединен с выходом третьего регистра, введены группа сумматоровj, третья память, два сумматора, дополнительный регистр кода условий, семь ре гистров, два узла загрузки, шесть ш раторов , группа триггеров, выходы - регистров группы соединены с первыми входами, соответствующих сумматоров группы, вторые входы которых со единены с выходом блока формировани адреса, первым входом первого шифратора, третьими входами процессоров, третьим входом второго сумматора и первыми входами третьего и четвертого сумматоров, второй вхо последнего через восьмой регистр со динен с шиной обмена, соединенной также с вторым входом третьего сумматора, входом девятого регистра и. 384 первым входом дополнительного регистра кода условий, выход которого через десятый регистр соединен с первым входом седьмого регистра , второй вход которого соединен с выходом третьего сумматора и входом одиннадцатого регистра, выход которого соединен с первым входом третьей памяти, второй вход которой через двенадцатый регистр соединен с выходом четвертого сумматора, выход третьей памяти соединен с третьими входами треть го сумматора, выход девятого регистра соединен с вторым входом первого шифратора,выход которого соединен с третьим входом блока формирования адреса, четве)тым входом каждого процессора и вторым входом буфер(€Г)й памяти, третий вход которой соединен с выходом второго шифратора, первые входы которого, тpинa цaтoгo регистра, третьего и четвертого шифраторов, выходы пятого шифратора, первые вход и выход каждого узла загрузки и вход четырнадцатого регистра соединены с шиной управления, первый выход тринадцатого регистра соединен с вторыми входами второго и третьего шифраторов и регистров кода условий, второй выход тринадцатого регистра соединен с третьими входами второго и третьего шифраторов, третий выход тринадцатого регистра соединен с пятым входом каждого процессора, вторым входом четвертого шифратора и первым входом пятого шифратора, четвертый выход тринадцатого регистра соединен с четвертыми входами второго и третьего шифраторов, пятый выход тринадцатого регистра соединен с третьим входом первого шифратора и шестым входом каждого процессора, шестой выход тринадцатого регистра соединен с пятыми входами второго и третьего шифраторов, второй выход узла загрузки соединен с шестым входом второго шифратора и вторым входом второго узла загрузки, второй выход которого соединен с шестым входом третьего .шифратора и вторым входом первого узла загрузки, третьи выходы первого-и второго узлов загрузки соединены соответственно с вторым и третьим входами тринадцатого регистра, выход третьего шифратора соединен с седьмыми входами каждого процессора, восьмой вход которого через шестой шифратор соединен с вы5ходом четырнадцатого регистра, второй выход и четвертый вход буферной памяти соединены соответственно с вторым входом пятого шифратора и выходом четвертого шифратора, чет вертый вход микропрограммного устро ства управления через соответствующий триггер группы соединен с выходом, каждого процессора, выходы сумматоров группы соединены с четвертым входом блока формирования адре са и девятым входом каждого процесс ра, а в каждый процессор введены бу фер.ная память, два шифратора, второ триггер, три регистра, коммутатор,п чем первый выход операционного блок соединен с третьим входом арифметического блока, и первым входом перг вого шифратора, выход которого соед нен с первыми входами коммутатора, буферной памяти и входом четвертого регистра, выход которого соединен с выходом процессора, входомвторого триггера, входом первого регистра и четвертым входом операционного блока, пятый вход которого соединен с восьмым входом процессора,девятый вход которого соединен с шестым входом операционного блока, четвертым входом арифметического блока, и первым входом третьего ре гистра, второй вход которого соединен с третьим входом процессораj седьмым входом операционного блока, и пятым входом арифметического блока, шестой вход которого соединен с первым входом второго регистра, второй вход которого соединен с третьим входом третьего регистра, шестой вход процессора соединен с вторым входом коммутатора, выход которого через пятый регистр соединен со своим третьим входбм и вторым входом первого шифратора, третий вход которого соединен с выходом первого триггера , четвертый вход процессора через шестой регист соединен с четвертым входом коммута тора, пятый вход процессора соедине с входом второго шифратора, соединенного двусторонними связями с шиной управления, информационной шиной и буферной памятью, второй вход которой соединен с седьмым входом процессора, память и буферная память соединены двусторонней связью между собой, а узел загрузки содержит счетчик, коммутатор, шифратор и регистр, причем, первый 6 и второй выходы счетчика соединены с первым и вторым выходами узла, первый вход которого через последовательно соединенные -регистр и шифратор соединеныС первым входом кoM- мутатора, второй вход которого явпяч ется вторым входом узла, а третий вход соединен со вторым выходом счетчика, выход коммутатора соединен с входом счетчика и третьим выходом узла. Функциональная схема многопроцессорной вычислительной систе 1 представлена на чертеже и содержит следующие блоки: процессоры 1, операционный блок 2, арифметические блоки 3 и , блок формирования адреса 5, узлы загрузки 6, сумматоры группы 7, регистры группы 8, микропрограммное устройство управления Э, дешифратор 10, триггер группы 11, триггера 12, 13, память 14-18,регистры коды условий 19 и 20,регистры 25-4б, коммутаторы У-+Э.буферная память 50,51шифраторы 52-61 счетчики 62 и 63, информационная шина 6, шина управления 65, шина обмена 66, шина двусторонней процессоров 67. Работу многопроцессорной вычислительной системы можно описать следующим образом . В начальном состоянии все регистры , счетчики, триггера и установлены в исходное состояние или обнулены.Первыми командами, выдаваемыми машиной-диспетчером в систему по шине управления 65, осуществляется запуск узлов загрузки 6.При этом, эти команды могут состоять из нескольких слов, каждое из которых сопровождается управляющим сигналом.Узел загрузки 6, состоящий из регистра 46, шифратора 55, коммутатора 62 автоматически, по заранее заданной программе распределяет входную информацию для памятей 1б,17 и 18, а также для микропрограммного устройства управления 9. Узел загрузки 6, состоящий из регистра Ц, шифратора 5, коммутатора kS и счетчика 63, управляет вводом и выводом данных, подлежащих обработке в процессорах 1. Счетчики 62 и 63 служат для подсчета числа слов .команд, поступающих с шины уп; равления и с информационной шины 6 на соответствующие,регистры «6 и 5t с которых потом данные поступают на

7

шифраторы 55 и 5, предназначенные для анализа и преобразования кодов, поступающих команд. Далее в работу включаются коммутатора 49 и 48, которые выдают на вход счетчиков 63 и 62 информацию, необходимую для подсчета числа поступающих команд. После того как приняты первые управляющие команды и запущены узлы загрузки 6,выполняется загрузка микропрограммного устройства управления 9 и памяти 18, Управляющие массивы данных по шине управления 65 i поступают на шифратор 56, который преобразовывает форматы поступающих чисел в формат,заданный для данной системы, и далее преобразованные числа массива поступают на буферную память 51 последовательно друг за другом. Управляется шифратор 56 регистром 44,с выхода которого поступает сигнал на. преобразование входного массива данных. Буферная память 51 управляется шифратором 58, на входы которого с выходов регистра 44 поступают сигналы, свидетельствующие о начале обмена данными, конца обмена данными, длины вектора массива данных и начальный адрес массива данных. Счет числа передаваемых элементов массива данных выполняется в машине-диспетчере, а завершение каждой из команд осуществляется по сигналу из системы в машину-диспетчер.При этом счет адресов микропрограммного устройства управления 9 и преобразование слов внешних устройств в формат слов данной системы выполняется ап- паратно. Точно также для первоначальной загрузки памяти 18 регистр 40 запускается автоматически и работает в режиме счетчика по +1, Во время вычислительного процесса адрес для памяти 18 выставляется в регистре 40 с выхода сумматора 23, который формирует адрес памяти 18. Исходные адреса, необходимые для памяти 18 содержатся в памяти 17,считывание адресов с которой осуществляется с помощью регистра 42, сумматора 24 и регистра 43. Исходные данные для регистра 43 могут поступать с шинь) обмена 66 или с выхода р§гистра 39. Второй вход сумматора 24 подключен к выходу . блока формирования адреса 5, который формирует адреса для сумматоров 22, 23,24 и группы сумматоров 7. Сумматор 24 с помощью регистра 43 формирует очередные адреса памяти 17,кото512388

рые выставляются в регистре .Считанные адреса с памяти 17 с помощ-ью сумматора 23 и регистра 1 преобразовываются или модифицируются в очередные адреса памяти 18, которые выставляются в регистре 0.

Далее из памяти 18 считываются команды программы, базовый набор которых ориентирован на выполнение опера50 ци1 с матрицами, быстрого преобразования Фурье, математической статистики, спектрального анализа, решения задач линейного и динамического программирования и т.д. Кроме этого,память 18 служит для хранения констант общих для всех процессоров 1 и результатов нёкоторых программ, например полей экстремумов, и определение их координат в числовом массиве.

После загрузки микропрограммного устройства управления 9 и памяти 18 выполняется загрузка памятей Т процессоров 1, которая осуществляется с

25 шины с помощью шифратора 53 и буферной памяти 50. Управления вводом, а также в дальнейшем и выводом информации, осуществляется узлом загрузки 6, состоящим из регистра

30 5 шифратора S, коммутатора 8 и счетчика 63, а также шифратором 59, входы которого подключены к соответствующим выходам регистра +4, и по которым поступают значения кодов

эг начала обмена, конца обмена, длины массива данных и начального адреса массива данных, а также значение кода маски процессоров. Предварительно, по отдельной команде, устанавли- ;

40 вается значение в разрядах буферных памятей 50 и 51 активности каждой буферной памяти, предназначенных для активизации и включение в процесс обмена с шиной 6 процессоров. С выхо. да буферной памяти 50 по двусторонней шине массив данных поступает для записи в память процессора. Управление или выборка адресов памяти 14 осуществляется с помощью регистра 25, адреса в который выставляются с выхода арифметического блока 3. Арифметический блок 3 формирует и модифицирует очередные адреса памяти 1 k с помощью регистра 26 и памяти 15,в которой хранятся значения адресов для памяти . Кроме этого,адреса для памяти 1 могут поступать и с операционного бло-. ка .2 и с вйхода блока формирования адреса 5- В свою очередь формиро 75

вание адресов для памяти 15 поступающих с регистра 27, осуществляется или в блоке формирования адресов 5, или в группе сумматоров 7.Регистр 25 может работать либо в виде п-разрядного счетчика, либо в виде п-разрядного регистра. Выставленный адрес в регистре 25 выбирает слово из памяти 1 и. в то же время в арифметическом блоке 3 формируется очередной адрес памяти. Возможны следующие Способы адресации памяти k всех процессоров:

слоями, по адресу, сформированному в блоке формирования адреса 5;

по адресам, независимо сформированным от других процессоров 1 и записанных в память 15;

по адресам, назависимо сформированным в арифметическом блоке 3. Текущий адрес, сформированный в арифметическом блоке 3 каждого процессора 1 может быть принят из соседнего процессора 1 по шине двусторонней связи б7, или по шине обмена 66 .,

Для некоторых операций, в частности ввода-вывода, адреса обращения к памяти 1А помещаются в память 15 каждого процессора и в ее опрееленные ячейки . В ходе вычислительного процесса может возникнуть ситуация исключения или,наоборот, включения в процесс арифметического блока 3 и памяти 15. Для .этого существует триггер 13, значение кода в который заносится о выхода регистра 28. Далее по заданной подпрограмме, которая записана в микропрограммном устройстве управления 9, выполняется запись данных в операционный блок 2,где они подвергаются обработке, причем в операционном блоке 2 могут выполняться любые арифметические и логические операции как над числами с фиксированной, так и с плавающей запятой.

Для включения в процесс обработки того или иного процессора 1 небходимо его активировать.Это выолняется посредством триггера 12, выход которого подключен к одному з входов операционного блока 2. Выборка очередного процессора 1 , в риггере 12 которого существует начение метки активности, выполнятся последовательно от одного риггера 12 к другому. При этом

10

1238

одновременно с переходом к последующему триггеру гасится предыдущий. Кроме этого, триггер 12 включает s в процесс обмена данными между процессорами 1 операционный блок 2,который выдает или в шину обмена 66, или в шину двусторонней связи б7 данные, необходимые для других процессоров 1. Операции обмена, также

как и вычислительные операции,могут быть oднoтaкtными и многотактными. Многотактными вычислительными операциями являются операции умножения, деления и т.д. При этом как

.во время выполнения однотактных, так и многотактных операций.микропрограммное устройство управления 9 может отключаться от управления процессорами 1 и выполнять команды операций ввода-вывода информации. Кроме того, возможно совмещение и арифметико-логических операций в операционном блоке 2 с операцией загрузки данных. Зто совмещение состоит

в том, что обработка данных в операционном блоке 2 выполняется под действием микрокоманды, считанной из микропрограммного устройства упрабления 9 на буферные регистры, не показанные на чертеже, а параллельная ей операция ввода-вывода информации из памяти 1 осуществляется с помощью команды машины-диспетчера и затребованной по сигналу готовности.

Совмещение арифметико-логических операций с загрузкой данных в операционные блоки с памяти 14 выполняется одной микрокомандой, в которой указаны параметры проведения вычислительных операций и операций загрузки . При этом обработка ведется над теми Мислами, которые в ходе вычислительного процесса циркулируют в pef гистрах операционного блока 2J .

В ходе вычислительного процёсса может возникнуть необходимость выключения из процесса памяти It, которое осуществляется с помощью- регистра 28, выход которого подключен к управляющему входу регистра 25. Выход регистра 28, помимо этого, подключен к входу триггера группы 11,назначение которого состоит в том, что он фиксирует по дизъюнкции наличие активноге хотя бы одного из всех процессоров 1 . Наличие метки активности в триггере группы 11 позволяет путем подключения его выхода к микропрограминому устройству управления 9. осуществить переход по условию активно сти процессоров 1. Возможны следущие способы актив ции процессоров 1: внешняя активация; активация по ooflepmHwoitiy Операци онного блока 2; активация по содержимому регистра 29; . активация по значению триггера 1 Значение внешней активаций формирУ ется с помощью регистра 38 и и ифрато ра 61, содержимое в, который загружа ется с блока формирования адреса 5; шины обмена 66 и с одного из выходо регистра с которого поступает з чение кода маски. По этому значению кода маски совместно со значением кода из блока формирования адреса 5 формируется значение внешней актива ции. Далее это значение поступает на вход регистра 30 и с.помощью комм татора kj, шифратора 52 и регистра а также в зависимости от внутреннего I состояния их формируется значение внешней активации, которое в оконча тельном виде поступает на регистр 259 триггер 13 и триггер группы 1К Возможны также следущие способы внешней активации: йктивация процессора с номером Р активация всех процессоров 1, кроме процессора с номером Р; активация процессоров Т с номерами от О до Р ; активация процессоров с номерами от P-f 1 до N-1 . Модификация поля Р обеспечивается арифметико-логическими операциями в блоке формирования адреса 5« В регистре 29 каждого процессора содержится по 4 триггерар участвущих в формировании активности.При помощи маски, задаваемой с одного из выходов регистра kk через регистр 30 и коммутатор i/j выбирается от одного до четырех триггеров активных в данном процессе. При этом могут быть Следующие способы активации по триггерам регистра 29 с участием маски: Нрямые выходы триггеров; инверсные выходы триггеров; дизъюнкция выходов триггеров; конъюнкция выходов триггеров; неэквивалентность выходов триггеipOBo812 Активация по триггерам регистра 29 позволяет активировать процессоры 1по любому нерегулярному закону,полученному в процессе решения задачи или по закону 5 заданному программистом. Активация по содержимому операционного блока 2 может быть следую-щих типов: содержимое операционного блока 2 0; содержимое операционного блока содержимое операционного блока 2кО; содержимое операционного блока 2 Q, Содержимое блока 2 передается в шифратор 52 и вычисленное значение активности обратно с регистра 28 управляет работой блока 2. Активация по триггеру 12 была рассмотрена выше, С помощью команд пересылок загружаются регистры группы регистров 8,которые совместно с сумматорами группы 7 формируют адреса операндов для всех операционных блоков 2, регистров 27 и регистра 25. Модификация этих адресов может выполняться.автономно в каждом процессоре 1 или путем подключения выхода сумматоров группы к одному из входов блока формирования адреса 5 который по обратной связи выдает новое значение адреса для обработки его в сумматорах группы. Первоначальные значения этих адресов поступают из микропрограммного устройства управления 9, которое к тому же выдает на вход регистра 31 значение формата чисел,подлежащих обработке в блоке 2, значение адресов для, блока формирования адреса 5 через регистр 35 и сумма, а также значение кода услов регистр кода условий 20. С помощью регистров кода условий 19 и 20,.а также регистров 3 и 37 выполняется программно-заданный останов работы соответственно микропрограммного устройства управления 9 и памяти 18 при условиях, сформированных по конъюнкции в регистрах 19 и 20, Кроме этого, выход микропрограммного устройства управления 9 подключен к одному из входов арифметического блока , который совместно с регистром 33 и памятью 16 служит для запоминания адреса очередной микрокоманды при обращении к сторонней микропрограммы. Модификация таких возврата осуществляется в арифметическом блоке ..который может работать в трех режимах: ело-, жения, вычитания и режиме счетчика. Для гибкого и эффективного обмена данными между процессорами 1 , а также между процессорами и внешними уст ройствами служит регистр 32 и шифратор 60, которые осуществляют разбивку поля процессоров на сегменты по шине двусторонней связи б7 и шине обмена 66. Возможные варианты сегмен тации представляют собой объединение в кольцо двух, четырех, восьми, шестнадцати и т.д. процессоров. Обра зование сегментов обеспечивается Динамически по программе, а необходимость в сегментации вытекает из обработки массивов данных с большим удельным весом операций обмена.Решение относительно разбиения поля про цессоров на сегменты, размеры сегмен тов принимает программист для каждой конкретной задачи. Сегментирование не распространяется на шины6 и 65, оно требует для каждого сегмен та автономности по нумерации процессоров и шинам 66 и 67. Обмен между процессорами разных сегментов возможен только посредством изменения границ сегментов, которые устанавливаются посредством загрузки соответ ствующего кода из машины-диспетчера в регистр 32 и далее в шифратор 60. Шифратор 60 по соответствующей программе осуществляет преобразование данного кода с последующей его мо дификацией по условию и выдает на соответствующие управляющие шины .сиг налы,осуществляя тем самым, а следовательно, и всего поля, разбивку на заданные сегменты. В ходе работы системы могут возни нуть случаи.условного перехода,ожи8даемое условие которого задается в микрокоманде, а фактическое получается в результате обработки в блоке 2. Сравнением обоих условий вырабатывается сигнал перехода на другую микрокоманду, а в случае без$ словного перехода адресация перехода задается в ОТведенном для этого поле микрокоманды. Таким образом, структура, конструктивные связи и функциональные возможности системы позволяют значительно повысить эффективность решения на ней задач. Вычислительные комплексы, построенные на базе многопрюцессорной вычислительной системы, могут использоваться для: обработки результатов геофизических и океанографических исследований;обработки аэрофотоснимков,изображений земной поверхности, полученных со спутников, микрофотографий, телевизионных изображений, распознавания образов; обработки информации при испытании самолетов и других сложных обт.ектов;интенсивного-наблюдения за больными и обработка данных в медицине;обработки радиолокационных сигналов;обработки акустических сигналов; управления реакторами; обработки данных в метеорологии и т.д. Испытание опытного образца Геофизического вычислительного комплекса на контрольных задачах подтвердило его высокую эффективность и ожидаемые характеристики.

Авторы

Даты

1983-07-15—Публикация

1979-08-02—Подача