го счетчика первого дешифратора блока управления соединен с первым инверсным входом второго элемента И и с первым входом третьего элемента И, вторые входы которых объединены и подключены к выходу признака переполнения второго счетчика второго дешифратора блока управления, выходы которого являются выходом номера такта вычислений блока управления, вход второго деишфратора блока управления соединен с выходом второго счетчика, счетный вход которого через делитель частоты соединен с выходом первого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, отличающееся тем, 4TOj с целью расширения функциональных возможностей устройства за счет обработки как значений координат, так и их приращений, в него введены четвертый, пятьм, шестой регистры, второй и третий дешифраторы, второй блок памяти, два мультиплексора, а блок управления дополнительно содержит распределитель импульсов второй триггер, второй формирователь импульсов, второй,, третий и четвертый элементы ИЛИ и четвертьш элемент И, причем входы приращения первой и .второй координат устройства соедине- ны с информационными входами пятого и шестого регистров соответственно выходы которых соединены с входами второго дешифратора, выходы которого соединены с первой группой адресных входов второго блока памяти, вторая группа адресных входов которого соединена через последовательно включенные третий дешифратор и шестой р егистр с входом приращений угла поврота устройства, выход второго блока памяти соединен с первыми информационными входами первого и второго мултиплексоров, управляюш 1е входы которых соединены с выходом управления режимом блока управления, вторые информационные входы первого и второго мультиплексоров соединены с выходами первого и второго сдвигателей соотвественно а выходы мультиплексоров соединены с входами сумматоров, синхронизирующие входы .третьего, четвертого, пятого и шестого регистров соединены с выходом управления записью информации в режиме приращения блока управления, входы запуска режима полных значений, запуска режима приращений, останова блока управления являются одноименными входами устройства и подключены к первому входу второго элемента ИЛИ, входу второго формирователя импульсов и входу сброса второго триггера соответственно, выход второго формирователя им- nvnbcoB соединен с первьп входом четвертого элемента И, второй вход которого соединен с выходом третьего элемента И и входом сброса первого триггера, вход установки которого соединен с вьгходом второго элемента I-fflH, второй вход которого подключе к входу запуска режима приращений блока управления, первый выход рас- пределителя импульсов подключен к певому входу четвертого элемента ИЛИ и является выходом управления запись информации в режиме приращения блока .управления, второй выход распределителя импульсов подключен к первому входу третьего элемента ИЛИ, второй и третий входы которого подключены к вькодам первого формирователя импульсов и элемента задержки соответ- :; гвенно, вьпсод второго элемента И подключен к второму входу четвертого элемента ИЛИ, выход которого является выходом управления записью вход ;Ной информации блока управления, третий выход и вход запуска распределителя импульсов соединены с выходом управления режимом блока управления, вход блокировки распределителя импульсов подключен к прямому выходу второго триггера, вход установки которого подключен к выходу четвертого элемента И, выход третьего элемента ИЛИ подключен к входу сброса второго счетчика и является вторым выходом коррекции блока управления.

Изобретение относится к вычислительной технике.

Цель изобретения - расширение функциональных возможностей .устрок- ства за счет обеспечения возможности работы как в режиме преобразования полных значений исходных данных, так и их приращений.

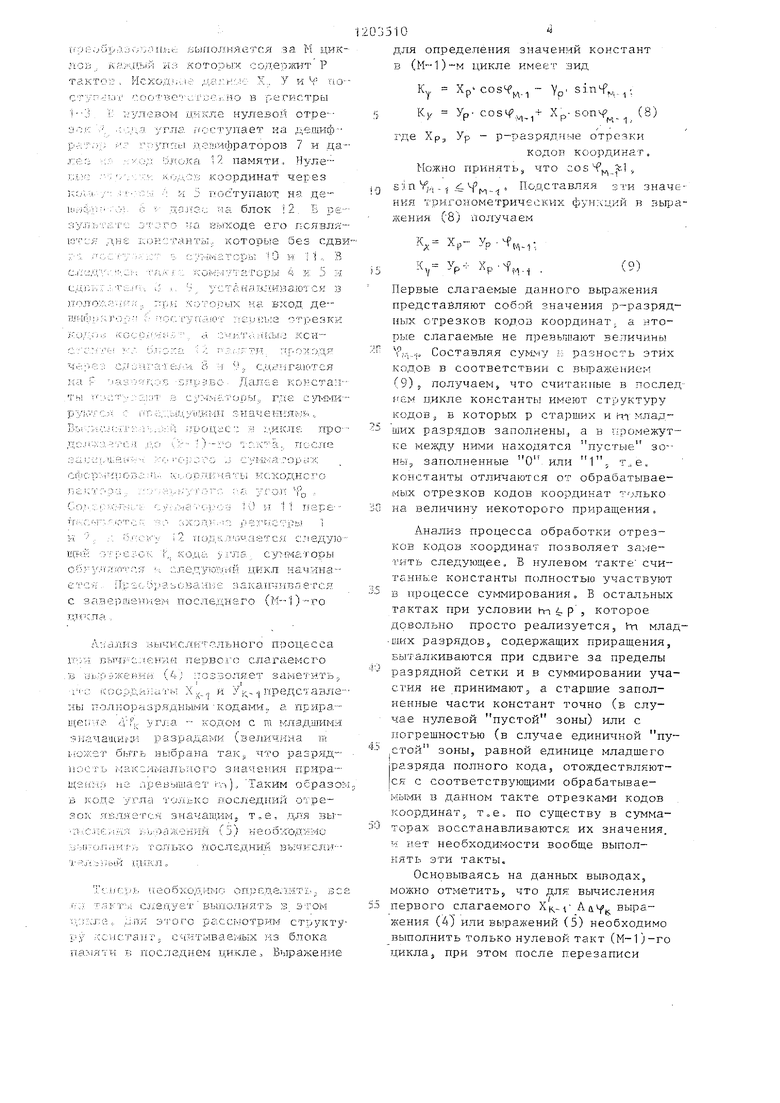

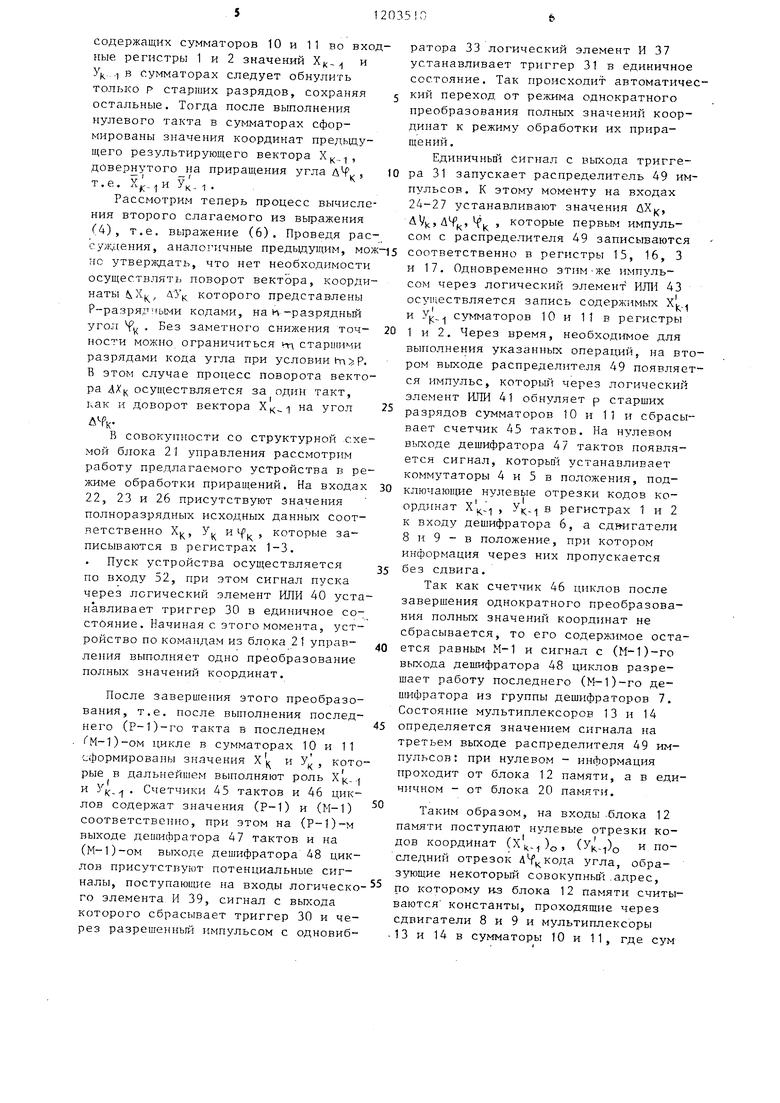

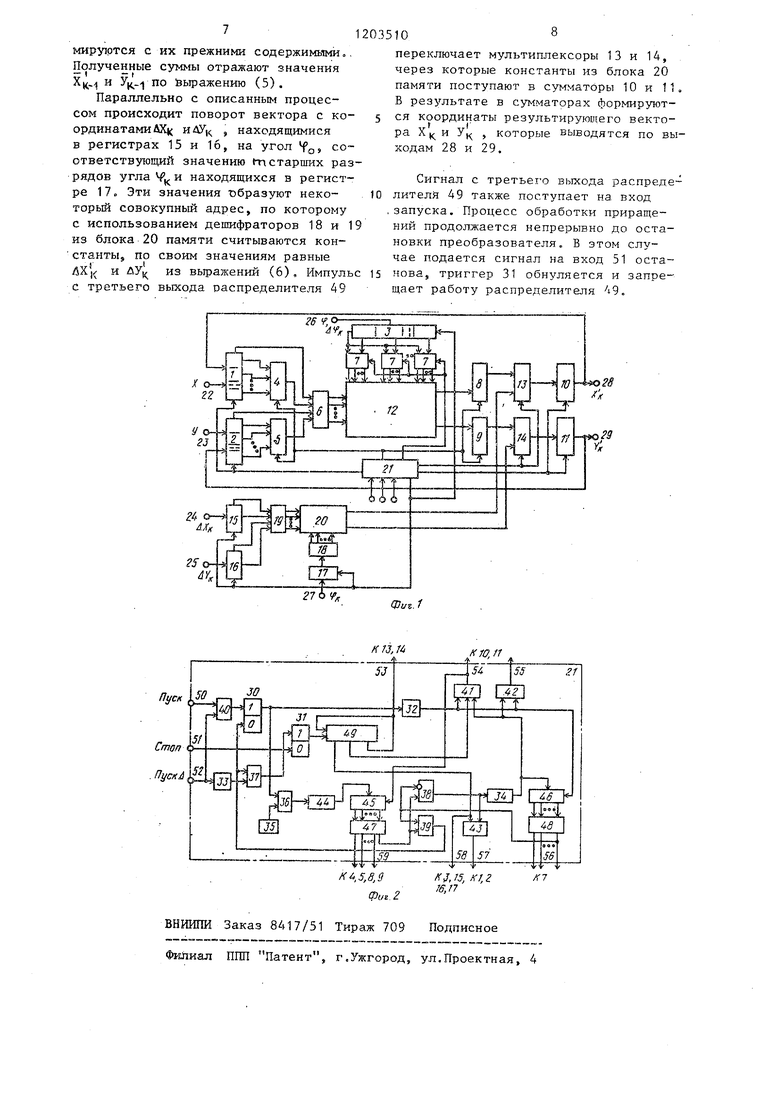

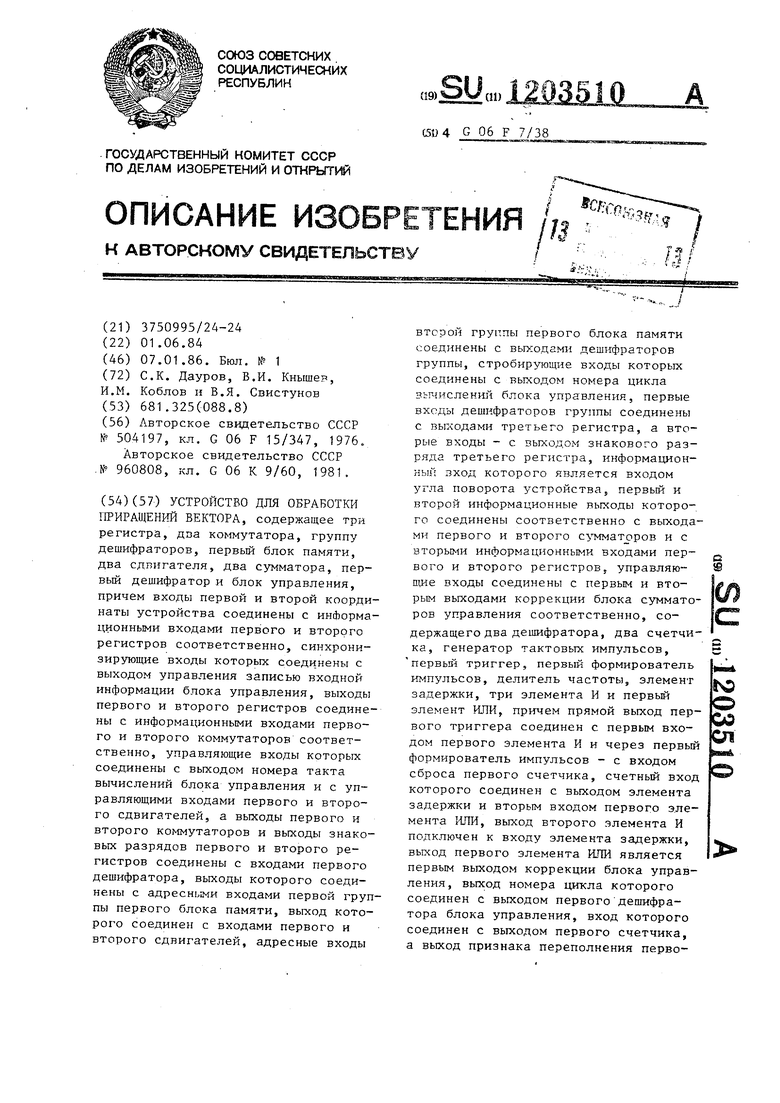

На фиг. 1 представлена структурная схема предлагаемого устройства, на фиг. 2 - структурная схема блока управления.

Устройство для обработки приращений вектора содержит регистры 1-3, коммутаторы 4 и 5, дешифратор 6, группу дешифраторов 7, сдвигатели 8 и 9, сумматоры 10 и 11, блок 12 памятмл, мультиплексоры 13 и 14, р- разрядные регистры 15 и 16, т-раз- рядный регистр 17, дешифраторы 8, и 19, блок 20 памяти, блок 21 управления, первый 22 и второй 23, четвертый 24, пятый 25, третий 26, шестой 27 информационные входы устройства, выходы 28 и 29 устройства.

Блок 21 управления содержит тригг геры 30 и 31, одновибраторы 32 и 33, элемент 34 задержки, генератор 35 тактовых импульсов, элементы Pi 36-39 элементы 1-ШИ 40-43, делитель 44 частты, счетчики 45 и 46, деимфраторы 47 и 48, распределитель 49 импульсов вход 50 запуска режима полных значений, вход 51 останова, вход 52 запуска режима прираш;ений, выход 53 управления режимом, выходы. 54 и 55 коррекции, выход 56 номера цикла вычислений, выход 57 управления записью входной информации, выход 58 управления записью информации в режиме приращения, выход 59 номера тактов вычислений.

Процесс поворота вектора с полными значениями исходных данных Х, f выполняется по выражению

К Тк 1

(1)

где X1 - результирующий вектор в

К

к-и момент времени;

Av - матрица поворота вектора

на плоскости вида

cos Ч к sin f.

А и TK

- cosl t

Представляя значения Х, и А. в форме

XK Хк.1+ Ь АМ-К-/ -

2035102

где д X, приращения исходных данных в к-и момент времени,. и подставляя их в выражение (1), получаем

5

. .к АдЧ /Ч к-, АЧ /Чк- - К (3)

Учитьгоая, что Ai -Х ( Х,,., , выражение (3) можно представить в следующем виде: 10,

к

где в право й части присутствуют приращения исходных данных и вычислен- Hbrit в предыдущий момент времени результируюш;ий вектор х5,. Таким образом, из выражения (4) видно, что при представлении исходных данных в их приращениях ЛЧ., процесс определения результирующего вектора Х распадается на операцию доворота вектора Xi. на угол, равный приращению Aft; J и операцию поворота вектора дХ приращений на полньш угол Т.

Первое слагаемое вьфажения (4) в

скалярном виде:

Vr Х ,, СОЗДН - y sin& У,, .собйМ к + Х -1-51пДЧк (5)

где Х|,, У, координаты вектора

Х| после его поворота на ДЧ у;.

Определение выражений (5) осуществляется частью устройства, в которую

входят блоки 1-14 и 21. Одновременно

вычисляется и второе слагаемое из выражения (4), которое в скалярной форме имеет вид:

ЛХ uXi. - , ЛУк - . (6)

Определение вьфажений (6) осуществляется другой частью устройства, в которую входят блоки 15-21. Вычислен- ные по вьфажениям (5) и (6) значения координат суммируются

Х Хкп + 4X1 ;(7)

X 1

в сумматорах 10 и 11, на выходах которых получаются искомые значения Х, У, вектора в к-и момент времени. Устройство работает следующим образом.

в режиме преобразования полных значений код угла f и коды координат X и У разбиты соответственно на М и Р кодовых отрезков, в связи с чем

ifO::oG;i ::iJ ъ liiic:: выполняется за М циклов , )лй;«..ць1Й i-uj которых содер}К1П Р такте;;:. Исход;,uc; .:-: л, У и Ч по CTyp Mj-i соотве ч: i . в регистры i- j L Т;улевом цикле нулевой отре-- : . ;ч:.,, 1 угла ггостз гшет на депшф-- рг/г; у . rv;yTiT;ui ,11;т Л1ифраторов 7 и да .гег:; : ;, Ьггок. 12 памяти,, Нуле- г,. : : ,;- . ::ч коде:-:-; координат через 1ал-1 /: i --:y-i ; Я 5 поступают на деIn-iu/i:- . О Ь о п;з.;та;.: Mil блОК 12 Б рв

зу.ггьч а-г:: оччуго ;;а выходе его псявля- 1:ггу:я :1кг ;;:.ijHСтанти;, которЕяе без сдвлсд);;-,:; .; T:;:.,if-, : i, ;р устАкг)В;1И}лаю Т ся з п ; ЛО;лг ; ;у, г:ри Kovopoix на вход де- tijf-Enj;jу) ..;у- осч уri,;ijO f nepiiijie отр езкн

c/ C: /: i;;: ; - . Ьт;с-; а -: и г гтл

Чгг. ::;: с;г:У.1Г;;1-1 е,плг и 1 Vj Cyi : iira OTCH

i;;i F Далее констап

Th; 1 ;.ч;Т; .;-:;.к1 Г S .-vopb,, rjie e ;n-Bv K

ру;:л ся ;; 1гпс,-:: 1цуи5;:мп значекиямь,,

Ik.i ;:,;.aji:.;iA :: У: .::;:ft : н :.,икле лро

делу:.-ччу лло ;:--:)-У о УУУ- а. после

сфср:м п;о13У :п,.. к:., опличаты ксходнсго

СП; :. У -.-V-ia :-i-i; .: Щ К И 11 иарб - тГ/чС -т-: iO r,;;r; ;:,-. :ЧЛЭП1-,.-; р в Г лСУрЫ I

ЕСнй а7у:-е;;ок I ,, ко.ца . Л5 сумма торы с :У - ул; иу : ; ; ч уледутагл-гй цикл начинас завершет-гкем последнего (M-- i)--ro

ТЛ ПС Rcl

Л:;с1лиз оычксли ль)1ого процесса пуу вьгч;-слр;и:аи первог о слагаенсго в иъУ)жевкй: (4; ;7оз5оляет заметить

:J

( (.: (СООрДаУаГ;-. Х.,,, И У ;,;, .| ПредС ХЯЗЛены полкоразрядкьми-кодами,, а прира.-- щеггл ур;, угла - кодом с m клад-пими

: i;a4a iLHfK разрадами (вeличjiнa ш быть ньюрана так -что разряд- иоо гь гаксимальтюго значения пряра-- mSiCuj яе лревъ1шае1 i-n).. Таким образом в к:оде -угла лоследни; отрезок является; зршчащкм. т ., е, для вы-У1 iC.iU;:, УчЯ jyj-OflAOHfiH (j) п&ООУ ОЦКЛО

j-:ii:4j.r-iiJH -у -голько последний вьик-сли-- j.-r::j-i:;i:;: Lft 1а;:кл,

T ..i rr;ji:, 1еобход;.мг; определите,, Бс : сз.;едует вьгаолнять з э-гом у;:улй, апя этого рассмотрим структуру /сснстапг, ечитьшае1-4ь;х из блока па:ияти в последнем цикле, Возражение

для определения значений констант в ()м цикле имеет :зид

KY Хр созЧ ц.- YP sinf.., К), Ур. ,,,,, Хр. Бопч;.(8)

где Хрэ Ур - р-разрядные отрезки кодов координат.

МО-ЖНО принять, что COS -f| лГ.1 ,

sin V,, . .. . Подставляя эти значения тригонометрических фунл-ций в зырач- жения ( 8) -Получаем

Кд X,Ур --с

Г V VчП

А,- р .- лр -VM,

(9)

Первые слагаемые данного выражения представляют собой значения р-разряд ных отрезков кодов координат, а нто- рые слагаемые не превьппают величинь г.-,-1 Составляя сумму г; разность этих кодов в соответствии с выражением (9)„ получаем, что считанные в посленем цикле константы имеют структуру кодов 3 в которых р и н.л младших разрядов заполнены,, а в Глромежут ке межд-у ними находятся пустые зо-- ны, заполненные О или Г т., е. константы отличаются от обрабатываемых отрезков кодов координат ту лько на величин-у некоторого приращения.

Анализ процесса обработки отрезков кодов координат позволяет заметить следующее. В нулевом такте счи- таннь;е константы полностью участвуют в процессе суммирования, В остальных тактах при условии i-n р , которое довольно просто реализуется, Vn мла, разрядов5 содержащих приращения, выталкиваются при сдвиге за пределы разрядной сетки и в суммировании участия не принимают, а старшие заполненные части констант точно (в слу- ч,ае нулевой пустой зоны) или с ц-огрешностью (в случае единичной пустой зоны, равной младшего разряда полного кода, отождествляются с соответствующими обрабатывае- 1- лыМ1 в да-нном такте отрезками кодов координат, т.е. по существу в сумматорах восстанавливаются их значения. и нет необходимости вообще выполнять эти такты.

Основываясь на данных выводах, можно отметить,, что для вычисления первого слагаемого А а Yj выражения (4) или вырайсений (5) необходимо

выполнить только нулевой такт (М-1)-го тдикла, при этом после перезаписи

содержащих сумматоров 10 и 11 во входные регистры 1 и 2 значений Х, и ,., в сумматорах следует обнулить только р старших разрядов, сохраняя остальные. Тогда после выполнения нулевого такта в сумматорах сформированы значения координат предыдущего результирующего вектора Х|, довернутого на приращения угла , т.е. У 1 ,

Рассмотрим теперь процесс вычисления второго слагаемого из выражения (4), т.е. выражение (6). Проведя рассуждения, аналогичные предьщущим, мож но утверждать, что нет необходимости осуществлять поворот вектора, координаты Xц, ДУк которого представлены Р-разрядчыми кодами, на н-разрядный угол Уц . Без заметного снижения точ- ности можно ограничиться v-n старшими разрядами кода угла при условии (. В этом случае процесс поворота вектора 4Хк осуществляется за один такт, как и доворот вектора Х,- на угол

совокупности со структурной схемой блока 21 управления рассмотрим работу предлагаемого устройства в режиме обработки приращений. На входах 22, 23 и 26 присутствуют значения полноразрядных исходных данных соответственно Хц., У и f k которые записываются в регистрах 1-3.

Пуск устройства осуществляется по входу 52, при этом сигнал пуска через логический элемент ИЛИ 40 устанавливает триггер 30 в единичное состояние. Начиная с этого момента, устройство по командам из блока 21 управ- ле1П1я выполняет одно преобразование полных значений координат.

После завершения этого преобразования, т.е. после выполнения последнего (Р-1)-го такта в последнем М-1)-ом цикле в сумматорах 10 и 11 сформированы значения X | и У , которые в дальнейшем выполняют роль Х).) и УК, Счетчики 45 тактов и 46 циклов содержат значения (Р-1) и (М-1) соответстветпю, при этом на (Р-1)-м выходе дешифратора 47 тактов и на СМ-1)-ом выходе дещифратора 48 циклов присутствуют потенциальные сигналы, поступающие на входы логического элемента И 39, сигнал с выхода которого сбрасывает триггер 30 и через разрешенный импульсом с одновибратора 33 логический элемент И 37 устанавливает триггер 31 в единичное состояние. Так происходит автоматичекий переход, от режима однократного преобразования полных значений координат к режиму обработки их приращений.

Единичньй нгиаг1 с выхода триггера 31 запускает распределитель 49 импульсов. К этому моменту на входах 24-27 устанавливают значения ДХ, АУ, 4f,, f|, , которые первым импульсом с распределителя 49 записываются соответственно в регистры 15, 16, 3 и 17. Одновременно этим-же импульсом через логический элемент ИЛИ 43 осуществляется запись содержимых Х, и У| сумматоров 10 и 11 в регистры 1 и 2. Через время, необходимое для выполнения указанных операций, на втром выходе распределителя 49 появляеся импульс, которьш через логический элемент ИЛИ 41 обнуляет р старших разрядов сумматоров 10 и 11 и сбрасывает счетчик 45 тактов. На нулевом выходе дешифратора 47 тактов появляется сигнал, KOTOpbrfi устанавливает коммутаторы 4 и 5 в положения, подключающие нулевые отрезки кодов координат , . в регистрах 1 и 2 к входу дешифратора 6, а сдгшгатали 8 и 9 - в положение, при котором информация через них пропускается без сдвига.

Так как счетчик 46 циклов после завершения однократного преобразования полных значений координат не сбрасывается, то его содержимое остается равным М-1 и сигнал с (М-1)-го выхода дешифратора 48 циклов разрешает работу последнего (М-1)-го дешифратора из группы дешифраторов 7. Состояние мультиплексоров 13 и 14 определяется значением сигнала на третьем выходе распределителя 49 импульсов: при нулевом - информация проходит от блока 12 памяти, а в единичном - от блока 20 памяти.

Таким образом, на входы .блока 12 памяти поступают нулевь е отрезки кодов координат (Xh.)o, (УК-,)О и последний отрезок угла, образующие некоторый совокупный.адрес, по которому КЗ блока 12 памяти считываются константы, проходящие через сдвигатели 8 и 9 и мультиплексоры 13 и 14 в сумматоры 10 и 11, где сум

MHpyipTCH с их прежними содержимыми о, Полученные отражают значения Х(, и У(- по йыражению (5).

Параллельно с описанным процессом происходит поворот вектора с ко- ординатами ДХ« , находящимися в регистрах 15 и 16, на угол YO соответствующий значению (пстарших разрядов угла V и находящихся в регистре 17 Эти значения tjepasyroT неко- торый совокупный адрес, по которому с использованием дешифраторов 18 и 19 из блока 20 памяти считываются кон- станты, по своим значениям равные ЙХ. и ДУ( из вьфажений (6), Импульс с третьего выхода распределителя 49

переключает мультиплексоры 13 и 14, через которые константы из блока 20 памяти поступают в сумматоры 10 и 11, В результате в сумматорах формируются координаты результирующего вектора Хц и У , которые выводятся по выходам 28 и 29.

Сигнал с третьего выхода распределителя 49 также поступает на вход .запуска. Процесс обработки приращений продолжается непрерывно до остановки преобразователя, В этом случае подается сигнал на вход 51 останова, триггер 31 обнуляется и запрещает работу распределителя А9,

гп

5o-W/

4028

-I

Фиг.Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования координат | 1984 |

|

SU1179324A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

| Устройство для преобразования координат | 1985 |

|

SU1254475A1 |

| Цифровой преобразователь координат | 1980 |

|

SU943715A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ВЕКТОРОВ И ДУГ НА ЭКРАНЕ ЭЛЕКТРОННО-ЛУЧЕВОЙ ТРУБКИ | 1990 |

|

RU2050021C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство поворота изображения на экране телевизионного приемника | 1987 |

|

SU1424028A1 |

| Линейный интерполятор | 1987 |

|

SU1418751A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Стоп

. Пуск А

К13,«

кю.п

f ,5,8,3 фи1- 2

ВНЙИПИ Заказ 8417/51 Тираж 709 Подписное Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

KJJ5, К, г W, П

К1

| Устройство для поворота вектора | 1974 |

|

SU504197A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-07—Публикация

1984-06-01—Подача