прямой выход которого подключен к второму входх третьего элемента ИЛИ, группа выходов гкразрядного распределителя илшульсов блока управления соединена с соответствующими входами регистров коэффициента и аргумента, выход регистра аргумента подключен к второму информационному входу схемы сравнения, регистра коэффициента соединен с первым входом седьмого элемента И, выход которого подключен к первому входу второго сумматора, выход суммы которого соединен с информационным входом четвертого регистра сдвига, выход которого подключен к второму входу второго сумматора, выход переноса которого соединен с первым входом пятого элемента И, выход п-го разряда п-разрядного распределителя импульсов блока управления подключен. к вторым входам пятого и шестого элементов И, ко входу сброса схемы сравнения, к входу сброса четвертого триггера и первому входу восьмого элемента И, выход которого соединен с входом установки четвертого триггера, прямой выход которого подключен к второму входу седьмого элемента И, выход четвертого элемента ИЛИ блока управления соединен с входами записи первого, второго и четвертого регистров сдвига, прямой выход пятого триггера блока управления подключен к входу ввода данных второго регистра сдвига, ко второму входу второго элемента ИЛИ и к входу записи третьего регистра сдвига, входы ввода данных первого, третьего и четвертого регистров сдвига соединены с шиной нулевого сигнала преобразователя, выход переноса первого сумматора подключен ко второму входу восьмого элемента И, выход генератора тактовых импульсов блока управления соединен с входом синхронизаюш четвертого регистра сдвига, выход девятого элемента И блока управления подключен к второму входу четвертого элемента И,вход задания режима преобразователя соединен с управляющим входом первого коммутатора, причем в блоке управления выход генератора тактовых импульсов соединен через элемент НЕ с первыми входами элементов ИЛИ-НЕ и девятого элемента И и с входом п-разрядного распределителя импульсов, выход п-го разряда которого подключен к второму входу элемента ИЛИ-НЕ и к первому входу четвёртого элемента ИЛИ, выход (n-l)-ro разряда п-разрядного распределителя импульсов соединен с вторым входом девятого элемента И, выход которого подключен к входу сброса пятого триггера и входу генератора одиночных импульсов, информационный выход которого соединен с входом второго коммутатора, второй информационный выход которого подключен к входу установки пятого триггера, прямой выход которюго соеданен с вторым входом четвертого элемента ИЛИ, вход начального запуска преобразователя подключен к входу управления ключа, выход которого соединен с управляющим входом генератора одиночных импульсов, вход задания режима преобразователя подключен к управляющему входу второго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Устройство для вычисления экспоненциальной функции | 1982 |

|

SU1057944A2 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

ФУИКЦИОНАЛБИЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий первый, второй и третий регистры сдвига, первый, )й и третий триггеры, первый, второй и третий элементы И и блок управления, состоящий из генератора тактовых импульсов и ключа, причем входы синхронизации первого, второго и третьего регистров сдвига соединены с выходом генератора тактовых импульсов блока управления, о тличающийся тем, что, с целью расширения функциональных возможностей за счет вычисления как логарифмической, так и показательной функций, в него дополнительно введены первый и второй сумматоры, регистр коэффициента, регистр аргумента, четвертый регистр сдвига, схема сравнения, первый коммутатор, четвертый триггер, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый, второй и третий элементы ИЛИ, первый и второй элементы задержки, а в блок управления введены п-разрядный распределитель импульсов, генератор одиночных импульсов, второй коммутатор, пятый триггер, девятый элемент И, четвертый элемент ИЛИ, элемент ИЛИ-НЕ и элемент НЕ, причем выход первого элемента ИЛИ соединен с информационным входом второго регистра сдвига, с первым информационным входом первого коммутатора и первым входом первого элемента И, выход которого подключен к первому входу первого сумматора, выход суммы которого соединен с информационным в.ходом первого регистра сдвига, выход которого подключен к второму входу первого сумматора, выход второго регистра сдвига соединен с первым входом второго элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход третьего регистра сдвига соединен с первым входом третьего элемента И, выход элемента ИЛИ-НЕ блока управления подключен к входу синхронизации схемы сравне шя, выход которой соединен с первым входом четвертого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом сброса первого триггера, выход второго регистра сдвига подключен к входу сброса второго триггера, инверсный выход которого соединен через первый элемент задержки с вторым входом второго элемента И, выход третьего регистра сдвига подключен к входу сброса третьего триггера, инверсный выход которого соединен через второй элемент задержки с вторым входом, третьего элемента И, выход которого подключен к первому 00 4 входу третьего элемента ИЛИ, выход которого соединен с информационным входом третье4 1C го регистра сдвига и вторым информационным входом первого коммутатора, выход которюго подключен к первому информационному входу схемы сравнения, выход пятого элемента И соединен с установочным входом второго триггера, выход которого подключен к второму входу первого элемента ИЛИ, первый выход вторюго коммутатора блока управления соединен с установочным входом первого триггера, прямой выход которого подключен к второму входу первого элемента И и первому входу шестого элемента И, выход которого соединен с установочным входом третьего триггера.

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных устройствах и устройствах дискретной автоматики для вычисления показательной или логарифмической функции.

Известно устройство для логарифмирования двоичных чисел, содержащее два блока памяти, регистры старших и младших разрядов аргумента, три коммутатора, блок деления, сумматор, выходной регистр результата, два буферных регистра, три сдвигателя и блок синхронизации 1 .

Недостатками данного устройства для вычисления логарифмической функции являются сложность реализации и ограниченные функциональные возможности, которые не позволяют вычислять показательную функцию.

Наиболее близким к предлагаемому является функциональный преобразователь, предназначенный для логарифмирования двоичных чисел, содержащий генератор импульсов, три

регистра, три элемента И, ключ и блок управления, а также четыре счетчика, управляемый делитель, реверсивный счетчик и элемент 2И-2ИЛИ. Блок управления устройства содержит три триггера и два одновибратора с соответствующими связями {2.

Недостаток этого устройства заключается в ограниченных функциональных возможностях, которые не позволяют вычислить показательную функцию.

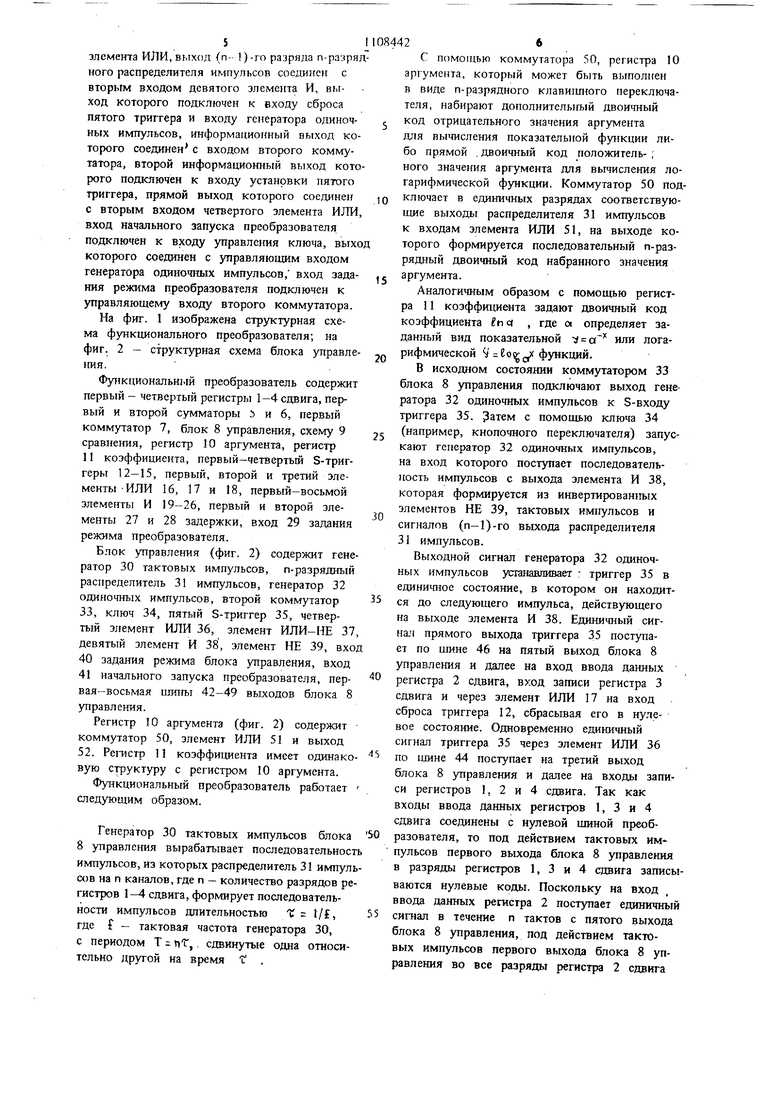

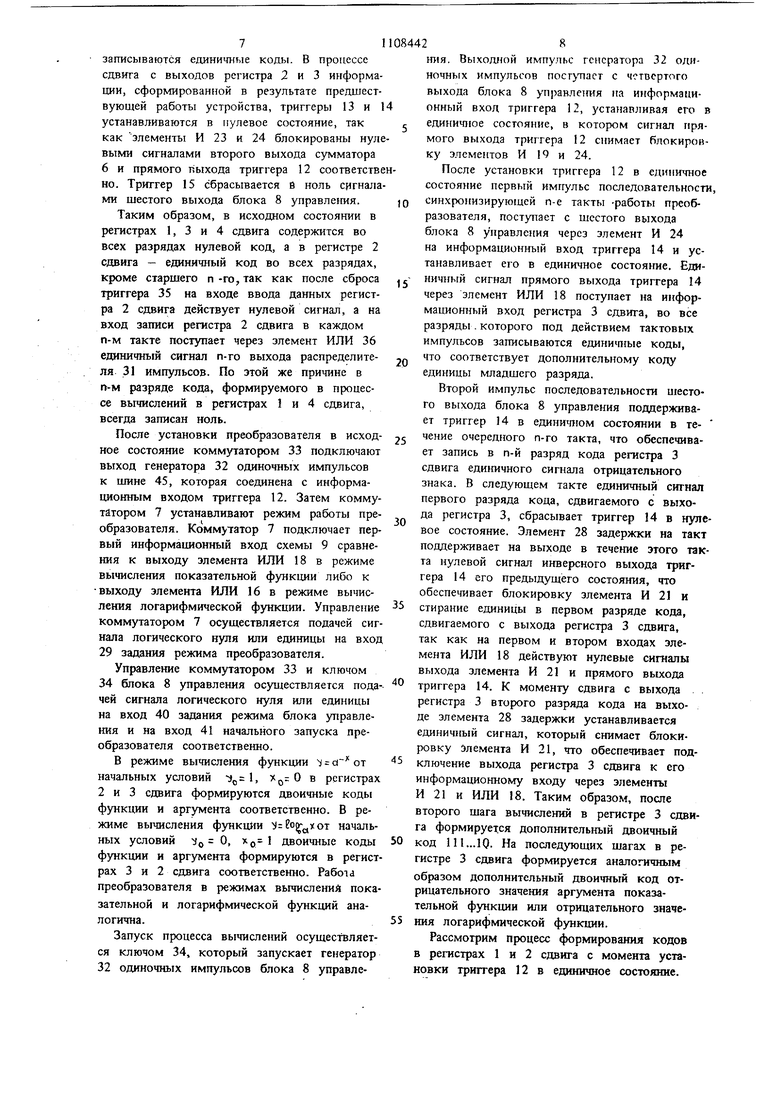

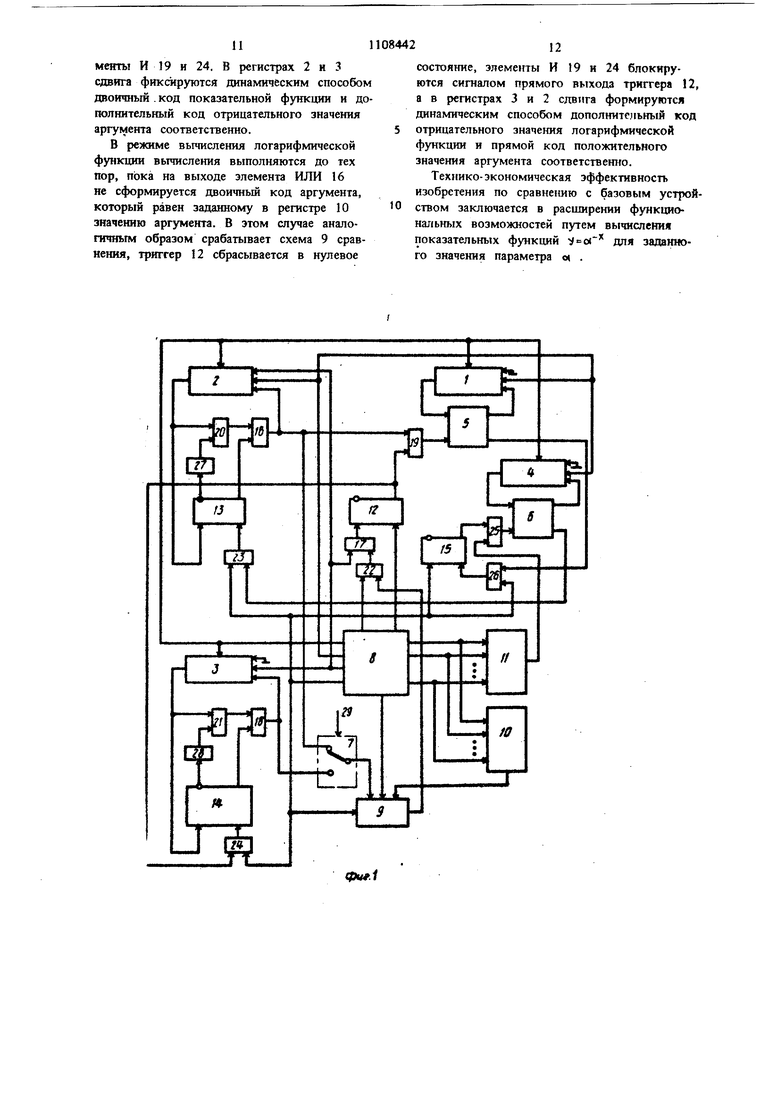

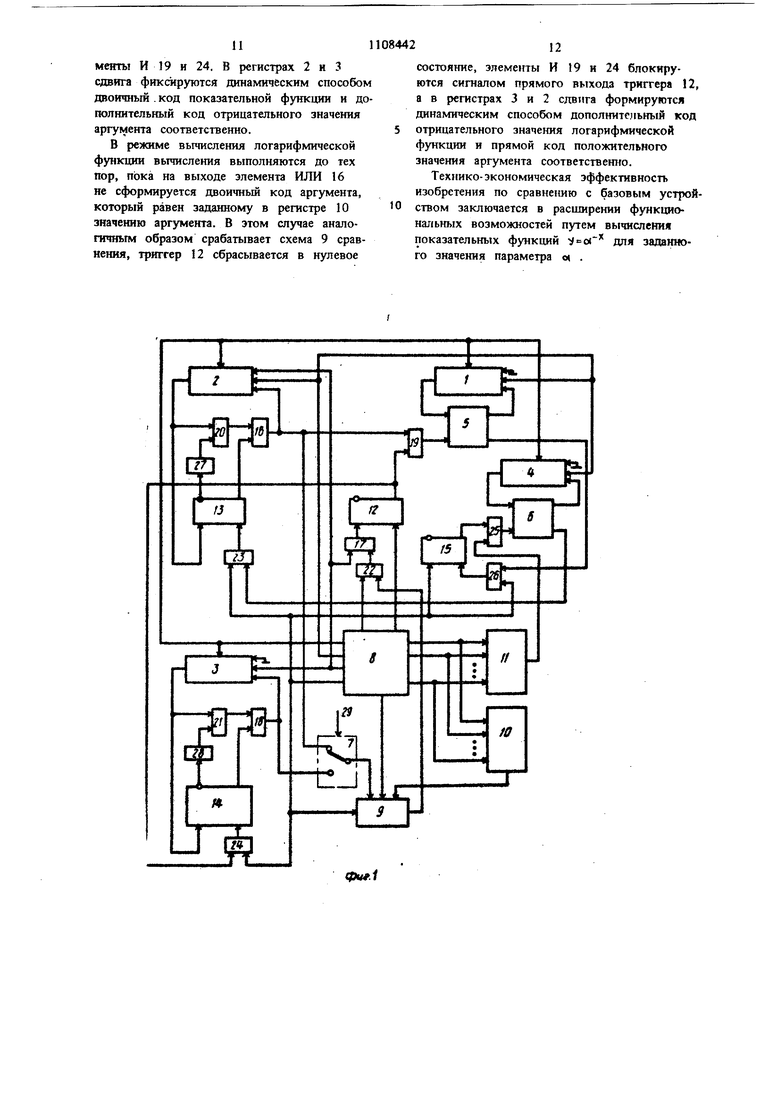

Цель изобретения - расширение функциональных возможностей за счет вычисления как логарифмической, так и показательной функций. Поставленная цель достигается тем, что в преобразователь, содержащий первый, второй и третий регистры сдаига, первый, второй и третий триггеры, первый, второй и третий элементы И и блок управления, состоящий из генератора тактовых импульсов и ключа, причем входы сиихронизации первого, второго и третьего регистров сдвига соединены с выходом генератора тактовых импульсов бло: ка управления, дополнительно введены первый и второй сумматоры, регистр коэффицие та, регистр аргумента, четвертый регистр сдви га, схема сравнения, первый коммутатор, чет вертый триггер, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый, второй и третий элементы ИЛИ, первый и второй элементы задержки, а в блок. управления введены п-разрядный распределитель импульсов, генератор одиночных импульсов, второй коммутатор, пятый триггер, девятый элемент И, четвертый элемент ИЛИ, элемент ИЛИ-НЕ и элемент НЕ, причем выход первого элемента ИЛИ соединен с информационным входом второго регистра сдвига, с первым информационным входом первого коммутатора и первым входом первого элемента И, выход которого подключен к первому входу первого сумматора, выход суммы которого соединен с информационным входом первого регистра сдвига, выход которого подключен к второму входу первого сумматора, выход второго регистра сдвига соединен с первым входом второго элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход третьего регистра сдвига соединен с первым входом третьего элемента И, выход элемента ИЛИ-НЕ блока управления подключен к входу синхронизации схемы сравнения, выход которой соединен с первым входом четвертого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом сброса первого триггера, выход второго регистра сдвига подключен к входу сброса второго триггера, инверсный выход которого соединен через первый элемент задержки с вторым входом второго элемента И, выход треть гого регистра сдвига подключен к входу сбро са третьего триггера, инверсный выход которого соединен через второй элемент задержки с вторым входом третьего элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, выход которого соеди нен с информационным входом третьего регис ра сдвига и вторым информационным входом первого коммутатора, вьосод которого подклю чен к первому информационному входу схемы сравнения, выход пятого элемента И сое динен с установочным входом второго трштера. выход которого подключен к второму входу первого элемента ИЛИ, первый выход второго коммутатора блока управления соединен с установотоым входом первого тригг-ера, прямой выход которого подключен к вторюму входу первого элемента И и первому входу шестого элемента И, выход которого соединен с установочным входом третьего триггера,прямой выход которого подключен к второму входу третьего элемента ИЛИ, группа выходов п-разрядного распределителя импульсов блока управления соединена с соответствуюпшми входами регистров коэффициента и аргумента, выход регистра аргумента подключен к второму информационному входу схему сравнения, выход регистра коэффициента соединен с первым входом седьмого элемента И, выход которого подключен к первому входу второго сумматора, выход суммы которого соединен с информационным входом четвертого регистра сдвига, выход которого подключен к второму входу второго сумматора, выход переноса которого соединен с первым входом пятого элемента И, выход п-го разряда п-раэрядного распределителя импульсов блока управления подключен к вторым входам пятого и шестого элементов И, к входу сброса схемы сравне1гия, к входу сброса четвертого триггера и первому входу восьмого элемента И, выход которого соединен с входом установки четвертого триггера, прямой выход которого подключен к второгиу входу седьмого элемента И, выход четвертого элемента ИЛИ блока ущъ.ъления соединен с входами записи первого, второго и четвертого регистров сдвига, прямой выход пятого триггера блока управления подключен к входу ввода второго регистра сдвига, к второму входу второго элемента ИЛИ и к входу записи третьего регистра сдвига, входы ввода данных первого, третьего и четвертого регистров сдвига соединены с шиной нулевого сигнала преобразователя, выход переноса, первого сумматора подключен к второму входу восьмого элемента И, выход генератора так- . товых импульсов блока управления соединен с входом синхронизации четвертого регистра сдвига, выход девятого элемента И блока управления подключен к второму входу четвертого элемента И, вход задания режима преобразователя соединен с управляющим входом первого коммутатора, причем в блоке управления выход генератора тактовых импульсов соединен через элемент НЕ с первыми входами элементов ИЛИ-НЕ и девятого элемента И и с входом п-разрядного распределителя импульсов, выход п-го разряда которого подключен к второму входу элемента ИЛИ-НЕ и к первому входу четвертого элемента ИЛИ, выход (п- )-го разряда п-разряд ного распределителя импульсов соединен с вторым входом девятого элемента И, выход которого подключен к входу сброса пятого триггера и входу генератора одиночных импульсов, информационный выход которого соединен с входом второго коммутатора, второй информационный выход кото рого подключен к входу установки пятого триггера, прямой выход которого соединен с вторым входом четвертого элемента ИЛИ, вход начального запуска преобразователя подключен к входу управления ключа, выхо которого соединен с управляющим входом генератора одиночных импульсов, вход задания режима преобразователя подключен к управляющему входу второго коммутатора. На фиг. 1 изображена стрзгктурная схема функщ{онального преобразователя; на фиг. 2 - структурная схема блока управлеФункциональный преобразователь содержит первый - четвертый регистры 1-4 сдвига, первый и второй сумматоры Ь и 6, первый коммутатор 7, блок 8 управления, схему 9 сравнения, регистр 10 аргумента, регистр 11 коэффициента, первый-четвертый S-триггеры 12-15, первый, второй и третий элементыИЛИ 16, 17 и 18, первый-восьмой элемертты И 19-26, первый и второй элементы 27 и 28 задержки, вход 29 задания режима преобразователя. Блок управления (фиг. 2) содержит гене ратор 30 тактовых импульсов, п-разрядный распределитель 31 импульсов, генератор 32 одиночных импульсов, второй коммутатор 33, ключ 34, пятый S-триггер 35, четвертый элемент ИЛИ 36, элемент ИЛИ-НЕ 37 девятый элемент И 38, элемент НЕ 39, вхо 40задания режима блока управления, вход 41начального запуска преобразователя, первая-восьмая ШИ1ГЫ 42-49 выходов блока 8 управления. Регистр 10 аргумента (фиг. 2) содержит коммутатор 50, элемент ИЛИ 51 и выход 52. Регистр 11 коэффициента имеет одинако вую структуру с регистром 10 аргумента. Функциональный преобразователь работает следующим образом. Генератор 30 тактовых импульсов блока 8 управления вырабатывает последовательнос импульсов, из которых распределитель 31 импул сов на п каналов, где п - количество разрядов ре гистров 1-4 сдвига, формирует последовательности импульсов длительностью К t/f, где f - тактовая частота генератора 30, с периодом Т - пТ,. сдвинутые одна относительно другой на время t . 2 С п()МО1цью коммутатора 50, регистра 10 аргумерпа, который может быть вьгполнен в виде п-разрядного клавишного переключателя, набирают дополнителыгый двоичный код отрицательного значения аргумента для вычисления показательной функции либо прямой . двоичный код положитель- ; ного значения аргумента для вычисления логарифмической функции. Коммутатор 50 подключает в единичных разрядах соответствующие выходы распределителя 31 импульсов к входам элемента ИЛИ 51, на выходе которого формируется последовательный п-разрядный двоичный код набранного значения аргумента. Аналогичным образом с помощью регистра 11 коэффициента задают двоичный код коэффициента ri с( , где а определяет заданный вид показательной или логарифмической У функций. В исходном состоянии коммутатором 33 блока 8 управления подключают выход гене ратора 32 одиночных импульсов к S-входу триггера 35. Затем с помощью ключа 34 (например, кнопочного переключателя) запускают генератор 32 одиночных имнульсов, на вход которого поступает последовательность импульсов с выхода элемента И 38, которая формируется из инвертирован1п 1х элементов НЕ 39, тактовых импульсов и сигналов (п-1)-го выхода распределителя 31 импульсов. Выходной сигнал генератора 32 одиночных импульсов устанавливает : триггер 35 в единичное состояние, в котором он находится до следующего импульса, действующего на выходе элемента И 38. Единичный сигнал прямого выхода триггера 35 поступает по щине 46 на пятый выход блока 8 управления и далее на вход ввода данных регистра 2 сдвига, вход записи регистра 3 сдвига и через злемент ИЛИ 17 на вход сброса триггера 12, сбрасывая его в нулевое состояние. Одновременно единичный сигнал триггера 35 через элемент ИЛИ 36 по шине 44 поступает на третий выход блока 8 управления и далее на входы записи регистров 1, 2 и 4 сдвига. Так как входы ввода данных регистров 1, 3 и 4 сдвига соединены с нулевой щиной преобразователя, то под действием тактовых им пульсов первого выхода блока 8 управления в разряды регистров 1, 3 и 4 сдвига записываются нулевые коды. Поскольку на вход ввода данных регистра 2 поступает единичный сигнал в течение п тактов с пятого выхода блока 8 управления, под действием тактовых импульсов первого выхода блока 8 управления во все разряды регистра 2 сдвига

записываются единичные коды. В процессе сдвига с выходов регистра 2 и 3 информации, сформированной в результате предшествующей работы устройства, триггеры 13 и 1 устанавливаются в пулевое состояние, так

как элементы И 23 и 24 блокированы нулевыми сигналами второго выхода сумматора 6 и прямого яыхода триггера 12 соответствено. Триггер 15 сбрасывается и ноль сигналами шестого выхода блока 8 управле1гия.

Таким образом, в исходном состоянии в регистрах 1, 3 и 4 сдвига содержится во всех разрядах нулевой код, а в регистре 2 сдвига - единичный код во всех разрядах, кроме старшего п-го, так как после сброса триггера 35 на входе ввода данных регистра 2 сдвига действует нулевой сигнал, а на вход записи регистра 2 сдвига в каждом п-м такте поступает через элемент ИЛИ 36 единичный сигнал п-го выхода распределителя 31 импульсов. По этой же причине в п-м разряде кода, формируемого в процессе вычислений в регистрах 1 и 4 сдвига, всегда записан ноль.

После установки преобразователя в исходное состояние коммутатором 33 подключают выход генератора 32 одиночных импульсов к шине 45, которая соединена с информационным входом триггера 12. Затем коммутатором 7 устанавливают режим работы преобразователя. Коммутатор 7 подключает первый информационный вход схемы 9 сравнения к выходу элемента ИЛИ 18 в режиме вычисления показательной функции либо к выходу элемента ИЛИ 16 в режиме вычисления логарифмической функции. Управление коммутатором 7 осуществляется подачей сигнала логического нуля или единицы на вход 29 задания режима преобразователя.

Управление коммутатором 33 и ключом 34 блока 8 управления осуществляется подачей сигнала логического нуля или единицы на вход 40 задания режима блока управления и на вход 41 начального запуска преобразователя соответственно.

В режиме вычисления функции начальных условий 0 1, о регистрах 2 и 3 сдвига формируются двоичные коды функции и аргумента соответственно. В режиме вычисления функции начальных условий 0 О, Хо 1 двоичные коды функции и аргумента формируются в регистрах 3 и 2 сдвига соответственно. Работа преобразователя в режимах вычислений показательной и логарифмической функций аналогична.

Запуск процесса вычислений осуществляется ключом 34, который запускает генератор 32 одиночных импульсов блока 8 управления. Выходной импульс генератора 32 одиночных импульсов nocr TiacT с четвертого выхода блока 8 управле1шя па информационный вход триггера 12, устанавливая его в единичное состояние, в котором сигнал прямого выхода триггера 12 снимает блокировку элементов И 19 и 24.

После установки триггера 12 в единичное состояние первый имггульс последовательност синхронизирующей п-е такты -работы преобразователя, поступает с шестого выхода блока 8 управления через элемент И 24 на информационный вход триггера 14 и устанавливает его в единичное состояние. Единич1{ый сигнал прямого выхода триггера 14 через элемент ИЛИ 18 поступает на информационный вход регистра 3 сдвига, во все разряды . которого под действием тактовых импульсов записываются единишгые коды, что соответствует дополнителытому коду единицы младшего разряда.

Второй импульс последовательности шестого выхода блока 8 управления поддерживает триггер 14 в единипгом состоянии в течение очередного п-го такта, что обеспечивает запись в п-й разряд кода регистра 3 сдвига еди1шчного сигнала отрицательного знака. В следующем такте единичный сигнал первого разряда кода, сдвигаемого с выхода регистра 3, сбрасывает триггер 14 в нулвое состояние. Элемент 28 задержки на такт поддерживает на выходе в течение этого такта нулевой сигнал инверсного выхода триггера 14 его предыдущего состояния, что обеспечивает блокировку элемента И 21 и стирание единицы в первом разряде кода, сдвигаемого с выхода регистра 3 сдаига, так как на первом и втором входах элемента ИЛИ 18 действуют нулевые сигналы выхода элемента И 21 и прямого выхода триггера 14. К моменту сдвига с выхода . регистра 3 второго разряда кода на выходе элемента 28 задержки устанавливается единичный сигнал, который снимает блокировку Элемента И 21, что обеспечивает подключение выхода регистра 3 сдвига к его информационному входу через элементы И 21 и ИЛИ 18. Таким образом, после второго шага вычислений в регистре 3 сдвига формируется дополнительный двоичный код 111...10. На последующих шагах в регистре 3 сдвига формируется аналогичным образом дополнительный двоичный код отрицательного значения аргумента показательной функции или отрицательного значения логарифмической функции.

Рассмотрим процесс формирования кодов в регистрах 1 и 2 сдвига с момента установки триггера 12 в единичное состояние.

В это время еди гачный сигнал инверсного выхода триггера 13 через элемент 27 задержки на такт действует на втором входе элемента И 20, а на первом входе элемента ИЛИ 16 действует нулевой сигнал прямого выхода триггера 13. Начальный двоичный код 0111...I сдвигается с выхода регистра 2 через элементы И 20 ИЛИ 16 и И 19 на второй вход сумматора 5 и с первого выхода суммы поступает на информационный вход регистра 1 сдвига и запнсьгеается в него за время тактов под действием тактовых импульсов первогэ выхода блока 8 управления. В следующие п тактов (на втором шаге вычислений) на первый вход сумматора 5 с выхода реги :тра 1 сдвигается двоичный код 0111...1, а на второй вход сумматора 5 поступает с выхода регистр 2 сдвига через элементы И 20, ИЛИ 16 и И 19 такой же двоичный код ОП1...1. В результате суммирования последовательным двоичным сумматором 5 на его втором выходе формируется сигнал переноса в п-й разряд, который приведет к срабатыванию элемента И 26 в момент п-го такта. Триггер 15 устанавливается в единичное состояние и поддерживается в нем в течение п тактов.

Последовательный двоичный код коэффициента nd , действующий на выходе регистра 11 коэффициента, в течение п тактов записывается, начиная с младшего разряда, через элемент И 25 и сумматор 6 в регистр 4 сдвига под действием тактовых импульсов первого выхода блока 8 управления. Если на следующем шаге вычислений сигнал переноса в п-й разряд на втором -выходе сумматора 5 отсутствует, триггер 15 возвратится в нулевое состояние сигналом шестого выхода блока 8 управления.

В случае действия сигнала переноса в п-й разряд на втором выходе сумматора 5 триггер 15 сохраняет единичное состояние в течение следующих п тактов и на первом выходе сумматора 6 формируется сумма двоичных кодов, сдвигаемых, начиная с

младшего разряда, с выхода регистра 4 сдвига и с выхода регистра 11 коэффициента. Последовательньш двоичный код суммы с первого вькода сумматора 6 записьгеается в регистр 4 сдвига под действием тактовых импульсов первого выхода блока 8 управления.

Если на втором выходе сумматора 6 формируется сигнал переноса в п-й разряд, то элемент И 23 срабатывает я триггер 13 устанавливается в единичное состояние на п-м

такте rekymero шага вычислений, в котором на входе записи регистров 1, 2 н 4 сдвига

действует импульс с третьего выхода блока 8 управления, блокирующий запись единичного сигнала в п-е разряды кодов регистров 1, 2 и 4 сдвига. Триггер 13 сбрасывается в нулевое состояние единичным сигналом первого разряда кода, сдвигаемого с выхода регистра 2. Элемент 27 задержки на такт поддерживает на выходе в течение такта нулевой сигнал инверсного выхода триггера 13 его предыдущего состояния, что обеспечивает блокировку элемента И 20 во время сдвига первого разряда кода с выхода регистра 2 сдвига. Fla первом и втором входах элемента ИЛИ 16 действуют нулевые сигналы прямого выхода триггера 13 и выхода элемента И 20 соответственно. Нулевой сигнал выхода элемента ИЛИ 16 обеспечивает запись нуля в первом разряде ко- . да, сдвигаемого в регистр 2. К .моменту сдвига с выхода регистра 2 второго разряда кода на выходе элемента 27 задержки устанавливается единичный сигнал, который открывает элемент И 20. Таким образом, остальные разряды кода, начиная с второго разряда, поступают с выхода регистра 2 с;щига на его информационный вход через элементы И 20 и ИЛИ 16 беэ изменения. В регистр 2 сдвига записывается двоишгый код 01 П...10, который также с выхода элемента ИЛИ 16 через элемент И 19 поступает на первый вход сумматора 5, на второй вход которого сдвигается содержимое регистра 1 сдвига. Дальнейшие вычисления выполняются аналогичным образом, причем за время п тактов производится каждый последующий щаг вычислений.

В процессе вычислений на каждом щаге вычислений схема 9 сравнения выполняет сравнение последовательных двоичных кодов, поступающих на ее информационные входы.

8конце каждого шага вычислений схема

9сравнения возвращается в исходное состояние импульсом шестого выхода блока 8 управления.

В режиме вычислений показательной функции вычисления выполняются до тех пор, пока на выходе элемента ИЛИ 18 не сформируется дополнительный последовательный двоичный код аргумента, который равен заданному на коммутаторе 50 регистра 10 значению аргумента. В этом случае срабатьгоает , схема 9 сравнения, на выходе которой формируется единичный сигнал, открьшающий элемент И 22. Импульсный сигнал седьмого выхода блока 8 управления проS ходит через элементы К 22 н ИЛИ 17 на информационный вход триггера 12 и сбрасывает его в нулевое состояние, в котором сигнал его прямого выхода блокирует элементы И 19 и 24. В регистрах 2 и 3 сдвига фиксирутотся дина шческим способо двоичный . код показательной функции и д полнительный код отрицательного значения аргумента соответственно. В режиме вычисления логарифмической функции вычисления выполняются до тех пор, пока на выходе элемента ИЛИ 16 не сформируется двоичный код аргумента, который равен заданному в регистре 10 значению аргумента. В этом случае аналогичным образом срабатывает схема 9 сравнения, триггер 12 сбрасывается в нулевое 12 состояние, элементы И 19 и 24 блокируются сигналом прямого выхода триггера 12, а в регистрах 3 и 2 сдвига формируются динамическим способом дополнительный код отрицательного значения логарифмической функции и прямой код положительного значения аргумента соответственно. Технико- экономическая эффективность изобретения по сравнению с базовым устройством заключается в расширении функциональных возможностей путем вычисления показательных функций для заданного значения параметра о .

«г «4

5/

г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для логарифмирования двоичных чисел | 1978 |

|

SU767755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1983-04-18—Подача