Вх

7Х

Изобретение относится к импульсной технике и может быть использовано пр создании интегральных схем на КМДП- транзисторах.

Цель изобретения - уменьшение потребляемой мощности.

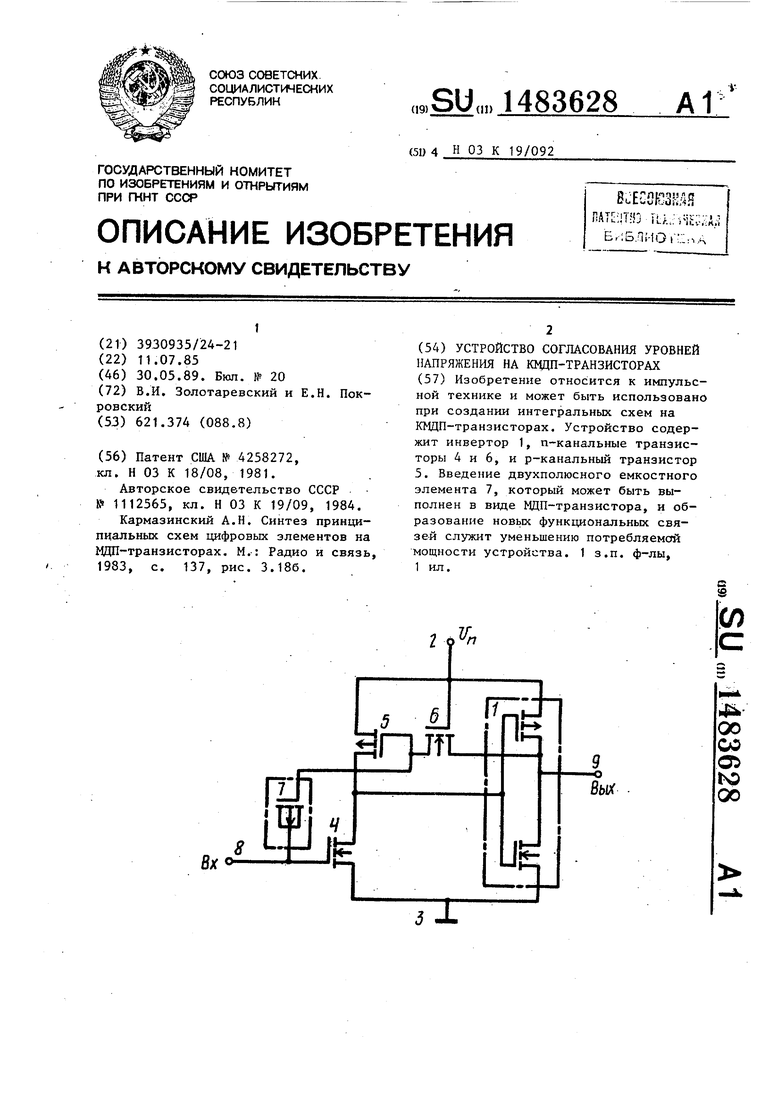

На чертеже представлена электрическая принципиальная схема устройства согласования уровней напряжения н КМДП-транзис торах.

Устройство согласования уровней напряжения содержит выходной инвертор 1, состоящий из n-канального и р-канального транзисторов, включенный между шиной 2 питания и общей шиной 3, первый п-канальный 4 и р-ка- нальный 5 транзисторы, стоки которых соединены и объединены с входом выходного инвертора 1, а истоки подключены соответственна к общей шине 3 и шине 2 питания, второй п-канальный транзистор 6, включенный между затвором р-канального транзистора 5 и выходом выходного инвертора 1, причем затвор второго п-канального транзистора 6 подключен к шине 2 питания, и двухполюсный емкостной элемент 7, включенный между входной шиной 8 и затвором р-канального транзистора 5, при этом затвор первого п.-канального транзистора 4 соединен с входной шиной 8, а выход выходного инвертора 1 соединен с выходной шиной 9.

Устройство работает следующим образом.

Б исходном состоянии на Б.ХОДНОЙ шине 8 устройства находится высокий уровень управляющего напряжения, тогда транзистор 4 открыт, на входе выходного инвертора 1 устанавливается напряжение, близкое к нулю, а на его выходе и, следовательно, на выходной шине 9 - напряжение, близкое к напряжению питания, при этом на затворе транзистора 5 устанавливается напряжение, меньшее напряжения питания на величину порогового напряжения транзистора 6, транзистор 5 закрыт либо очень большое сопротивление (в зависимости от соотношения пороговых напряжений транзисторов 5 и 6), n-канальный транзистор выходного инвертора закрыт и ток от источника питания практически не потребляется.

При переходе входного напряжения от высокого уровня к низкому транзистор 4 закрывается, транзистор 5

0

5

0

5

0

5

0

5

0

5

открывается перепадом напряжения, поступающим на его затвор через емкостной элемент 7, тогда напряжение на входе выходного инвертора 1 стремится к напряжению питания, а на выходной шине 9 - к нулю, через транзистор 6 этот потенциал передается на затвор транзистора 5 и фиксирует последний в открытом состоянии, при этом на выходной шине устанавливается низкий уровень напряжения, транзистор 4 закрыт, р-канальный транзистор выходного инвертора закрыт, ток от источника питания не потребляется.

При переходе напряжения на входной шине 8 от низкого к высокому уровню транзистор 4 открывается, перепад напряжения через емкостной элемент 7 поступает на затвор транзистора 5, что уменьшает проводимость последнего, на входе выходного инвертора напряжение уменьшается и стремится к нулю, а на выходной шине 9 увеличивается и стремится к напряжению питания, при этом на затворе транзистора 5 устанавливается напряжение, меньшее напряжения питания на величину порогового напряжения транзистора 6, проводимость транзистора 5 уменьшается и ток от источника питания практически не потребляется (аналогично исходному состоянию).

Формула, изобретения

1. Устройство согласования уровней напряжения на КМДП-транзисторах, содержащее выходной инвертор, включенный между шиной питания и общей шиной, выход которого соединен с выходной шиной, первый п-канальный транзистор, затвор которого соединен с входной шиной, исток - с общей шиной, а сток - с входом выходного инвертора, р-канальный транзистор, сток которого соединен со стоком первого n-канального транзистора, а исток подключен к шине питания, и второй п-канальный транзистор, отличающееся тем, что, с целью уменьшения потребляемой мощности, в него введен двухполюсный емкостной элемент, включенный между входной шиной и затвором р-канального транзистора, исток второго п-канального транзистора соединен с выходной шиной, сток - с затвором р-канального

514836286

транзистора, а затвор - с шиной пи- ный емкостной элемент выполнен в витания.де мдп-транзистора, сток, исток и

подложка которого объединены и сое2. Устройство по п. 1, о т л и - динены с одним полюсом емкостного чающееся тем, что двухполюс- элемента, а затвор - с другим.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь с тремя состояниями на выходе | 1983 |

|

SU1149399A1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| Формирователь импульсов на МДП-транзисторах | 1985 |

|

SU1569973A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Устройство согласования ттл-схемС Мдп-иНТЕгРАльНыМи СХЕМАМи | 1979 |

|

SU818015A1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

| Тактируемый триггер на комплементарных МДП-транзисторах | 1985 |

|

SU1499435A1 |

Изобретение относится к импульсной технике и может быть использовано при создании интегральных схем на КМДП - транзисторах. Устройство содержит инвертор 1,N - канальные транзисторы 4 и 6 и р - канальный транзистор 5. Введение двухполюсного емкостного элемента 7, который может быть выполнен в виде МДП - транзистора, и образование новых функциональных связей служит уменьшению потребляемой мощности устройства. 1 з. п. ф - лы, 1 ил.

| Патент США № 4258272, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство согласования уровней напряжения | 1983 |

|

SU1112565A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кармазинский А.Н | |||

| Синтез принципиальных схем цифровых элементов на ЩП-транзисторах | |||

| М.: Радио и связь, 1983, с | |||

| Способ приготовления строительного изолирующего материала | 1923 |

|

SU137A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-30—Публикация

1985-07-11—Подача