О) Од 00

Изобретение относится к дискретным устройствам обработки информации и системам синхронизации и предназначено для формирования импульсных последовательностей, синхронных с внешним сигналом.

Цель изобретения - сокращение времени фазирования синхронизирующих последовательностей.

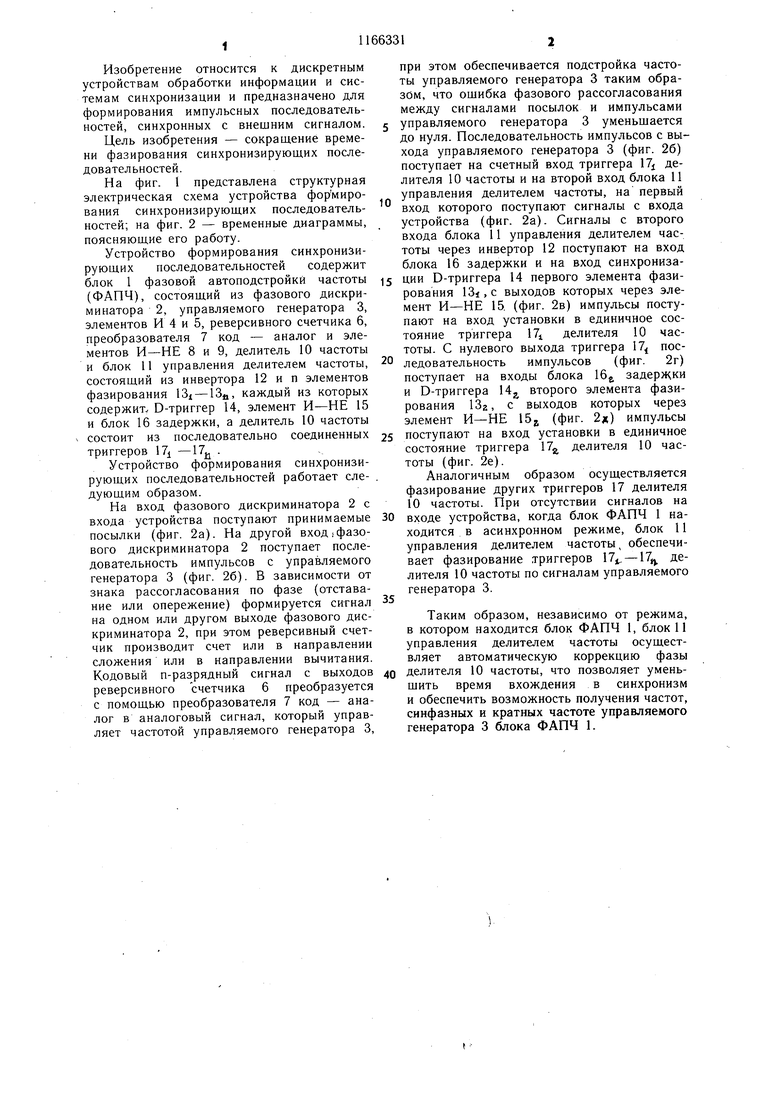

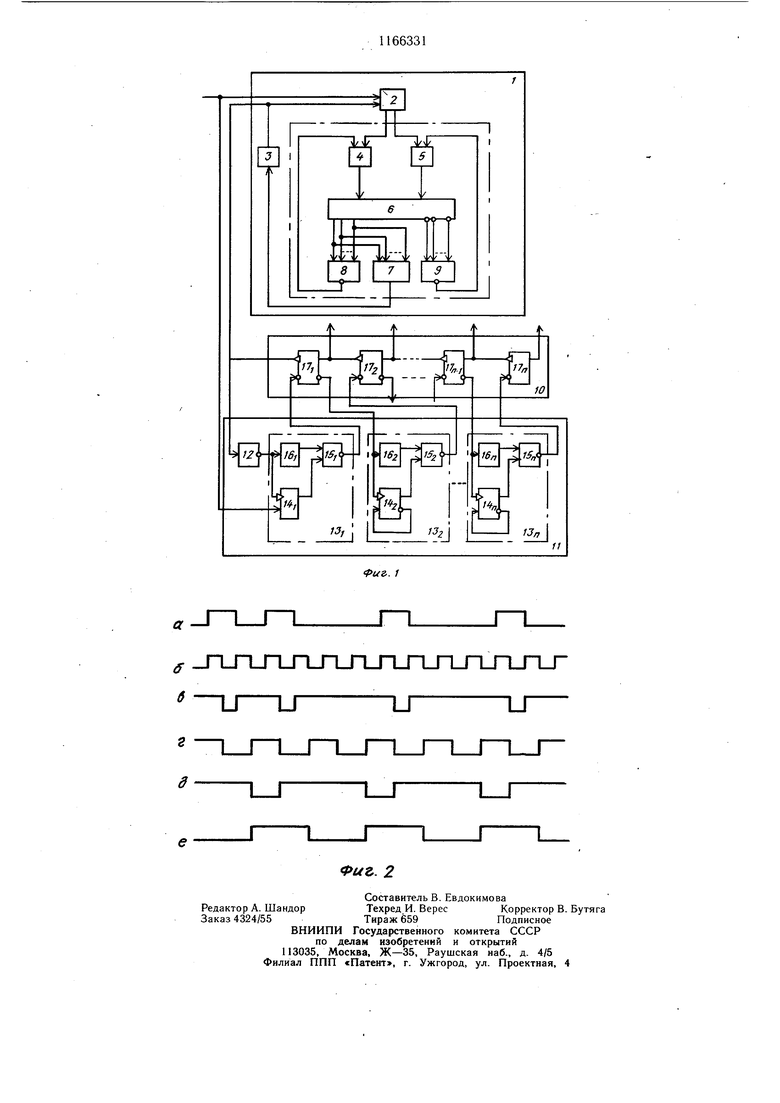

На фиг. 1 представлена структурная электрическая схема устройства формирования синхронизирующих последовательностей; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство формирования синхронизирующих последовательностей содержит блок 1 фазовой автоподстройкй частоты (ФАПЧ), состоящий из фазового дискриминатора 2, управляемого генератора 3, элементов И 4 и 5, реверсивного счетчика 6, преобразователя 7 код - аналог и элементов И-НЕ 8 и 9, делитель 10 частоты и блок 11 управления делителем частоты, состоящий из инвертора 12 и п элементов фазирования 13i - 13и, каждый из которых содержит D-триггер 14, элемент И-НЕ 15 и блок 16 задержки, а делитель 10 частоты состоит из последовательно соединенных триггеров 7i -17 Устройство формирования синхронизирующих последовательностей работает следующим образом.

На вход фазового дискриминатора 2 с входа устройства поступают принимаемые посылки (фиг. 2а). На другой вход..фазового дискриминатора 2 поступает последовательность импульсов с управляемого генератора 3 (фиг. 26). В зависимости от знака рассогласования по фазе (отставание или опережение) формируется сигнал на одном или другом выходе фазового дискриминатора 2, при этом реверсивный счетчик производит счет или в направлении сложения или в направлении вычитания. Кодовый п-разрядный сигнал с выходов реверсивного счетчика 6 преобразуется с помощью преобразователя 7 код - аналог в аналоговый сигнал, который управляет частотой управляемого генератора 3,

при этом обеспечивается подстройка частоты управляемого генератора 3 таким образом, что ощибка фазового рассогласования между сигналами посылок и импульсами управляемого генератора 3 уменьщается до нуля. Последовательность импульсов с выхода управляемого генератора 3 (фиг. 26) поступает на счетный вход триггера 17 делителя 10 частоты и на второй вход блока 11 управления делителем частоты, на первый вход которого поступают сигналы с входа устройства (фиг. 2а). Сигналы с второго входа блока 11 управления делителем частоты через инвертор 12 поступают на вход блока 16 задержки и на вход синхронизации D-триггера 14 первого элемента фазирования 13i. с выходов которых через элемент И-НЕ 15. (фиг. 2в) импульсы поступают на вход установки в единичное состояние триггера 17 делителя 10 частоты. С нулевого выхода триггера 17 последовательность импульсов (фиг. 2г) поступает на входы блока 16 задержки и D-триггера 14 второго элемента фазирования 13г, с выходов которых через элемент И-НЕ 15 (фиг. 2д) импульсы

5 поступают на вход установки в единичное состояние триггера 17 делителя 10 частоты (фиг. 2е).

Аналогичным образом осуществляется фазирование других триггеров 17 делителя 10 частоты. При отсутствии сигналов на

0 входе устройства, когда блок ФАПЧ 1 находится в асинхронном режиме, блок 11 управления делителем частоты, обеспечивает фазирование триггеров 17. - 17j делителя 10 частоты по сигналам управляемого генератора 3.

Таким образом, независимо от режима, в котором находится блок ФАПЧ 1, блок 11 управления делителем частоты осуществляет автоматическую коррекцию фазы делителя 10 частоты, что позволяет уменьщить время вхождения в синхронизм и обеспечить возможность получения частот, синфазных и кратных частоте управляемого генератора 3 блока ФАПЧ 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство дискретной фазовой автоподстройки частоты | 1980 |

|

SU866771A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Устройство для восстановления информации | 1988 |

|

SU1561098A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1774497A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1983 |

|

SU1138946A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1990 |

|

SU1714817A1 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

УСТРОЙСТВО ФОРМИРОВАНИЯ СИНХРОНИЗИРУЮЩИХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащее блок фазовой автоподстройки частоты, вход которого объединен с первым входом блока управления делителем частоты и является входом устройства, а выход блока фазовой автоподстройки частоты подключен к счетному входу делителя частоты, выполненного в виде п последовательно соединенных триггеров, отличающееся тем, что, с целью сокращения времени фазирования синхронизирующих последовательностей, блок управления делителем частоты выполнен в виде инвертора и п элементов фазирования, каждый из которых состоит из объединенных по входу D-триггера и блока задержки, выходы которых подключены к соответствующим входам элемента И-НЕ, причем счетный вход делителя частоты объединен с входом элемента НЕ, выход которого подключен к входу первого элемента фазирования, единичный вход D-триггера которого является первым входом блока управления делителем частоты, выход каждого элемента фазирования подключен к входу установки «1 соответствующего триггера делителя частоты, нулевой выход с S которого подключен к входу последующего элемента фазирования, кроме того, в каж(Л дом элементе фазирования, кроме первого, нулевой выход D-триггера объединен с с единичным входом.

| Устройство дискретного фазирования | 1979 |

|

SU803115A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИНХРОНИЗИРУЮЩИХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 0 |

|

SU321960A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-07-07—Публикация

1982-11-03—Подача