., и

Ийобр зтение относится к вычислительной технике и может быть использовано при изготовлении ззпоминаюuiMx устройств на oaibse транзисторов МДП, в маетности МИОП-типа (металлнитрид кремния-двуокись кремния-кремиий).

изобретения является увеличение времени хранения информации элемента г(амяти.

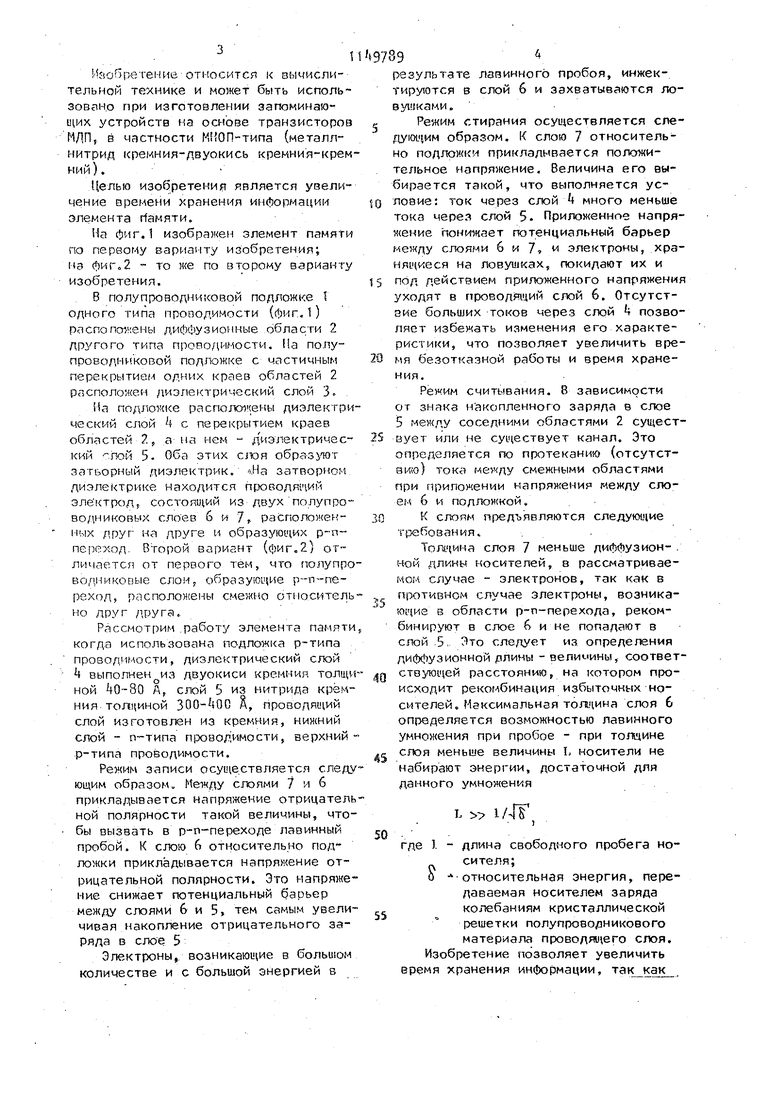

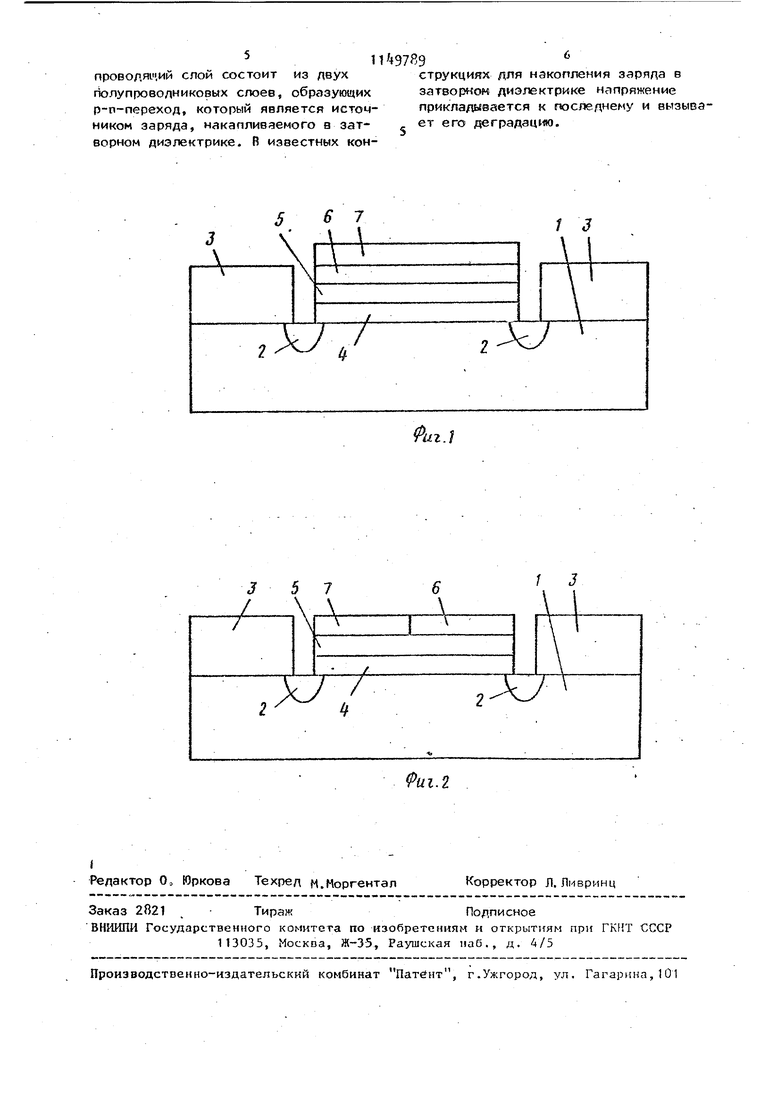

i-ia фиг.1 изображен элемент памяти по первому варианту изобретения; нз фиг,2 - то же по е тррому варианту изобретения.

В полупроводниковой подложке I одного типа проводимости (фиг.1) распоптнены диффузионные области 2 другого типа проводимости. На полупроводниковой подложке с частичным перекрытием одних краев областей 2 расположен диэлектрический слой 3. .

iSa подложке расположены диэлектрический слой 4 с перекрытием краев областей . 5 ana нем - Диэлектрический глой 5. Оба этих образ WT затьорный диэлектрик. «На затворном диэлектрике находится проводящий электрод состопи ий из двухполупроводниковых слоев б и 7 г раСположен1-1ЫХ друг на друге и образую{.цих р-ппереход. Второй вариант (фиг.2) от личается от первого тем, что полупровогичиковые слоМр образую1цие р-п-переход, расположены смежно относительно друг друга.

Рассмотрим .работу элемента памяти когда использована подложка р-типа проводимости, диэлектрический слой 4 выполнен из двуокиси креииия толщиной tO-SO А, слой 5 из нитрида кремния толциной А, проводящий слой изготовлен из кремния, нижний слой - п-типа проводимости, верхнийр-типа проводимости.

Режим записи осуще.ствляется следу ющим образом. Неткду cJDЯми 7 м б прикладывается напряжение отрицательной полярности такой величины, чтобы вызвать в р-п-переходе лавинный пробой. К слою 6 относительно подложки прикладывается напряжение отрицательной полярности. Это напряжение снижает потенциальный Оарьер между слоями & и 5, тем самым увеличивая накопление отрицательного заряда в слое 5

Электроны, возникающие в большом количестве и с большой энергией в

9

результате ла зинного пробоя, инжектиру отся в слой 6 и захватываются ловушками.

Решим стирания осуществляется следущим образом, К слою 7 относительно подложки прикладывается положительное напряжение. Величина его выбирается такой, что выполняется условие: ток через слой много меньше тока через слой 5. Приложенное напряжение понижает потенциальный барьер между слоями 6 и 7, « электроны, храняу иеся на ловушках, покидают их и

пОд действием приложенного напряжения уходят 8 проводящий слой 6. Отсутствие больших токов через слой k позволяет избежать изменения его характе ристики, что позволяет увеличить безотказной работы и время хранения.

Режим считывания. 8 зависимости от знака накопленного заряда в слое 5 между соседними областями 2 существует или не су1цествует канал. Это определяется по протеканию (отсутствию) тока между смежными областями при приложении напряжения между слоен 6 и подложкой.

слоям предъявляются следуккцие

требования...

слоя 7 меньше диффузион- . ной длины носителей, в рассматриваеMOI4 случае - электронов, так как в

п(Х)тивном случае электроны, возникающие в области р-п-перехода, рекомбинируют в слое б и не попадают в слой -5, Это следует из определения диф()узионной длины - вели1ины, соответствующей расстоянию, на котором происходит рекомбинация избыточных носителей. 1аксимальная тощина слоя 6 определяется возможностью лавинного умножения при пробое - при толщине

слоя меньше величины L носители не набирают энергии, достаточной для данного умножения

L

где 1 - длина свободного пробега носителя;

6 -относительная энергия, передаваемая носителем заряда колебаниям кристаллической решетки полупроводникового материала проводящего слоя. Изобретение позволяет увеличить время хранения информации, так как

проводя1.ии слои состоит из двух гюлупроволниковых слоев, образующих р-п-переход, который является источником заряда, накапливаемого в затворном диэлектрике. В известных конструкциях для накопления заряда в затворном диэлектрике напряжение прикладывается к гюследнему и вызывает его деградацию.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти для постоянного запоминающего устройства | 1982 |

|

SU1124762A1 |

| Элемент памяти для постоянного запоминающего устройства | 1984 |

|

SU1159447A1 |

| Способ изготовления интегральных схем памяти на основе МНОП-транзисторов | 1982 |

|

SU1040978A1 |

| Ячейка памяти | 1978 |

|

SU752476A1 |

| Способ изготовления полевых транзисторов | 1982 |

|

SU1085437A1 |

| Способ изготовления матричного накопителя для постоянного запоминающего устройства | 1989 |

|

SU1607621A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444891A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444890A1 |

| ЛАВИННЫЙ ФОТОДЕТЕКТОР | 1991 |

|

SU1823725A1 |

1. Элемент памяти для постоянного запоминакнцёго устройства, содержащий полупроводниковую подложку первого типа провод 1ости, в приповерхностном слое которой расположены лиффузиониые области второго типа проводимости на поверхности полупроводниковой подложки размещены диэлектрические области с частичным перекрытием одних краев диффузионных областей второго типа проводимости, на поверхности полупроводниковой подложки между диэлектрическими областями последовательно размещены первый и второй диэлектрические слои с частичным перекрытием других краев диффузионных областей, на поверхности второго диэлектрического слоя расположен проводячий слой, о т л и ч. а ю щ и и с я тем, что, с целыо увеличения времени хранения информации, проводящий слой выполнен из двух послеловательно расположенных полупроводниковых слоев, образую1цих р-п-переход, причем толчина слоя, примыкающего к второму диэлектрическому слою, менее диффузионной длины носителей, но более L, равной где 1 длина свободного пробега, S - относительная энергия, передаваемая носителем заряда колебаниям кристаллической решетки полупроводникового материала проводя1чего слоя. 2, Элемент памяти для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого типа проводимости, в приповерхностном слое которой расположены диффузионные области второго типа проводимости, на поверхности полупроводниковой подложки размещены диэлектрические области с частичным перекрытием одних краев диффузионных областей второго типа проводимости, на поверхности полупроводниковой подложки межсл ду диэлектрическими областями послес довательно размещены первый и второй диэлектрические слои с частичным перекрытием других краев диффузионных областей, на поверхности второго диэлектрического слоя расположен прово-, дящий слой, отличающийся тем, что, с целью увеличения времени 4 О хранения информации, проводяций слой выполнен из двух смежно располоVJ женных полупроводниковых слоев, обра00 Ю зующих р-п-переход, причем толцина слоев, привыкающих к второму диэлектрическому слою, менее диффузионной длины носителей, но более L, равной где 1 - длина свободного пробега носителей, и - относительная энергия, передаваемая носителем заряда колебаниям кристаллической решетки полупроводникового материала проводящего слоя.

иг.1

И1.2

Авторы

Даты

1992-07-15—Публикация

1983-06-15—Подача