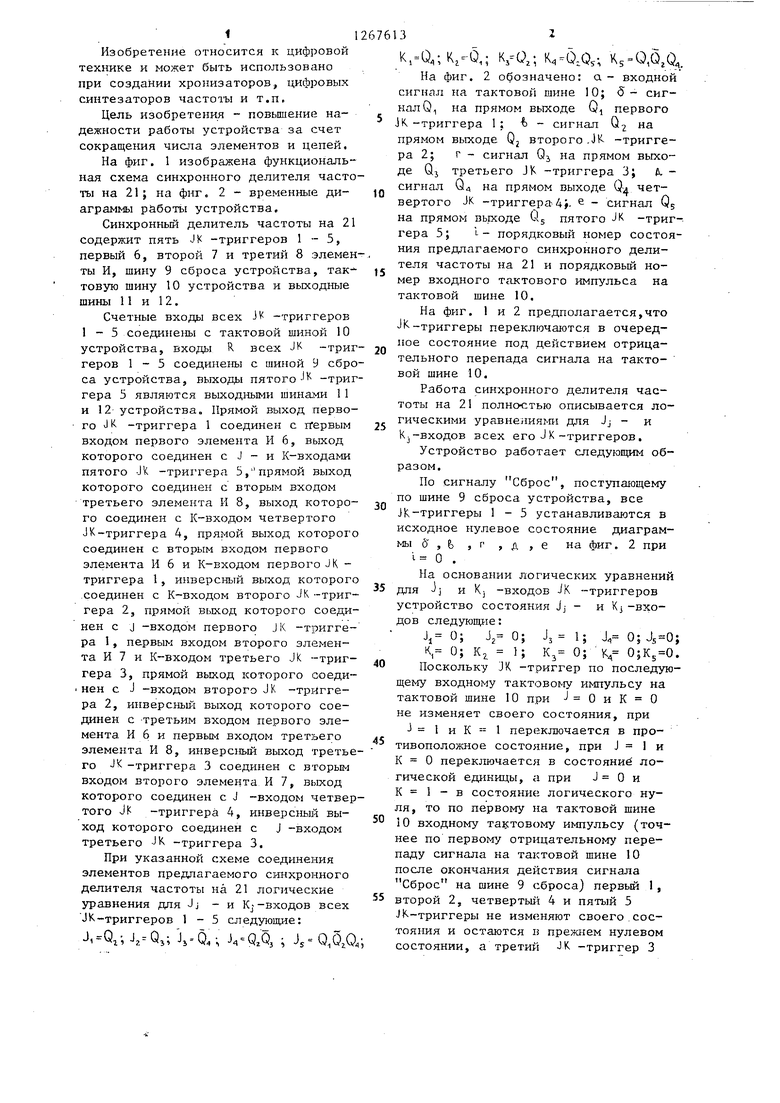

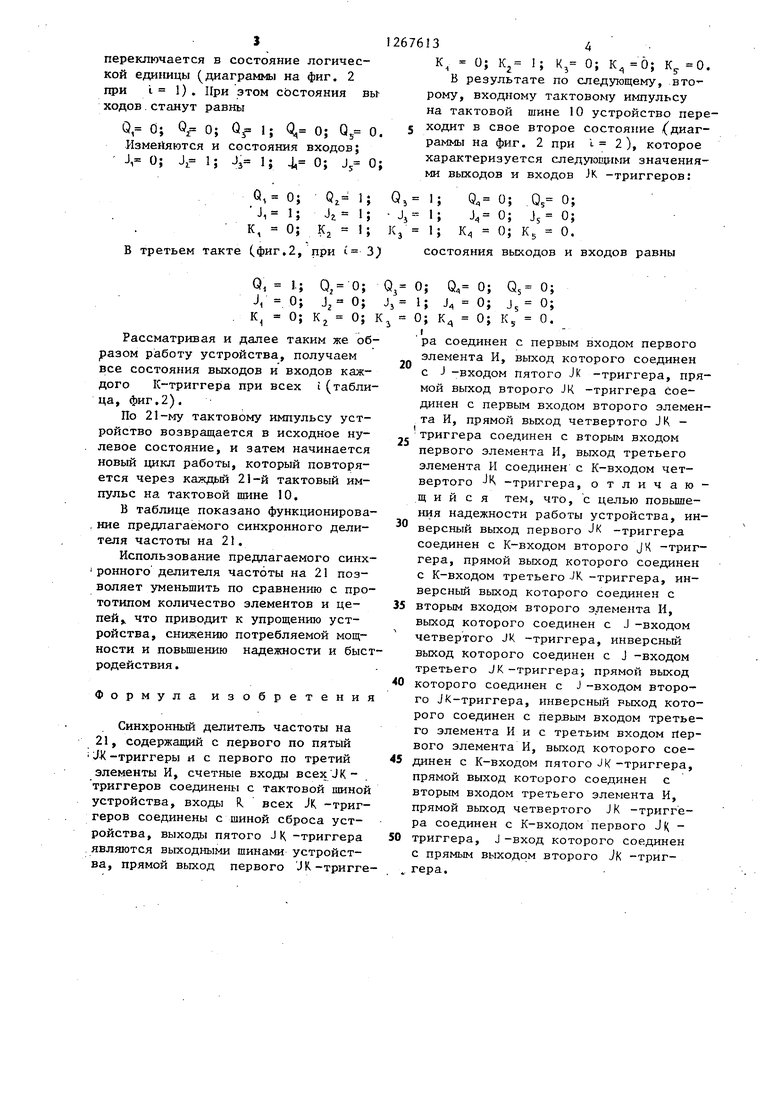

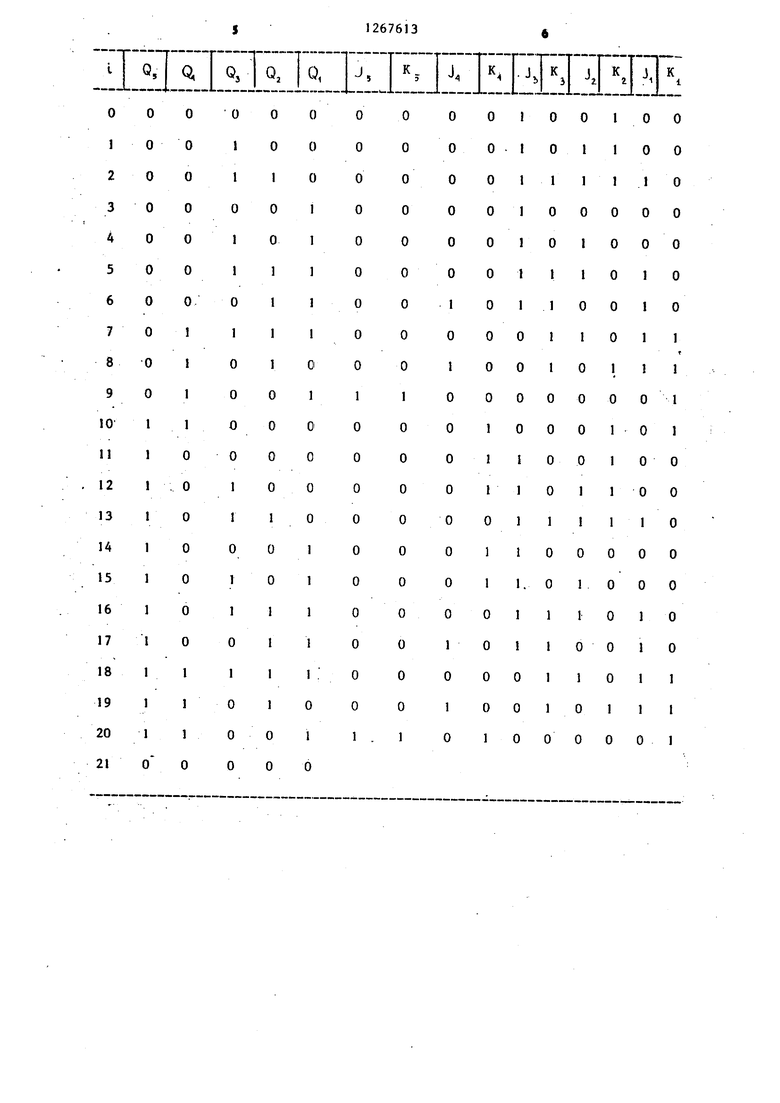

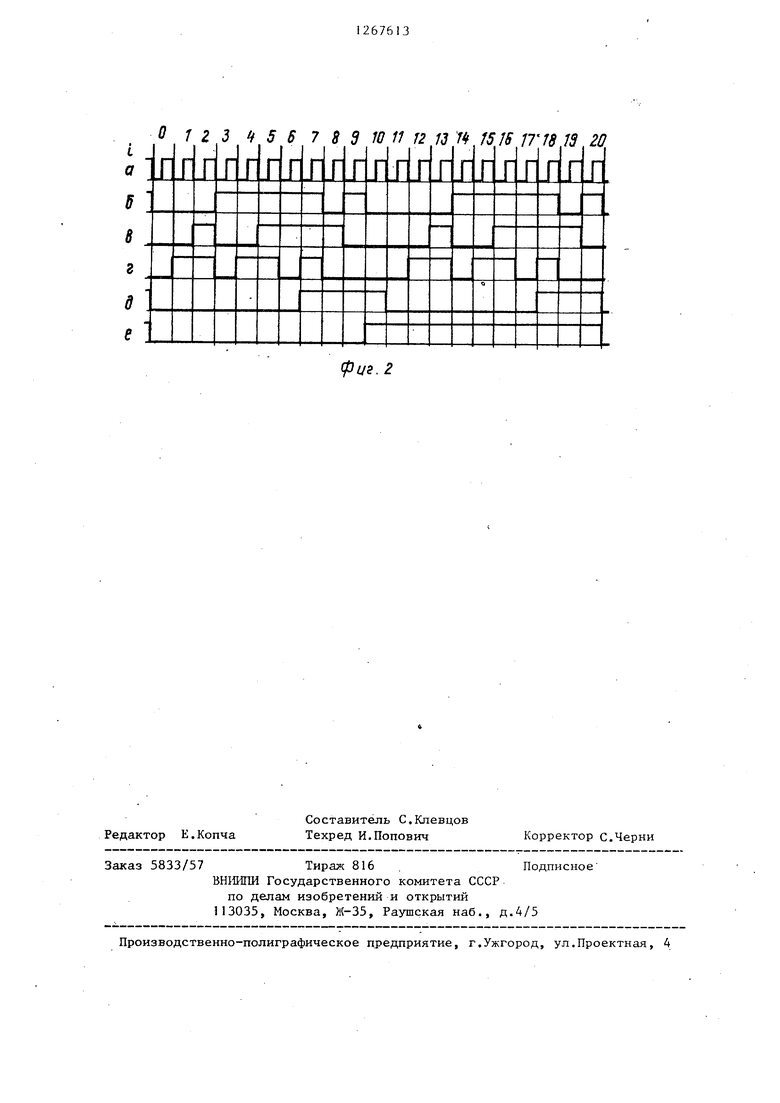

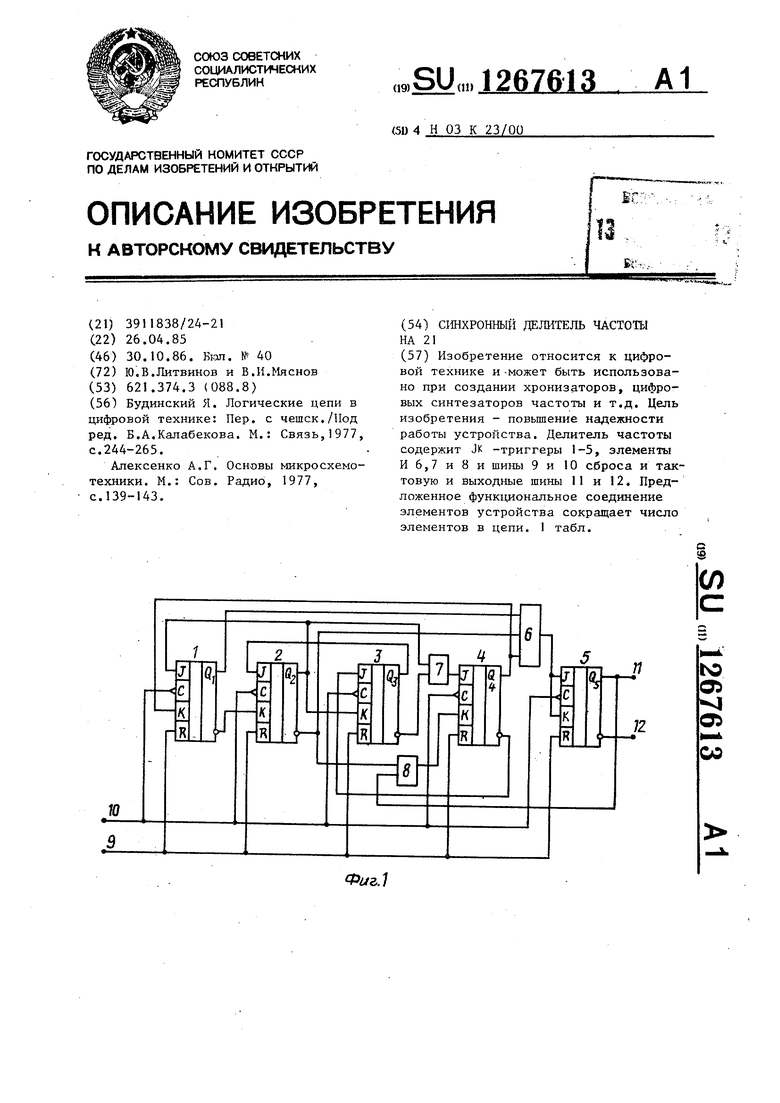

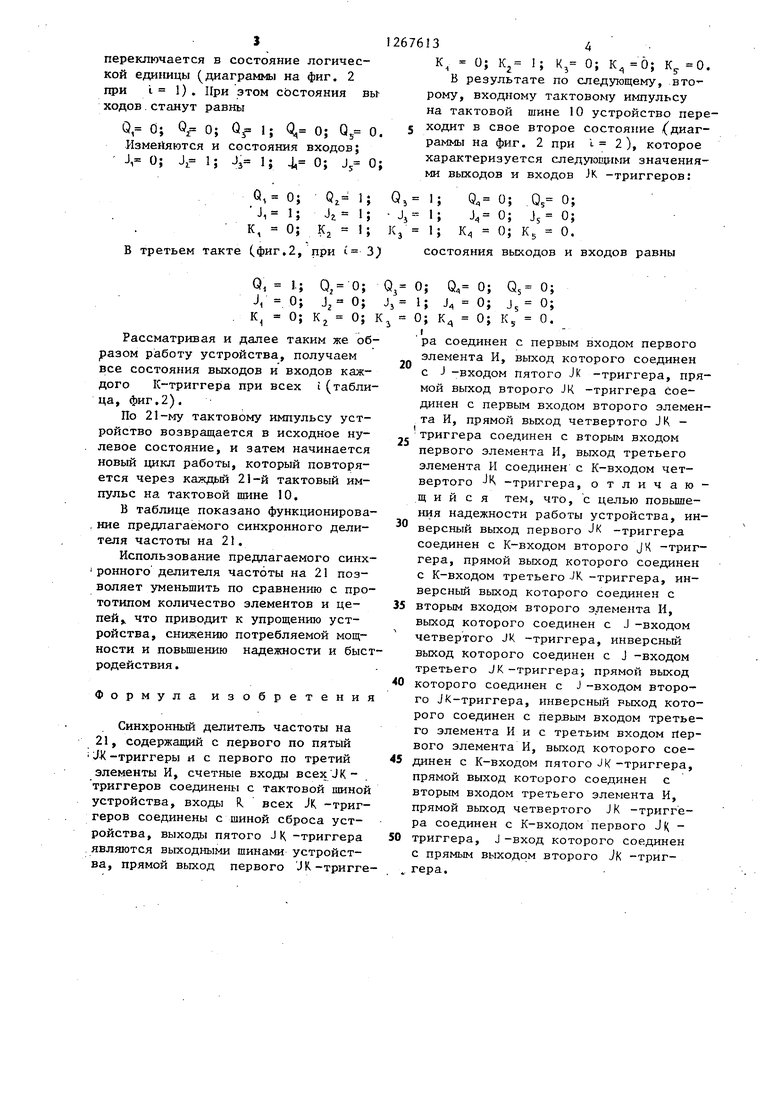

Фиг.1 Изобретение относится к цифровой технике и может быть использовано при создании хронизаторов, цифровых синтезаторов частота и т.п. Цель изобретения - повьшенисг надежности работы устройства за счет сокращения числа элементов и ц(гпей. На фиг. 1 изображена функциональная схема синхронного делителя часто ты на 21; на фиг. 2 - временные диаграммы работы устройства. Синхронный делитель частоты на 21 содержит пять JK -триггеров 1 - 5, первый 6, второй 7 и третий 8 элемен ты И, шину 9 сброса устройства, так- товую шину 10 устройства и выходные шины 11 и 12. Счетные входы всех -триггеров 1 - 5 соединены с тактовой шиной 10 устройства, входы R всех JK -триг геров 1 - 5 соедине1ш с шиной У сбро са устройства, выходы пятого гера 5 являются выходными шина:ми 1 1 и 12- устройства. Прямой выход первого J -триггера 1 соединен с тгервым входом первого элемента И 6, выход которого соединен с J - и К-входами пятого Jlf -триггера 5,прямой выход которого соединен с вторым входом третьего элемента И 8, выход которого соединен с К-входом четвертого JК-триггера 4, прямой выход которог соединен с вторым входом первого элемента И 6 и К-входом первого JK триггера 1, инверсный вьгход которог .соединен с К-входом второго JK-триг гера 2, прямой которого соеди нен с J -входом первого JK -триггера 1, первым входом второго элемента И 7 и К-входом третьего JK -триггера 3, прямой выход которого ооедииен с J -входом второго JK -триггера 2, инверсный выход которого соединен с -третьим входом первого элемента И 6 и первым входом третьего элемента И 8, инверсный выход третье го J -триггера 3 соединен с вторым входом второго элемента И 7, выход которого соединен с J -входом четвер того JK -триггера 4, инверсный выход которого соединен с J -входом третьего - -триггера 3. При указанной схеме соединения элементов предлагаемого синхронного делителя частоты на 21 логические уравнения для Jj - и Kj-входов всех иК-триггеров 1 - 5 следующие: J,Q,; J,.Q,; J,.Q,. J, Q,Q ; J K, Q.;K,-Q,; K,Q,; K,Q,0,; Ks 0,QA Ha фиг. 2 обозначено: a- входной сигнал на тактовой шине 10; S- сигнал Q, на прямом выходе 0 первого K -триггера 1 ; Ь - сигнал Gt2 на прямом выходе Qj второго ,JH- -триггера 2; г - сигнал QJ на прямом выходе QJ третьего JK -триггера 3; д, сигнал QA на прямом выходе Q четвертого 1К -триггера - сигнгш QS на прямом вьщоде QS пятого J -триг-. гера 5; L- порядковый номер состояния предлагаемого синхронного делителя частоты на 21 и порядковый номер входного тактового импульса на тактовой шине 10. На фиг. 1 и 2 предполагается,что JK-триггеры переключаются в очередное состояние под действием отрицательного перепада сигнала на тактовой шине 10. Работа синхронного делителя частоты на 21 полностью описывается логическими уравнениями для Jj - и kj-входов всех егоJК-триггеров, Устройство работает следующим образом. По сигнапу Сброс, поступающему по шине 9 сброса устройства, все JК-триггеры 1 - 5 устанавливаются в исходное нулевое состояние диаграммы 6 , Ь , г , д , е на фиг. 2 при О . На основании логических уравнений для -)j и Kj -входов JK -триггеров устройство состояния Jj - и Kj-входов следующие: Ji 0; Jj 0; 3 1; Л 0; К, 0; К 1; К 0; К . Поскольку JK -триггер по последующему входному тактовому импульсу на тактовой шине 10 при - О и К О не изменяет своего состояния, при J 1 и К 1 переключается в противоположное состояние, при J 1 и К О переключается в состояние логической единицы, а при J О и К 1 - в состояние логического нуля, то по первому на тактовой шине 10 входному TaijTOBOMy импульсу (точнее по первому отрицательному перепаду сигнала на тактовой шине 10 после окончания действия сигнала Сброс на шине 9 сброса) первый 1, второй 2, четвертый 4 и пятый 5 JK-триггеры не изменяют своего,состояния и остаются в прежнем нулевом состоянии, а третий JK -триггер 3 переключается в состояние логической еди1шцы (диаграммы на фиг. 2 при I 1). При этом состояния вы ходов.станут равны й, 0; 0 0; Q,f 1; 0, 0; 0 0. Изменяются и состояния входов; J, 0; 4 1; J3 1; 4, 0; J, 0; Q. 0; J, 1; К, 0; в третьем такте (фиг.2, при i 3) Qi 1; Q, 0; J, . 0; J,- 0; . K, 0; K, 0; Рассматривая и далее таким же об разом работу устройства, получаем все состояния выходов и входов каждого К-триггера при всех i(табли ца, фиг.2). По 21-му тактовому импульсу устройство возвращается в исходное нулевое состояние, и затем начинается новый цикл работы, который повторяется через каждый 21-й тактовый импульс на тактовой шине 10. В таблице показано функционирова , ние предлагаемого синхронного делителя частоты на 21. Использование предлагаемого синх ронного делителя частоты на 21 позволяет уменьшить по сравнению с про тотипом количество элементов и цепей,, что приводит к упрощению устройства, снижению потребляемой мощности и повышению надежности и быс родействия . Формула изобретени Синхронный делитель частоты на 21, содержащий с первого по пятый JX -триггеры и с первого по третий элементы И, счетные входы всех JК триггеров соединены с тактовой шиной устройства, входы R. всех JK, -триггеров соединены с шиной сброса устройства, выходы пятого J К -триггера являются выходными шинами устройства, прямой выход первого JK-TpHrre 12676 5 Q, - Jj Kj 134 К 0; К 1; К, 0; К 0; К 0. В результате по следующему, второму, входному тактовому импульсу на тактовой шине 10 устройство переходит в свое второе состояние .(диаграммы на фиг. 2 при 1 2), которое характеризуется следующими значениями выходов и входов JK -триггеров: 1; Q 0; Os 0; 1; J. 0; J5 0; 1; K 0; Kg 0. состояния выходов и входов равны ; Q, 0; Q5 0; 1; J, 0; j, 0; ; K 0; KJ 0. ,1 pa соединен с первым входом первого элемента И, выход которого соединен с J -входом Пятого J -триггера, прямой выход второго JK -триггера соединен с первым входом второго элемента И, прямой выход четвертого JK триггера соединен с вторым входом первого элемента И, выход третьего элемента И соединен с К-входом четвертого JK -триггера, отличающий с я тем, что, с целью повьшения надежности работы устройства, инверсный выход первого J -триггера соединен с К-входом второго JK -триггера, прямой выход которого соединен с К-входом третьего JK -триггера, инверсный выход которого соединен с вторым входом второго элемента И, выход которого соединен с J -входом четвертого JK -триггера, инверсный выход которого соединен с J -входом третьего JK -триггера; прямой выход которого соединен с J-входом второго JК-триггера, инверсный выход которого соединен с первым входом третьего элемента И и с третьим входом Первого элемента И, выход которого соединен с К-входом пятого JK -триггера, прямой выход которого соединен с вторым входом третьего элемента И, прямой выход четвертого JK -триггера соединен с К-входом первого JK триггера, J-вход которого соединен с прямым выходом второго JK -триггера.

а В S г

е

ffJus,2

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты с четным коэффициентом деления | 1987 |

|

SU1629990A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Синхронный делитель частоты на 14 | 1985 |

|

SU1243130A1 |

| Синхронный делитель частоты на 9 на JK-триггерах | 1987 |

|

SU1444938A1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Синхронный делитель частоты | 1986 |

|

SU1385291A1 |

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| Синхронный делитель на 12 | 1987 |

|

SU1517129A1 |

| Делитель частоты на 19 | 1984 |

|

SU1226660A1 |

| Синхронный делитель частоты | 1987 |

|

SU1431066A1 |

Изобретение относится к цифровой технике и -может быть использовано при создании хронизаторов, цифровых синтезаторов частоты и т.д. Цель изобретения - повьшение надежности работы устройства. Делитель частоты содержит JK -триггеры 1-5, элементы И 6,7 и 8 и шины 9 и 10 сброса и тактовую и выходные шины 11 и 12. Предложенное функ1Ц1ональное соединение элементов устройства сокращает число элементов в цепи. I табл.

| Будинский Я | |||

| Логические цепи в цифровой технике: Пер | |||

| с чешек./Иод ред | |||

| Б.А.Калабекова | |||

| М.: Связь,1977, с.244-265 | |||

| Алексенко А.Г | |||

| Основы микросхемотехники | |||

| М.: Сов | |||

| Радио, 1977, с.139-143. |

Авторы

Даты

1986-10-30—Публикация

1985-04-26—Подача