f

Изобретение относится к цифровой технике и может быть использовано, например, при построении цифровых синтезаторов частоты.

Целью изобретения является повы- шение надежности работы устройства за счет снижения числа элементов и цепей при одновременном повышении быстродействия,

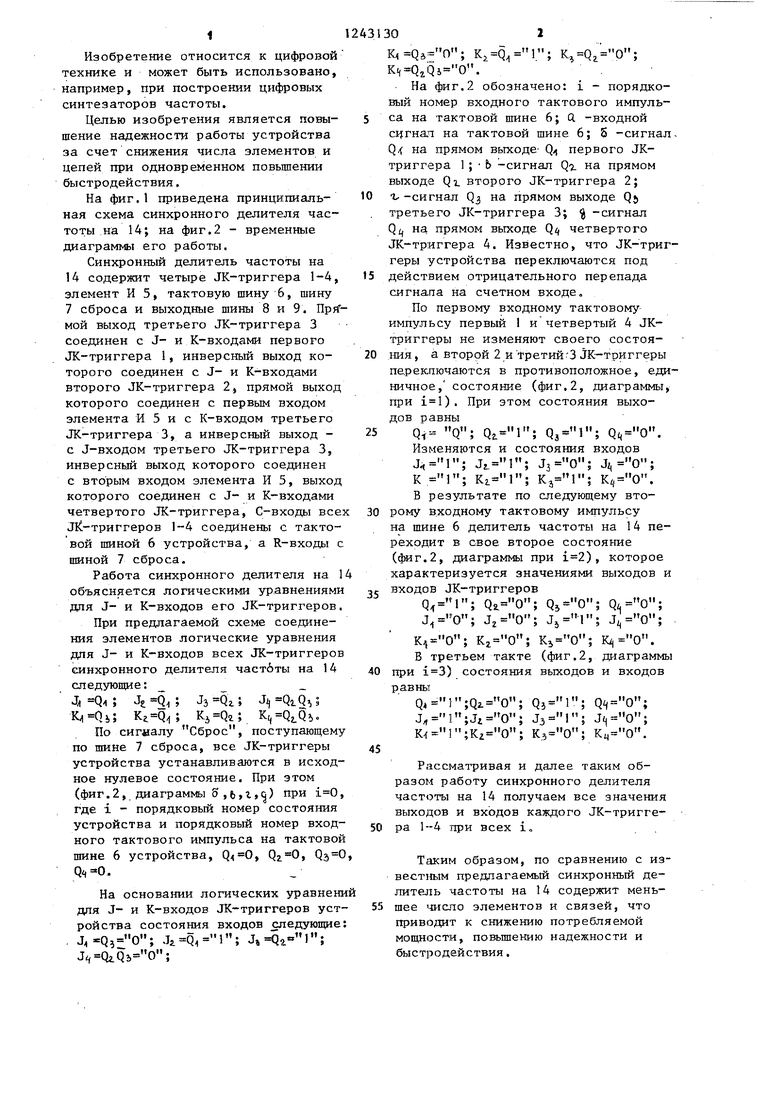

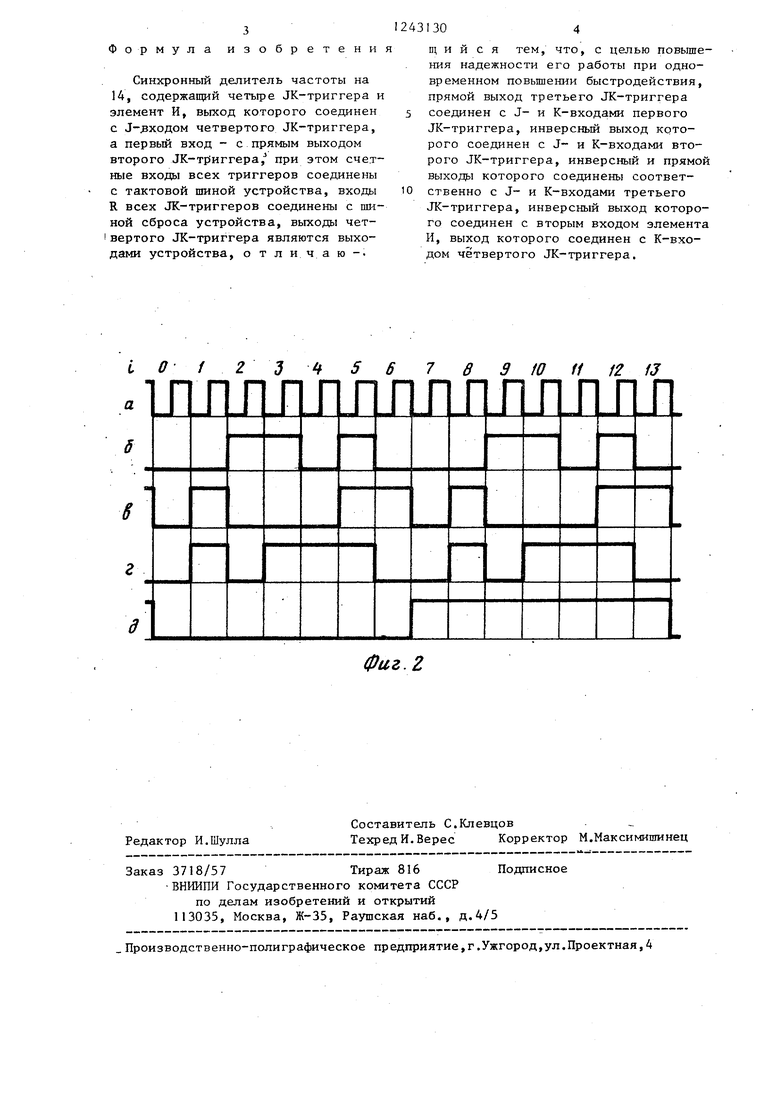

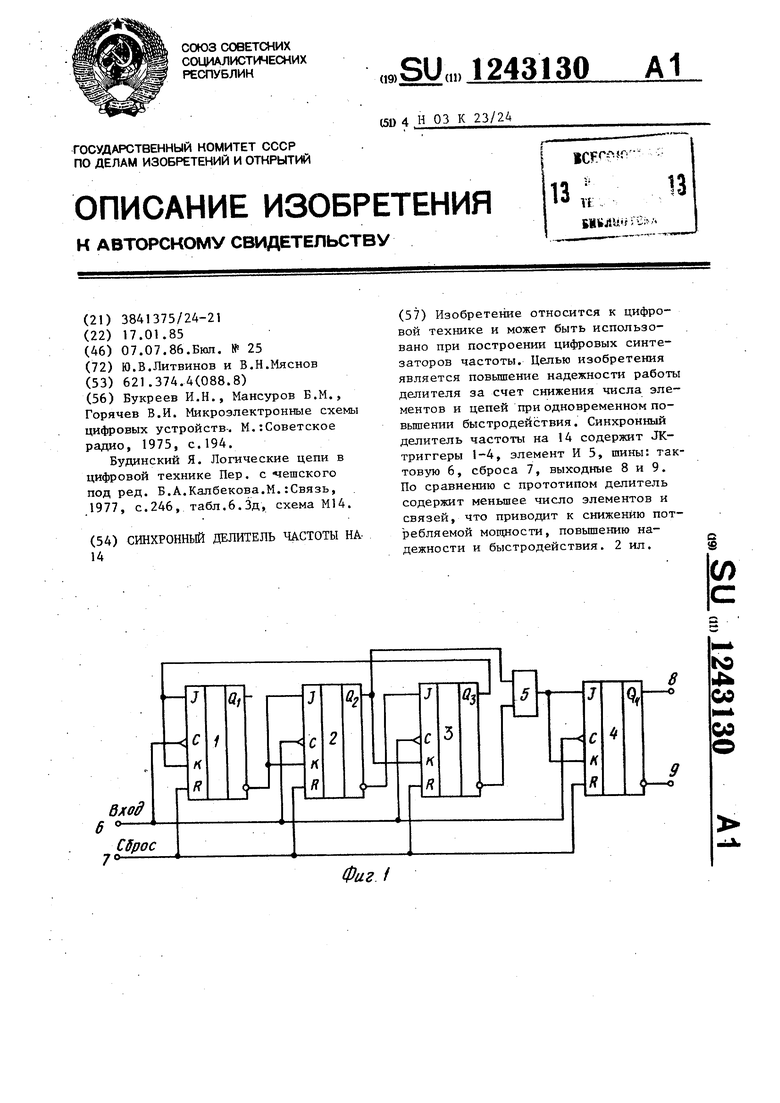

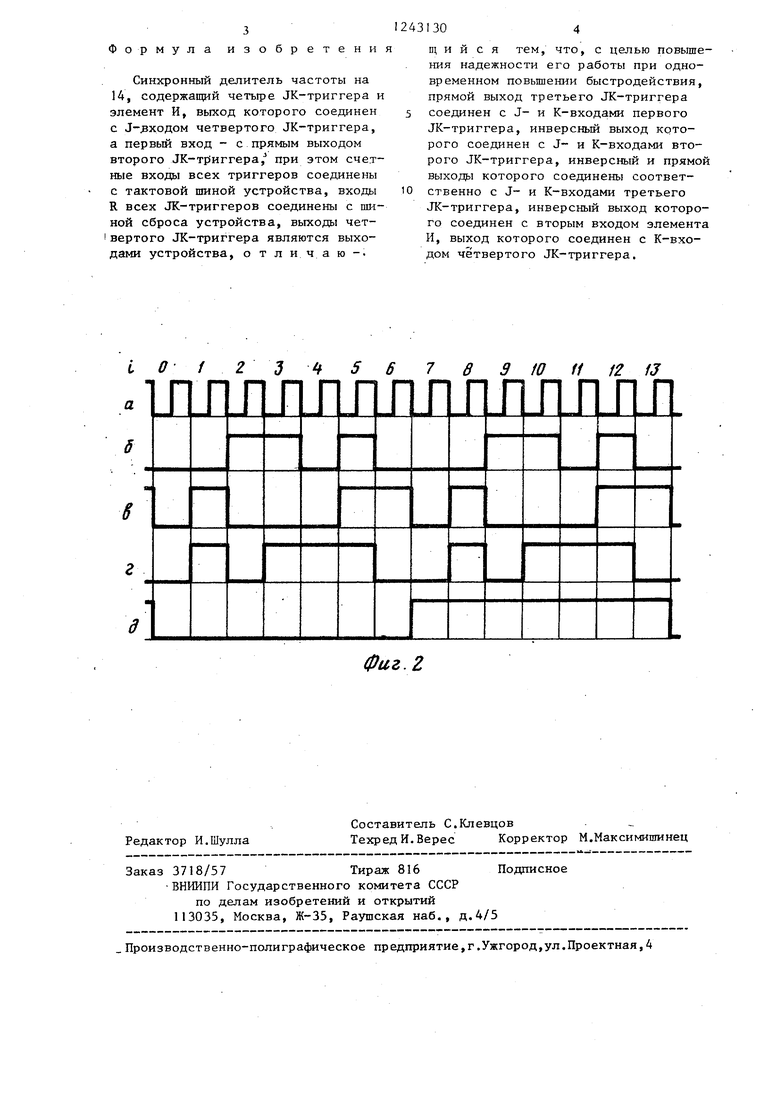

На фиг.1 приведена принципиаль- ная схема синхронного делителя частоты на 14J на фиг,2 - временные диаграммы его работы.

Синхронный делитель частоты на 14 содержит четыре JK-триггера 1-4, элемент И 5, тактовую шину 6, шину 7 сброса и выходные шины 8 и 9. Ilprf- мой выход третьего JK-триггера 3 соединен с J- и К-входами первого JK-триггера 1, инверсный выход ко- торого соединен с J- и К-входами второго JK-триггера 2, прямой выход которого соединен с первьм входом элемента И 5 и с К-входом третьего JK-триггера 3, а инверсный выход - с J-входом третьего JK-триггера 3, инверсный выход которого соединен с вторым входом элемента И 5, выход которого соединен с J- и К-входами четвертого JK-триггера, С-входы всех JK-триггеров 1-4 соединены с тактовой шиной 6 устройства, а R-входы с шиной 7 сброса.

Работа синхронного делителя на 1 объясняется логическими уравнениями для J- и К-входов его JK-триггеров. При предлагаемой схеме соединения элементов логические уравнения для J- и К-входов всех JK-триггеров синхронного делителя частбты на 14 следующие:

4| Qi ; Jt Qi ; Js Qz. Jif QiQi, 5 ,Q..

По сигналу Сброс, поступающему по шине 7 сброса, все JK-триггеры устройства устанавливаются в исходное нулевое состояние. При этом (фиг.2, диаграммы 5 ,ь,г,с) при , где 1 - порядковый номер состояния устройства и порядковый номер вход- ного тактового импульса на тактовой шине 6 устройства, Q-(0, , Q ) 0.

На основании логических уравнени для J- и К-входов JK-триггеров уст- ройства состояния входов следующие: . .

302

K, K, K,Q, ,.

Ha фиг.2 обозначено: i - порядковый номер входного тактового импульса на тактовой шине 6; 0. -входной сцгнап на тактовой шине 6; б -сигнал Q на прямом выходе- Q( первого JK- триггера 1 ; Ь -сигнал QT. на прямом выходе QI. второго JK-триггера 2; г--си гнал Q на прямом выходе Q третьего JK-триггера 3; -сигнал Qi на прямом выходе Q/ четвертого Ж-триггера 4. Известно, что JK-триггеры устройства переключаются под действием отрицательного перепада сигнала на счетном входе.

По первому входному тактовому- импульсу первый 1 и четвертый 4 JK- триггеры не изменяют своего состоя- 1-шя, а второй 2 и третий 3 JK-триггеры переключаются в противоположное, единичное, состояние (фиг,2, диаграммы при ). При этом состояния выходов равны

п - п . п , г . л Qt- ч ; Яг 1 ; Qj- ; О .

Изменяются и состояния входов Jj,r ; Ji, К ; .

В результате по следующему второму входному тактовому импульсу на шине 6 делитель частоты на 14 переходит в свое второе состояние (фиг.2, диаграммы при ), которое характеризуется значениями выходов и входов JK-триггеров

. А г . П , п -Ttn l . -f- I ; Qi- О ; Q5 О s Qi О ;

,0.

В третьем такте (фиг,2, диаграммы при ) состояния выходов и входов равны

Q4 r ;Qz 0 ;

J(

.

Рассматривая и далее таким образом работу синхронного делителя частоты на 14 получаем все значения выходов и входов каждого JK-триггера 1-4 :при всех 1„

Тгисим образом, по сравнению с известным предлагаемый синхронный делитель частоты на 14 содержит меньшее число элементов и связей, что приводит к снижению потребляемой мощности, повьш1ению надежности и быстродействия,

Формула изобретени

Синхронный делитель частоты на 14, содержащий четыре JK-триггера и элемент И, выход которого соединен с J-лходом четвертого JK-триггера, а первый вход - с прямым выходом второго JK-триггера, при этом счетные входы всех триггеров соединены с тактовой шиной устройства, входы R всех JK-триггеров соединены с шиной сброса устройства, выходы чет- Iвертого JK-триггера являются выходами устройства, о т л ича ю -

Редактор И.Шулла

Заказ 3718/57Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

щ и и с я тем, что, с целью повьше- ния надежности его работы при одновременном повьшении быстродействия, прямой выход третьего JK-триггера соединен с J- и К-входами первого JK-триггера, инверсный выход которого соединен с J- и К-входами второго JK-триггера, инверсный и прямой выхода которого соединены соответственно с J- и К-входами третьего JK-триггера, инверсный выход которого соединен с вторым входом элемента И, выход которого соединен с К-вхо- дом четвертого JK-триггера.

Фиг.2

Составитель С.Клевцов

Техред И. ВересКорректор М.Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Синхронный делитель частоты на 16 | 1984 |

|

SU1225010A1 |

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Синхронный делитель частоты | 1989 |

|

SU1651374A1 |

| Синхронный делитель частоты | 1986 |

|

SU1396273A1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Синхронный делитель частоты с четным коэффициентом деления | 1987 |

|

SU1629990A1 |

| Синхронный делитель частоты на 10 | 1985 |

|

SU1338061A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

Изобретение относится к цифровой технике и может быть использовано при построении цифровых синтезаторов частоты. Целью изобретения является повьшение надежности работы делителя за счет снижения числа элементов и цепей при одновременном по- вьшении быстродействия. Синхронный делитель частоты на 14 содержит JK- триггеры 1-4, элемент И 5, шины: тактовую 6, сброса 7, выходные 8 и 9. По сравнению с прототипом делитель содержит меньшее число элементов и связей, что приводит к снижению потребляемой мощности, повьшению надежности и быстродействия. 2 ил. с $ Q Ъ f 8

| Букреев И.Н., Мансуров Б.М., Горячев В.И | |||

| Микроэлектронные схемы цифровых устройств- | |||

| М.:Советское радио, 1975, с.194 | |||

| Будинский Я | |||

| Логические цепи в цифровой технике Пер | |||

| с чешского под ред | |||

| Б.А.Калбекова.М.:Связь, 1977, с.246, табл.6.Зд, схема М14. |

Авторы

Даты

1986-07-07—Публикация

1985-01-17—Подача