« 1

Изобретение относится к цифровой технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты.

Цель- изобретения - повышение надежности работы устройства за счет снижения вероятности возникновения сбоев путем уменьшения числа элементов и связей, что одновременно приводит к упрощению устройства.

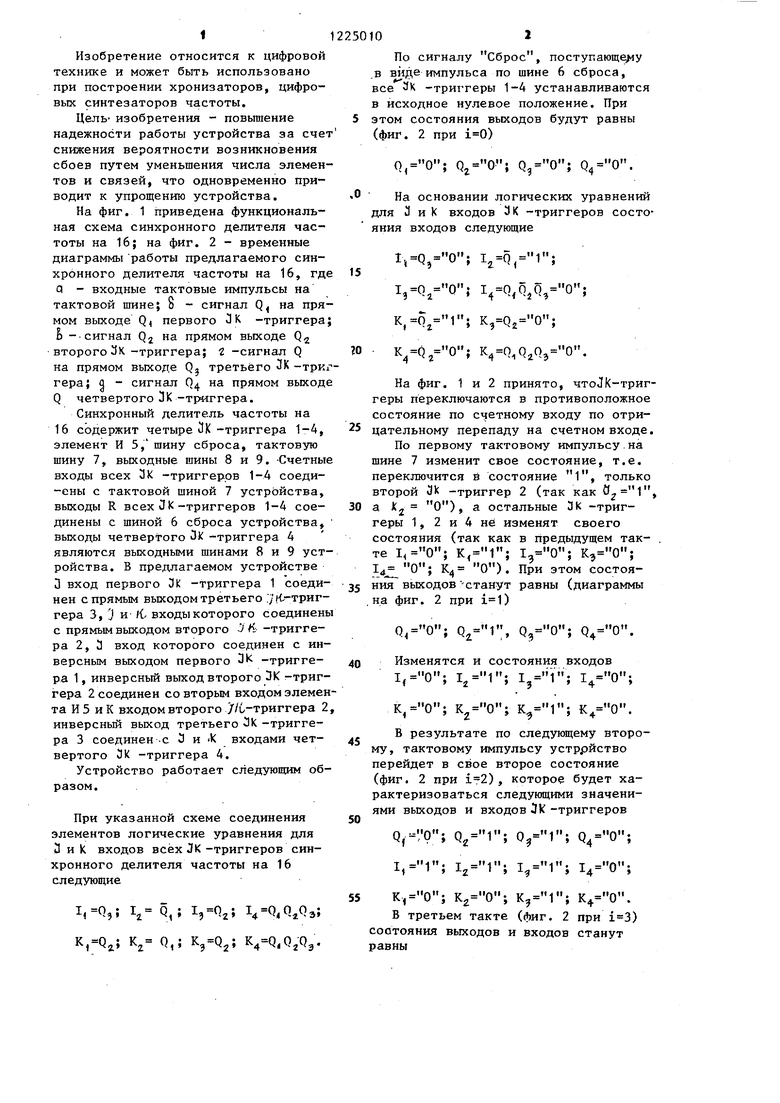

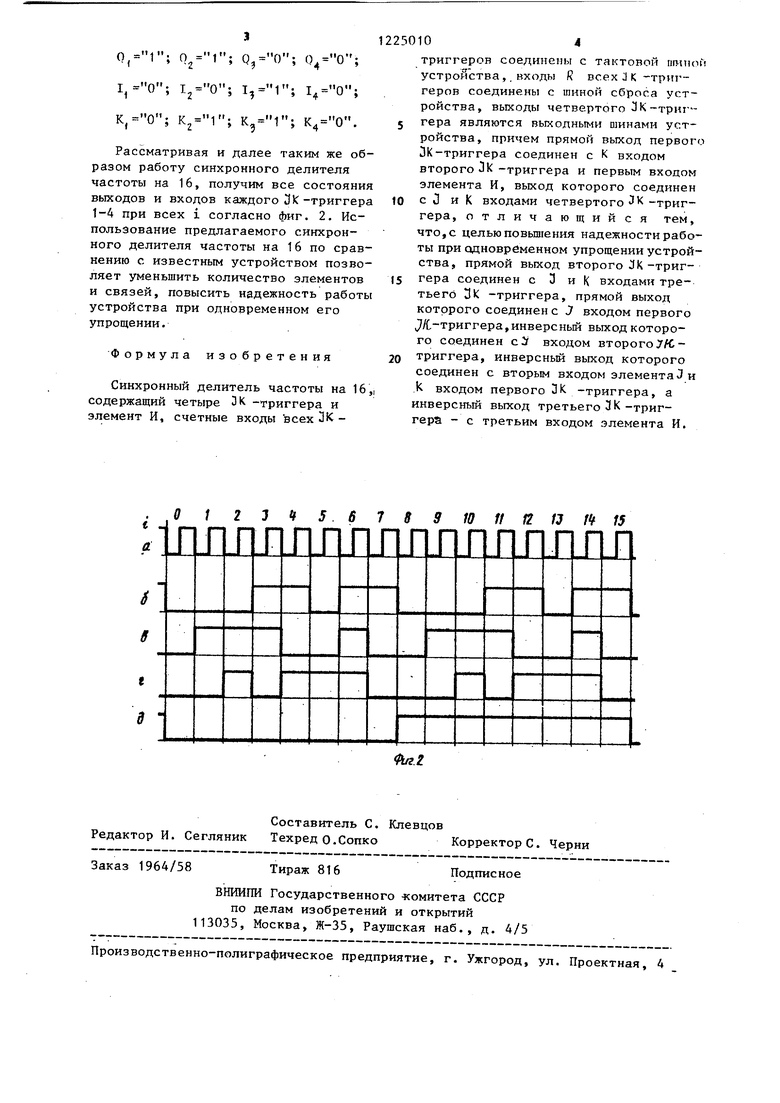

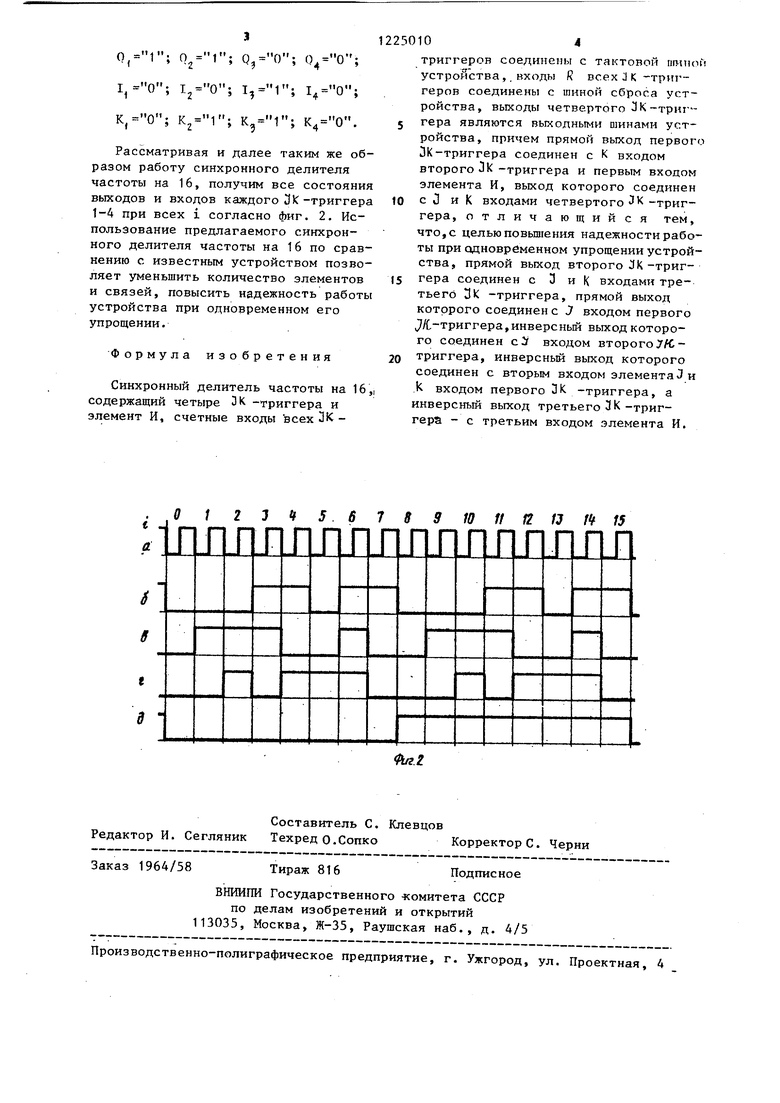

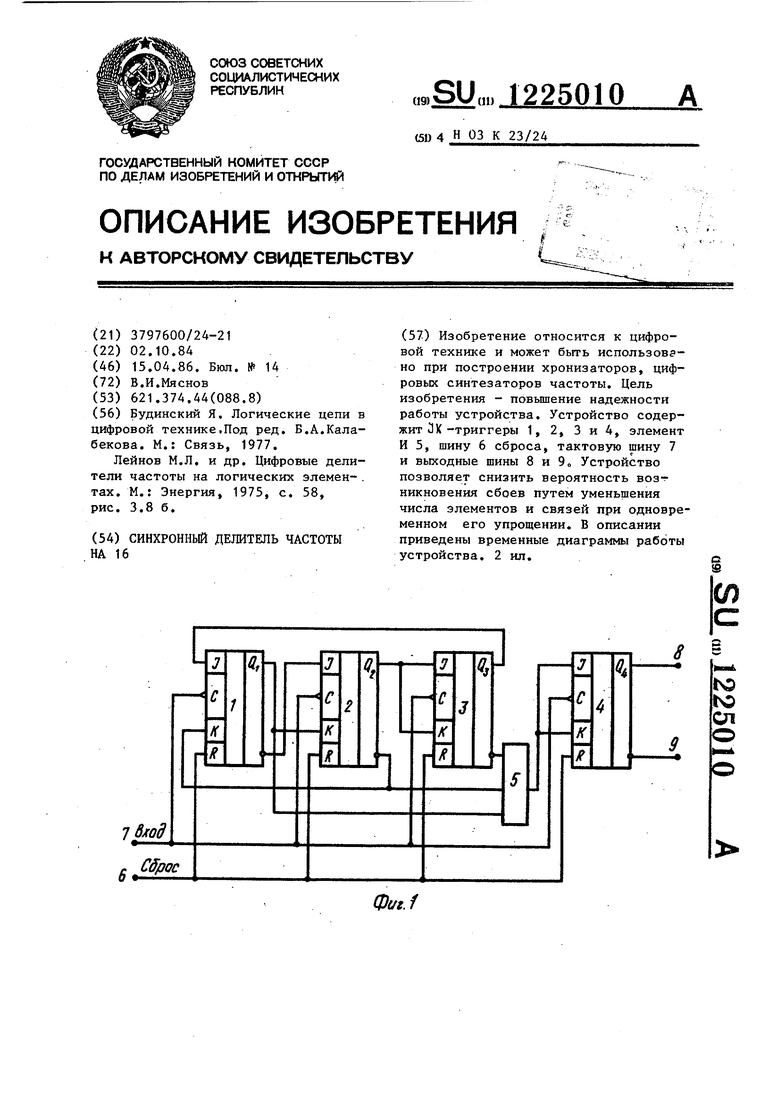

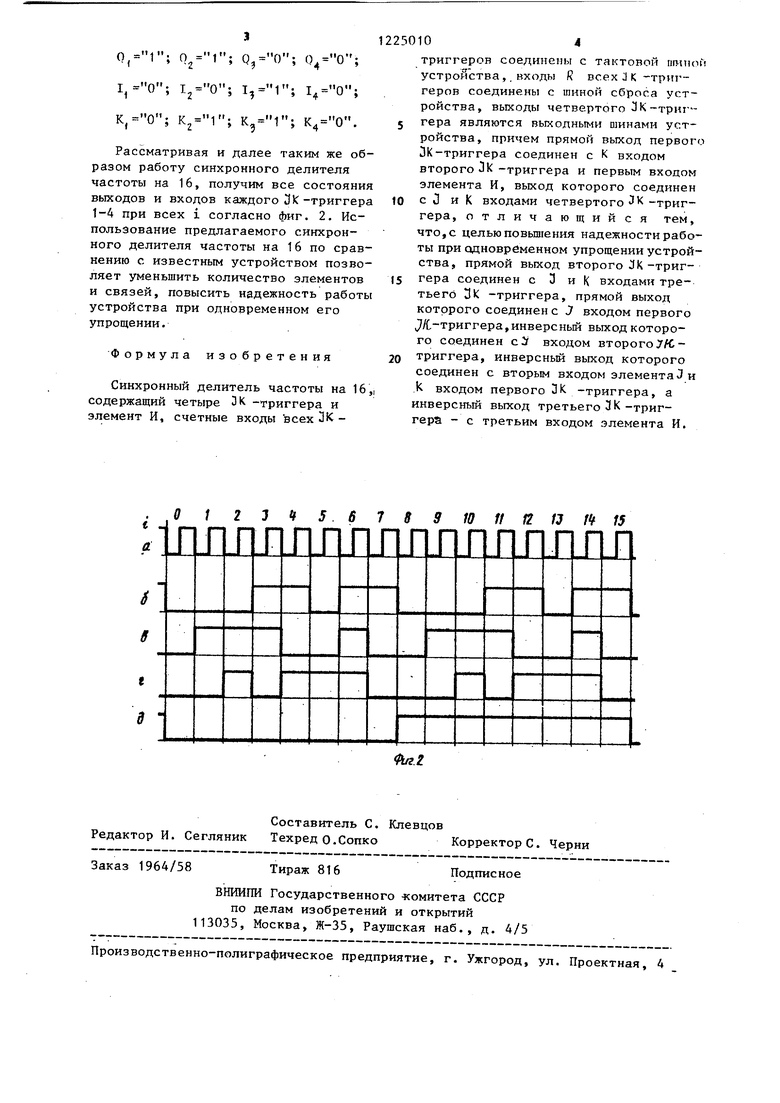

На фиг. 1 приведена функциональная схема синхронного делителя частоты на 16; на фиг. 2 - временные диаграммы работы предлагаемого синхронного делителя частоты на 16, где q - входные тактовые импульсы на тактовой шине; о - сигнал Q, на прямом выходе Q, первого JK -триггера; Ь --сигнал Qj на прямом выходе Q второго Зк -триггера; 1 -сигнал Q на прямом выходе Qj третьего ЗК -триггера; Q - сигнал Q на прямом выходе Q четвертого ЗК-т1 1ггера.

Синхронный делитель частоты на 16 содержит четыре ЗК -триггера 1-4, элемент И 5, шину сброса, тактовую шину 7, выходные шины 8 и 9. -Счетные входы всех ЗК -триггеров 1-Л соеди- -ены с тактовой шиной 7 устройства, выходы R всех Л li-триггеров 1-4 соединены с шиной 6 сброса устройства, выходы четвертого -триггера 4 являются выходными шинами 8 и 9 устройства. В предлагаемом устройстве D вход первого ЗК -триггера 1 соединен с прямым выходом третьего . //{.-триггера 3, и /С входыкоторого соединены с прямым выходом второго ) - -триггера 2, 3 вход которого соединен с инверсным выходом первого ЗК -триггера 1, инверсный выход второго ЗК -триггера 2 соединен со вторым входом элемента И5 и К входом второго 7/С-триггера 2, инверсный выход третьего ЗК -триггера 3 соединен -с 3 и -К входами четвертого ЗК -триггера 4.

Устройство работает следующим образом.

При указанной схеме соединения элементов логические уравнения для 3 и k входов всех ЛК -триггеров синхронного делителя частоты на 16 следующие

i,Q,; ,; I,QZ; K,Q,,; к Q,; -,:,.

2250102

По сигналу Сброс, поступающему в виде импульса по шине 6 сброса, все К -триггеры 1-4 устанавливаются в исходное нулевое положение. При 5 этом состояния выходов будут равны (фиг. 2 при )

0, .

«О На основании логических уравнений для 3 и К входов ЗК -триггеров состояния входов следующие

15

0

25

45

50

1,Q,

I,Q,,QjQ,

К-n i4.V r n.

,-Qj- 1 0 ;

V fS n.V n о n n

w и

На фиг. 1 и 2 принято, чтоЛК-триг- геры переключаются в противоположное состояние по счетному входу по отрицательному перепаду на счетном входе.

По первому тактовому импульсу.на шине 7 изменит свое состояние, т.е. переключится в состояние 1, только второй 3k -триггер 2 (так как

30 а 2 О) остальные ЗК -триггеры 1, 2 и 4 не изменят своего состояния (так как в предыдущем так- те К, 1, J-4Z К4 О). При этом состоя35 ния выходов станут равны (диаграммы ,на фиг. 2 при )

, Q,, .

40 Изменятся и состояния входов

J т 1. т . т f 2 з 1 4

К, ,

В результате по следующему второму, тактовому импульсу устррйство перейдет в свое второе состояние (фиг. 2 при ), которое будет характеризоваться следующими значениями выходов и входов JK -триггеров

1,

55 К, К,.

В третьем такте (фиг. 2при )

соотояния выходов и входовстанут равны

1,Q,

I,Q,,QjQ,

К-n i4.V r n.

,-Qj- 1 0 ;

V fS n.V n о n n

w и

0,Г ; Q, I, 1,Г ; K,

Рассматривая и далее таким же образом работу синхронного делителя частоты на 16, получим все состояния выходов и входов каждого Л1С -триггера 1-4 при всех i согласно фиг. 2. Использование предлагаемого синхронного делителя частоты на 16 по сравнению с известным устройством позволяет уменьшить количество элементов и связей, повысить надежность работы устройства при одновременном его упрощении.

Формула изобретения

Синхронный делитель частоты на 16, содержащий четыре ЗК -триггера и элемент И, счетные входы всех ЗКО 1 2 J tf S 6 7 8 9 W fl К 13 fif 15

Составитель С. Клевцов Редактор И. Сегляник Техред о.Сопко Корректоре. Черни

Заказ 1964/58

Тираж 816

ВНИИПИ Государственного -комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

2250104

триггеров соединены с тактовой пгитити устройства,.входы R всехJК -триггеров соединены с шиной сброса устройства, выходы четвертого 3 К-трит - 5 гера являются выходными шинами устройства, причем прямой выход первого DK-триггера соединен с входом второго Jk -триггера и первым входом элемента И, выход которого соединен

10 с J и К входами четвертого -триггера, отличающий ся тем, что, с целью повьшгения надежности работы при одновременном упрощении устройства, прямой выход второго J К-триг(5 гера соединен с 3 и К входами третьего Dk -триггера, прямой выход которого соединен с J входом первого 7/С триггера,инверсный выход которого соединен ci входом второго 7АС20 триггера, инверсный выход которого соединен с вторым входом элементаJ и .К входом первого 3К -триггера, а инверсный выход третьего 3 К-триггера - с третьим входом элемента И.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Синхронный делитель частоты на 14 | 1985 |

|

SU1243130A1 |

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| Синхронный делитель частоты на 9 на JK-триггерах | 1987 |

|

SU1444938A1 |

| Синхронный делитель частоты с четным коэффициентом деления | 1987 |

|

SU1629990A1 |

| Синхронный делитель частоты на 10 | 1984 |

|

SU1225009A1 |

| Делитель частоты на 11 | 1987 |

|

SU1522398A1 |

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

Изобретение относится к цифровой технике и может быть использовано при построении хронизаторов, цифровых синтезаторов частоты. Цель изобретения - повьппение надежности работы устройства. Устройство содержит J К -триггеры 1, 2, 3 и 4, элемент И 5, шину 6 сброса, тактовую шину 7 и выходные шины 8 и 9„ Устройство позволяет снизить вероятность воз-г никновения сбоев путем уменьшения числа элементов и связей при одновременном его упрощении. В описании приведены временные диаграммы работы устройства. 2 ил. 0tfe.f

| Будинский Я | |||

| Логические цепи в цифровой технике.Под ред | |||

| Б.А.Кала- бекона | |||

| М.: Связь, 1977 | |||

| Лейнов М.Л | |||

| и др | |||

| Цифровые делители частоты на логических элемен- | |||

| так | |||

| М.: Энергия, 1975, с | |||

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-15—Публикация

1984-10-02—Подача