Группа изобретений относится к импульсной технике и может быть использована в устройствах вычислительной техники и систем управления.

Известно триггерное устройство, содержащее триггер, первый и второй логические элементы Исключающее ИЛИ, первый и второй конденсаторы, первый и второй резисторы, входы установки и сброса триггера соединены с первыми обкладками соответственно первого и второго конденсаторов и через соответственно первый и второй резисторы с одной из шин питания, первые входы первого и второго логических элементов соединены между собой и с входной шиной устройства, вторые входы соединены соответственно с прямым и инверсным выходами триггера, а выходы соединены с вторыми обкладками соответственно первого и второго конденсаторов [1]

Недостатком известного устройства является малая помехоустойчивость, поскольку в режиме хранения информации на входе установки или сброса триггера отсутствуют удерживающие уровни напряжения, и при воздействии на триггер внешней помехи происходит его кратковременное переключение.

Известно также триггерное устройство, содержащее триггер, первый и второй резисторы, первый и второй конденсаторы, первый и второй логические элементы, выходы которых соединены соответственно со входами установки в единицу и обнуления триггера, а первые выходы подключены к первому входу устройства, прямой и инверсный выходы триггера соединены с первыми выводами соответственно первого и второго конденсаторов, вторые выводы которых соединены соответственно с первыми выводами первого и второго резисторов [2]

Основным недостатком известного триггерного устройства является низкая помехоустойчивость, выражающаяся в формировании на выходе устройства под действием внешних помех кратковременных паразитных импульсов, что в ряде случаев затрудняет согласование триггерного устройства с нагрузкой, поскольку требует принятия специальных мер по обеспечению устойчивости нагрузки к паразитным импульсам.

Целью изобретения является повышение помехоустойчивости.

В первом варианте поставленная цель достигается тем, что в триггерное устройство, содержащее триггер, первый и второй резисторы, первый и второй конденсаторы, первый и второй логические элементы, выходы которых соединены соответственно со входами установки в единицу и обнуления триггера, а первые входы подключены к первому входу устройства, прямой и инверсный выходы триггера соединены с первыми выводами соответственно первого и второго конденсаторов, вторые выводы которых соединены соответственно с первыми выводами первого и второго резисторов, введены третий и четвертый резисторы и первый и второй элементы исключающее ИЛИ, выходы которых подключены соответственно ко вторым входам первого и второго логических элементов, выполненных в виде элементов ИЛИ-НЕ, (И-НЕ), первые входы подключены ко второму входу устройства, а вторые входы соответственно через третий и четвертый резисторы соединены со вторыми выводами соответственно первого и второго конденсаторов, а вторые выводы первого и второго резисторов подключены соответственно к инверсному и прямому выходам.

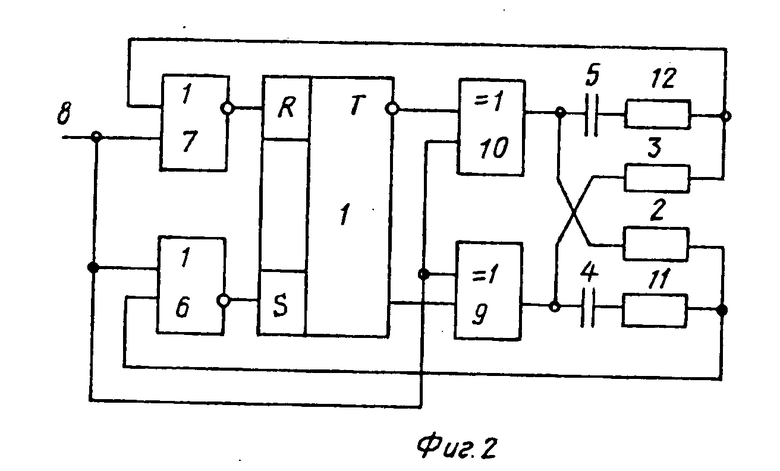

Во втором варианте поставленная цель достигается тем, что в триггерное устройство, содержащее триггер, первую и вторую последовательные RC-цепи, первый и второй логические элементы, выходы которых подключены соответственно ко входам установки в единицу и обнуления триггера, первые входы подклчены ко входу устройства, а вторые соединены с выходами соответственно первой и второй RC-цепей, введены первый и второй резисторы, первый и второй элементы исключающее ИЛИ, первые входы которых соединены с первыми входами логических элементов, выполненных в виде элементов ИЛИ-НЕ, (И-НЕ), вторые входы подключены соответственно к прямому и инверсному выходам триггера, а выходы соединены со входами соответственно первой и второй RC-цепей и соответственно через первый и второй резисторы подключены к соответствующим вторым входам второго и первого логических элементов.

На фиг. 1 и 2 представлены соответственно первый и второй варианты устройства.

Первый вариант триггерного устройства содержит триггер 1, первый 2 и второй 3 резисторы, первый 4 и второй 5 конденсаторы, первый 6 и второй 7 элементы ИЛИ-НЕ, выходы которых соединены соответственно со входами установки в единицу и обнуления триггера 1, а первые входы подключены к первому 8 входу устройства. Прямой и инверсный выходы триггера соединены с первыми выводами первого 4 и второго 5 конденсаторов. Первый 9 и второй 10 элементы исключающее ИЛИ своими выходами подключены ко вторым входам первого 6 и второго 7 элементов ИЛИ-НЕ первыми входами соединены со вторым 11 входом устройства, а вторым через третий 12 и четвертый 13 резисторы подключены ко вторым выводам соответственно первого 4 и второго 5 конденсаторов и через первый 2 и второй 3 резисторы соединены с инверсным и прямым выходами триггера 1.

Первый вариант триггерного устройства работает следующим образом.

Допустим, что триггер 1 находится в состоянии логического 0, на входах 8 и 11 уровень логического 0. При этом на прямом выходе триггера 1, на выходе элементов 10 и 6 и на S входе триггера 1 уровень логического 0, на инверсном выходе триггера 1, на выходе элементов 9 и 7 и на R входе триггера 1 уровень логической 1, удерживающий триггер 1 в состоянии логического 0.

На левой обкладке конденсатора 4 и на правой обкладке конденсаторы 5 - уровень логического 0, на первой обкладке конденсатора 4 и на левой обкладке конденсатора 5 уровень логической 1.

При поступлении уровня логической 1 на вход 11 изменяются состояния элементов 9, 10, 6, 7. При этом на выходах элементов 9 и 7 и на R входе триггера 1 устанавливается уровень логического 0, а на выходах элементов 10 и 6 и на S входе триггера 1 уровень логической 1, переключающий триггер 1 в состояние логической 1. При этом на правых обкладках конденсаторов 4 и 5 появляются перепады напряжения соответственно положительной и отрицательной полярности, не влияющие на состояние элементов схемы. Входные токи элементов 9 и 10 ограничиваются резисторами 12 и 13 соответственно.

При поступлении уровня логический 1 на вход 8 на выходе элемента 6 и на S входе триггера 1 устанавливается уровень логического 0. После этого на вход 11 подается уровень логического 0.

После переключения триггера 1 в состояние логической 1 происходит перезаряд конденсаторов 4 и 5 выходными напряжениями триггера 1 через резисторы 2 и 3 соответственно.

После перезаряда на правой обкладке конденсатора 4, на втором входе и на выходе элемента 9 устанавливается уровень логического 0, а на правой обкладке конденсатора 5, на втором входе и выходе элемента 10 уровень логической 1.

При поступлении уровня логического 0 на вход 8 на S входе триггера 1 устанавливается уровень логической 1, блокирующий триггер 1 в состоянии логической 1.

Переключение устройства в состояние логического 0 происходит аналогичным образом.

Второй вариант триггерного устройства работает следующим образом.

Допустим, что триггер 1 находится в состоянии логического 0, на входе 8

уровень логического 0. На прямом выходе триггера 1, на выходах элементов 10 и 6 и на S входе триггера 1 уровень логического 0, на инверсном выходе триггера 1, на выходах элементов 9 и 7 на R входе триггера 1 уровень логической 1, удерживающий триггер 1 в состоянии логического 0. На левой обкладке конденсатора 4 и на правой обкладке конденсатора 5 уровень логического 0, на правой обкладке конденсатора 4 и на левой обкладке конденсатора 5 уровень логической 1.

При поступлении уровня логической 1 на вход 8 на выходе элемента 7 и на R входе триггера 1 устанавливается уровень логического 0. Одновременно изменяется состояние элементов 9 и 10, на выходе элемента 9 устанавливается уровень логической 1, а на выходе элемента 10 уровень логического 0. На первых обкладках конденсаторов 4 и 5 появляются перепады соответственно положительной и отрицательной полярности, не влияющие на состояние элементов схемы. Входные токи элементов 6 и 7 ограничиваются соответственно резисторами 2 и 3.

Конденсаторы 2 и 3 начинают перезаряжаться выходными напряжениями элементов 9 и 10 через соответственно резисторы 2 11 и 12 3. После перезаряда на левой обкладке конденсатора 4, на правой обкладке конденсатора 5 и на втором входе элемента 7 устанавливается уровень логической 1, а на левой обкладке конденсатора 5, на правой обкладке конденсатора 4 и на втором входе элемента 6 уровень логического 0.

При поступлении уровня логического 0 на вход 8 изменяется состояние элементов 9 и 10. На выходе элемента 9 устанавливается уровень логического 0, а на выходе элемента 10 уровень логического 1. При этом на правой обкладке конденсатора 5 появляется перепад напряжения положительной полярности, обеспечивающий уровень логической 1 на втором входе элемента 7 и уровень логического 0 на его выходе и на R входе триггера 1. На правой обкладке конденсатора 4 появляется перепад напряжения отрицательной полярности, обеспечивающий уровень логического 0 на втором входе элемента 6 и уровень логической 1 на его выходе и на S входе триггера 1.

Триггер 1 переключается в состояние логической 1. На выходе элемента 9 устанавливается уровень логической 1, на выходе элемента 10 уровень логического 0. На правой обкладке конденсатора 5 восстанавливается уровень логической 1, сохраняющий уровень логического 0 на R входе триггера 1. На правой обкладке конденсатора 4 восстанавливается уровень логического 0, сохраняющий уровень логической 1 на S входе триггера 1 и блокирующий его в состоянии логической 1.

Переключение устройства в состояние логического 0 происходит аналогичным образом.

Технико-экономический эффект данного предложения заключается в том, что при выполнении триггерного устройства по любому из вариантов новая совокупность признаков позволяет повысить помехоустойчивость за счет осуществления блокировки состояния статического триггера в режиме хранения информации путем подачи удерживающего уровня напряжения с его выхода на вход установки или сброса через внешние цепи обратной связи, которые образуются при введении в схему дополнительных резисторов. При этом исключается при воздействии внешних помех формирование на выходе статического триггера кратковременных паразитных импульсов, что существенно упрощает согласование триггерного устройства с нагрузкой. Использование цепей фиг. 2 возможно в фиг. 1 и наоборот без изменения способа включения их в схему триггерного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2178617C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250558C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2210178C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2237354C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237969C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2224357C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2212095C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237970C1 |

| Формирователь одиночного импульса (его варианты) | 1983 |

|

SU1190488A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО (ЕГО ВАРИАНТЫ) | 1983 |

|

SU1186057A1 |

1. Триггерное устройство, содержащее триггер, первый и второй резисторы, первый и второй конденсаторы, первый и второй логические элементы, выходы которых соединены соответственно с входами установки в единицу и обнуления триггера, первые входы подключены к первому входу устройства, прямой и инверсный выходы триггера соединены с первыми выводами соответственно первого и второго конденсаторов, вторые выводы которых соединены соответственно с первыми выводами первого и второго резисторов, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены третий и четвертый резисторы и первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых подключены соответственно к вторым входам первого и второго логических элементов, выполненных в виде элементов ИЛИ - НЕ, (И - НЕ), первые входы подключены к второму входу устройства, а вторые входы соответственно через третий и четвертый резисторы соединены с вторыми выводами соответственно первого и второго конденсаторов, а вторые выводы первого и второго резисторов подключены соответственно к инверсному и прямому выходам триггера.

2. Триггерное устройство, содержащее триггер, первую и вторую последовательные RC-цепи, первый и второй логические элементы, выходы которых подключены соответственно к входам установки в единицу и обнуления триггера, первые входы подключены к входу устройства, а вторые соединены с выходами соответственно первой и второй RC-цепей, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены первый и второй резисторы, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых соединены с первыми входами логических элементов, выполненных в виде элементов ИЛИ - НЕ (И - НЕ), вторые входы подключены соответственно к прямому и инверсному выходам триггера, а выходы соединены с входами соответственно первой и второй RC-цепей и соответственно через первый и второй резисторы подключены к соответствующим вторым входам второго и первого логических элементов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Триггерное устройство (его варианты) | 1981 |

|

SU970650A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N 711994, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1997-09-10—Публикация

1983-05-20—Подача