та И подключен к входу установки в О третьего триггера, инвертирзпощий выход которого подключен к управляющему входу второго ключа, входы мультиплексора являются входами устройства, выход подключен к второму входу блока сравнения, адресный вход - к выходу счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1988 |

|

SU1499389A1 |

| Устройство для ввода информации | 1989 |

|

SU1644120A2 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| Устройство контроля состояния объекта | 1988 |

|

SU1564667A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее блок сравнения, блок памяти, первый триггер, первый инвертор, регистр данных, регистр адреса, генератор Тактовых импульсов, счетчик адреса и первый элемент ИЛИ, выходы регистра данных, первого триггера, регистра адреса и входы первого элемента ИЛИ являются выходами данных, стробирукщим, адреса, входами считывания и сброса устройства соответственно, выход первого элемента ИЛИ подключен через первый инвертор к входу установки в О первого триггера, вход установки в 1 которого соединен со стробируницими входами регистра данных и регистра адреса, выход счетчика адреса соединен с информационным входом регистра адреса и с адресным входом блока памяти, вьпсод которого соединен с первым входом блока сравнения , выход которого подключен к входу записи блока памяти, второй вход - к информационным входам блока памяти и регистра данных, о т л ичающееся тем, что, с целью упрощения устройства, оно содержит мультиплексор, второй элемент ИЛИ, первый и второй ключи, второй и третий триггеры, элементы И с первого по третий и формирователь импульсов, выход которого соединен с первым входом второго элемента ИЛИ и с первым входом сброса второго триггера, синхровход - с выходом генератора тактовых импульсов и с информационным входом первого ключа, выход которого подключен к счетному входу счетчика адреса и к управляющему входу блока сравнения, выход которого с jg соединен с информационным входом второго ключа, выход которого подкп чен к второму входу второго элемента ИЛИ, выход которого соединен со стробирующим входом регистра адреса,Vj выход блока сравнения соединен спер вым входом первого элемента И и i с входом установки в 1 третьего триггера, неинвертирующнй выход ко:л торого подключен к второму входу первого элемента И, выход которого подклюUD чен к входу установки в I второго триггера, второй вход сброса кото00 рого является входом сброса устройства, неинвертирукхций и инвертирукнций выходы подключены соответственно к первому входу второго элемента И и к объединенным управляющему входу первого ключа и первому входу третье го элемента И, второй вход которого соединен с выходом первого элемента ИЛИ и с вторым входом второго элемента И, выход которого подключен к информационному входу формирователя импульсов, выход третьего элемен

1

Изобретение относится к автоматике к вычислительной.технике и может быть использовано для ввода информации о состоянии комплекса технических средств от различных дискретных датчиков (аппаратуры каналообразования, аппаратуры контроля каналов, аппаратуры коммутации) в устройство обработки данных или в управляющую вычислительную машину.

Из вестно устройство сбора информации, содержащее мультиплексор, генератор тактовых импульсов, соединенный со счетчиком адреса, выход которого соединен с дешифратором адреса, выходы которого соединены с мультиплексором lj .

Наиболее близким к изобретению по технической сущности является устройство для вввода информации, со держащее блок сравнения, блок памяти, первьй триггер, первый инвертор, регистр данных, регистр адреса, генератор тактовых импульсов, счетчик адреса и первый .элемент ИЛИ, выходы регистра данных, первого триггера, регистра адреса и входы первого элемента ИЛИ являются выходами данных, стробирук(щим, адреса, входами считьюания и сброса устройства соответственно, выход первого элемента ИЛИ подключён Через первый инвертор к входу установки в О первого триггера, вход установки в 1 которого соединен со стробирующими входами регистра данных и регистра адреса, выход счетчика адреса соединен с информационнь&1 входом регистра адреса и с-адресным входом блока памяти, выход которого соединен с первым входом блока сравнения, выход которого подключен к входу записи блока памя.ти, второй вход к информационшлм входам блока памяти и регистра данныхГ.

Недостатком известных устройств является их сложность.

Цель изобретения - упрощение устройства.

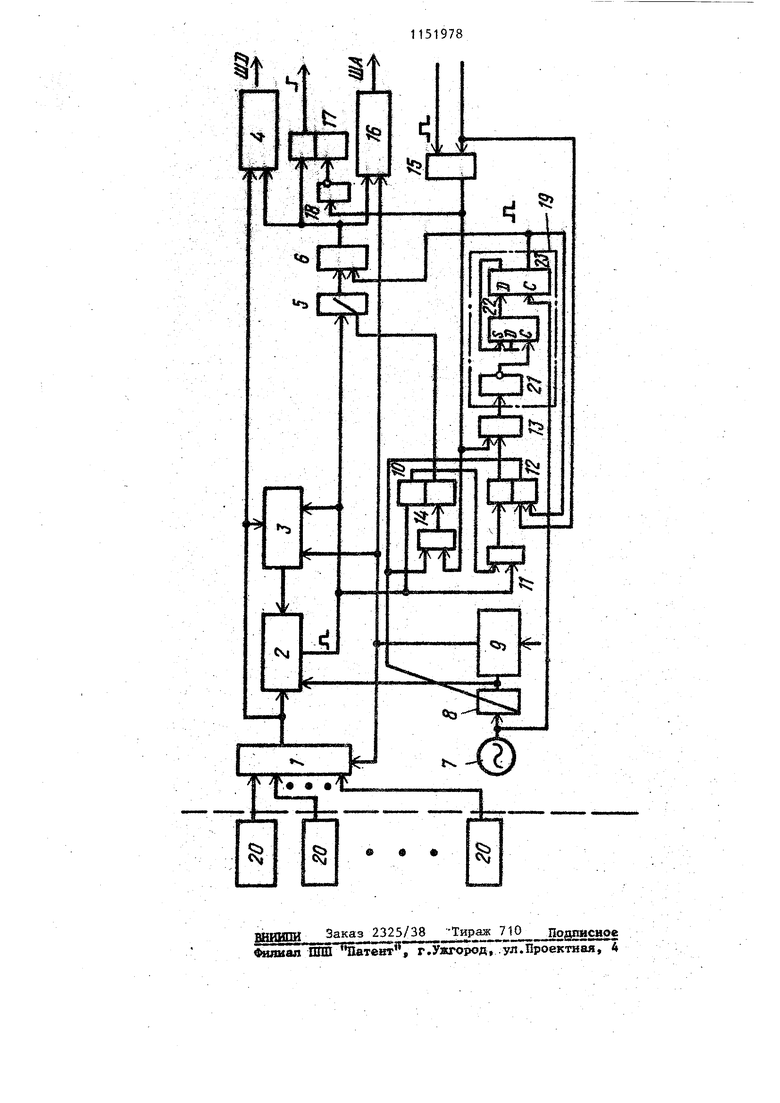

Указанная цель достигается тем, что в устройство для ввода информации, содержащее блок сравнения, блок памяти, первьй триггер, первый инвертор, регистр данных, регистр адреса, генератор тактовых импульсов, счетчик адреса и первый элемент ИЛИ, выходы регистра данных, первого триггера, регистра адреса и входы первого элемента ИЛИ являются выходами данных, стробирующим, адреса, входами считывания и c6iJoca устройства соответственно, выход первого элемента ИЛИ подключен через первый инвертор к входу установки в О первого триггера, вход установки в 1 которого соединен со стробирующими входами регистра данных и регистра адреса f выход счетчика адреса соединен с информационным входом регистра адреса и с адресным входом блока памяти, выход которого соединен с первым входом блока сравнения, выход которого подключен к входу записи блока памяти, второй вход - к информационным входам блока памяти и регистра данных, введены мультиплексор, второ элемент ИЛИ, первый и второй ключи, второй и третий триггеры, элементы И с первого по третий и формирователь импульсов, выход которого соединен с первым входом второго элемента ИЛИ и с первым входом сброса второго триггера, синхровход с выходом генератора тактовых импульсов и с информационным входом первого ключа, выход которого подключен к счетному входу счетчика адреса и к управляквцему входу блока сравнения , выход которого соединен с информационным входом второго ключа, выход которого подключен к второму входу второго элемента ИЛИ, выход которого соединен со стробируияцим входом регистра адреса, выход блока сравнения соединен с первым входом первого элемента И и с входом установки в 1 третьего триггера, неинвертирующий выход которого подключен к второму входу первого элемента И, выход которого подключен к входу установки в 1 второго триггера, второй вход сброса которого является входом сброса устройства, неинвертирукмций и инвертирукмций выходы подклю чены соответственно к первому входу второго элемента И и к объединенным управляющему входу первого ключа и первому входу третьего элемента И,. второй вход которого соединен с выхо дом первого элемента ИЛИ и с вторым входом второго элемента И, выход которого подключен к информационному входу формирователя импульсов, выход третьего элемента И подключен к входу установки в О третьего триггера инвертирующий выход которого подключен к управляющему входу второго клю ча, входы мультиплексора являются входами устройства, выход подключен к второму входу блока сравнения, адресный вход - к выходу счетчика ад реса. На чертеже Приведена схема предлагаемого устройства. Устройство содержит мультиплексор t, блок 2 сравнения, блок 3 памяти, регистр 4 данных, второй ключ 5 второй элемент ИЛИ 6, генератор 7 тактовых импульсов, первый ключ 8, счетчик 9 адреса, третий триггер 10, первый элемент И t1, второй триггер 12, второй элемент И 13, третий элемент И Т4, первый элемент ИЛИ 15, регистр 16 адреса, первый триггер 17 инвертор 18, формирователь 19 импульсов, датчики 20. I От каждого дискретного датчика считываемая информация может быть представлена, например, байтом инфор мации, которая через регистр данных и шину данных (ЩЦ) при считьшании постудает в ЭВМ с указанием адреса, поступающего по шине адреса (IJA) . Каждый датчик выдает совокупность бинарных символов, характеризующих состояние, например, аппаратуры (каналов) связи. Например, байт информа ции от первого датчика может характеризовать наличие сигналов Авария восьми линейных трактов, байт от вто рого датчика - наличие сигналов неис пр авности восьми стоек каналообра;; зующей аппаратуры, байт третьего датчика - наличие сигналов неисправности восьми каналов связи и т..д. Период опроса датчиков определяется допустимь1М временем обнаружения изменения состояния и может составлять примерно 0,5-1 с. За этот период времени с большой, вероятностью состояние датчиков не изменяется, т.е. факт изменения информации не зарегистрирован. В этих условиях целесообразно продолжать опрос до обнаружения следукнцего изменения. Устройство работает следующим образом. В исходном состоянии оба ключа 5 и 8 открыты. При поступлении первого импульса от генератора 7 тактовых импульсов счетчик 9 адреса устанавливается в первое состояние, соответствующее адресу первого датчика. Через мультиплексор 1 информация о состоянии этого датчика поступает на блок 2 сравнения, на второй вход которого поступает информация о предыдущем состоянии первого датчика, т.е. датчика, адрес которого указан счетчиком 9 адреса, а на третий вход - сигнал, формирующий импульс сравнения двух числовых значений информации. Блок 2 сравнения сравнивает предыдущее и текущее состояния датчика, и если информация от датчика не изменяется по сравнению с предыдущим состоянием, то сигнал на выходе блока 2 сравнения не формируется, и счетчик адреса выставляет следующий адрес датчика. . Если имеет место изменение информации, то на выходе блока 2 сравнения формируется импульс, по которому в регистр адреса и регистр данных через открытый ключ 5 и элемент ИЛИ 6 поступает сигнал записи, по которому в эти регистры поступают соответственно данные и адрес изменившегося состояния датчика. Сигнал с выхода блока 2 сравнения записьшает новые данные в блок 3 памяти, а также устанавливает в единичное состояние триггер 10, который открывает эле- мент И 11. Триггер 10 закрывает ключ 5 во избежание записи в регистры 16 адреса и данных 4 информации следующего датчика, если-не будут считаны предыдущие данные. Одновременно сигнал с выхода элемента ИЛИ 6 перебрасывает триггер 17, вьщавая сигнал Данные готовы, например, в центральньш процессор, которьй формирует сигнал Считывание, по которому по шинам данных и. шинам адреса считывается информация из регистров данных 4 и адреса 16. По сигналу считывания через инвертор 1 сбрасывается триггер 17, а также триггер 10 через открытьй элемент И 14. Импульс считывания не пр ходит через элемент И 13, закрытьй триггером 12. Через открытый ключ 5 информация следующего датчика, при наличии сигнала изменения, формируе го блоком 2 сравнения, готова записаться в регистры данных 4 и адреса б. Если новых изменений по последовательно выставляемым адресам нет, то счетчик адреса рабртает от генер тора 7 тактовых импульсов до появле ния импульса факта изменения на вых де блока 2 сравнения. Если центральный процессор не сч тывает изменившиеся данные (например, занят обработкой других объектов) и регистры данных 4 и адреса 1 заняты, то счетчик адреса опрашивае последующие датчики до появления си нала о наличии следунщего факта изменения состояния, т.е. счетчик адреса, несмотря на занятость регистров адреса и данных, продолжает опрос, если изменения данных нет, и доходит до следующего датчика, из менившего состояние. Если обнаружен второе измененное состояние, то импульс с выхода блока 2 сравнения через ключ 5 не пройдет, так как ключ 5 закрыт триггером 10, взведен ным сигналом первого изменения. Импульс с выхода блока 2 сравнения через открытый элемент И 11 перебра сывает триггер 12, который закрывает ключ 8, прекращая опрос последую щих датчиков до появления сигнала считывания. Теперь при формировании сигнала Считывание вначале информация считывается из регистров данных 4 и адреса 16 по шинам ОЩ и ША (данных и адреса). Передним фронтом импульса считьшания сбрасьшается через инвертор 18 триггер 1.7. Импульс счи тывания через элементы ИЛИ 15 и открытый элемент И 13 поступает на формирователь 19 импульсов, который формирует от заднего фронта импульса считывания калиброванный по длительности импульс (длительностью в один такт генератора). Этот импульс через элемент ИЛИ 6 записывает в регистры данных 4 и адреса 16 данные и адрес текущего изменения, взводит триггер 17, а также сбрасывает триггер 12, открывая ключ 8 и закрывая элемент И 13. Следукядчм сигналом считывания в начале по шинам данных и адреса считывается информация из регистров адреса 16 и данных 4, сбрасывается триггер 17, а также через открытый элемент И 14 сбрасывается триггер 10, открывая ключ 5 и т.д. Формирователь импульсов работает следующим образом. Задний фронт импульса считывания (отрицательньй перепад) после элемента И 13 и инвертора 21 поступает на вход С триггера 22 в виде положительного перепада и перебрасывает триггер 22, формируя на входе) триггера 23 низкий уровень. При поступлении на вход С триггера 23 первого положительного фронта тактовой частоты на вб1ходе триггера 23 формируется сигнал низкого уровня, по которому перебрасывается по вхолу S триггер 23, подавая на вход D триггера 23 высокий уровень. При поступлении второго положительного фронта тактовой частоты на выходе триггера 23 формируется сигнал высокого уровня, т.е. на выходе формирователя 19 импульса формируется положительный импульс длительностью в один тактовый интервал (после заднего фронта импульса считывания формируется импульс длительностью от первого до следуняцего положительного фронта тактовой частоты). Упрощение устройства достигается путем уменьшения объема памяти за счет отсутствия памяти адресов датчиков информации; отсутствия памяти всех новых значений изменившейся информации; отсутствия памяти всех адресов изменившейся информации. Кроме того, упрощение достигается за счет мультиплексирования входных атчиков и использования одного блока сравнения (в известном устройстве количество блоков сравнения равно количеству датчиков). 7 Отсутствие памяти адресов опрашиваемых датчиков достигается за счет использования циклического опроса всех датчиков, при этом адреса датчи ков определяются счетчиком адреса и управляющим циклическим опросом. Отсутствие памяти всех новых значений изменившейся информации и памяти адресов изменившейся информации (осуществляемые в известном устройстве соответственно блоками 5 и 4) достигается за счет того, что при последовательном опросе изменившейс информации и ее адреса не обязательно иметь полную память этой информации и ее адресов, достаточно иметь память текущих значений изменения и адреса. Действительно, после каждого полного цикла опроса всех датчи ков и передачи информации в ЭВМ память изменившейся информации и адреса не нужна и может быть сброшена до следукндего цикла, т.е. эти блоки памяти часть времени не используются В изобретении используется не полный объем памяти всех изменившихся состояний и адресов, а только памят текущего (опрошенного) изменения и его адреса, если оно имело место. При этом устройство продолжает опрос следующих датчиков (даже в том случае, ейли ЭВМ- занята обрат боткой других процессов) до выявле78ния следующего изменившегося состояния датчика.. Следует отметить, что в системах связи основной информацией сбора является состояние каналов, трактов и аппаратуры связи. Для своевременного выявления неисправности (изменения состояния) цикл опроса датчиков должен быть небольшим (единицы секунд), и за зто время с малой вероятностью возникает неисправность нескольких устройств (каналов, трактов и т.д.),так как коэффициент готовности каналов и трактов Kj.0,95. а наработка на отказ аппаратуры связи составляет сотни и тысячи часов. Поэтому, выявив изменение и адрес изменения какого-либо датчика, устройство может (даже если ЭВМ занята ) продолжать опрос остальных датчиков, которые с большой вероятностью не изменят своего состояния на короткое время. Таким образом, в изобретении отсутствует память адресов (используется счетчик адреса), используется один блок сравнения вместо ряда таких блоков (не требуется иметь в каждом блоке сравнения память предьщущего состояния), а. также имеется возможность обхода датчиков даже при занятом процессоре с запоминанием наличия до двух измененных состояний датчиков.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Проектирование и применение операционных усилителей | |||

| Под ред | |||

| Дж | |||

| Грэма | |||

| М., Мир, 1974, с | |||

| Способ получения продуктов уплотнения фенолов с альдегидами | 1920 |

|

SU361A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО для СБОРА ИНФОРМАЦИИ от ДИСКРЕТНЫХ ДАТЧИков | 0 |

|

SU377759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-12-16—Подача