Изобретение относится к вычислительной технике и может найти применение в автоматизированных системах управления технологическими процессами.

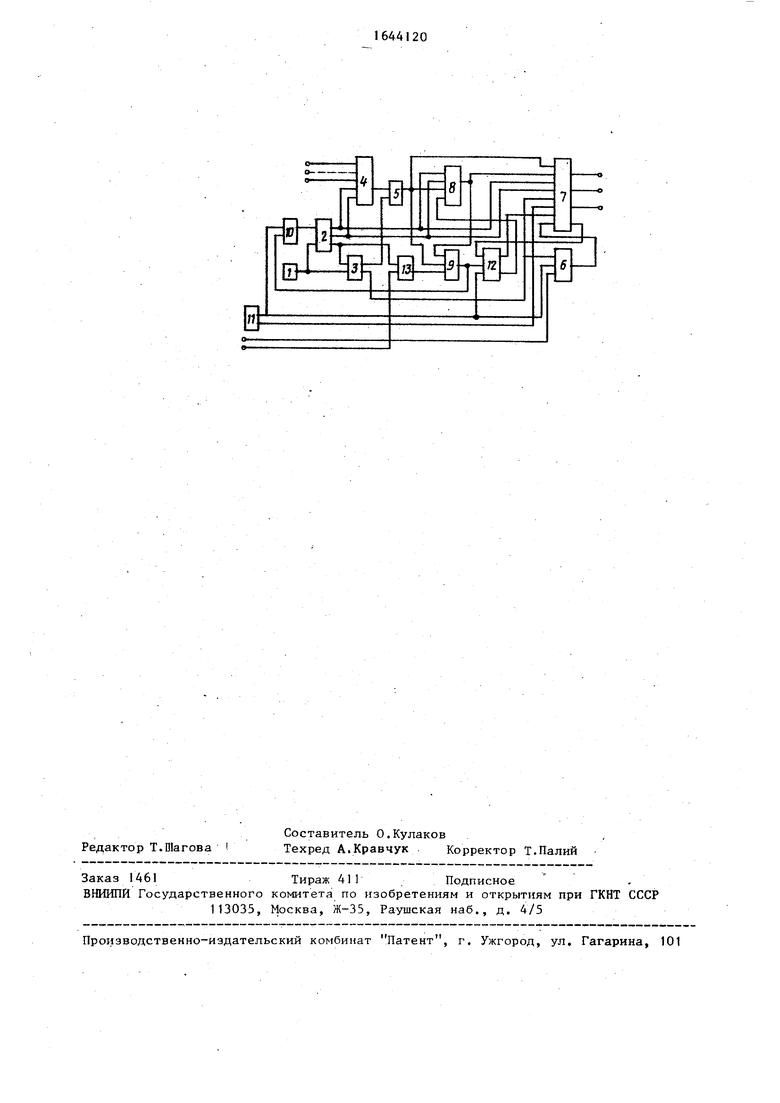

Цель изобретения - повышение надежности устройства,На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит формирователь 1, регистр адреса 2, триггер 3, мультиплексор 4, первый элемент И 5, блок управления 6, блок буферной памяти 7, блок оперативной памяти 8, компаратор 9, второй элемент И 10, генератор 11, блок коррекции 12, блок приема сигнала Вызов 13.

Устройство работает следующим образом.

При включении питания на выходе формирователя 1 появляется сигнал,

который устанавливает регистр 2 адреса и триггер 3 в исходное положение. Сигналом с первого выхода триггера на выходе первого элемента И 5 формируется сигнал логического нуля, а сигналом с второго выхода триггера блок управления 6 и блок буферной памяти устанавливаются в нулевое состояние. Начинается первый цикл опроса датчиков, при котором блок оперативной памяти 8 устанавливается в нулевое положение. Под действием кода, поступающего с выхода регистра 2 адреса на адресные входы мультиплексора 4 и блока оперативной памя- ти 8, выход первого датчика подключается к выходу первого элемента И 5, а на выходе блока оперативной памяти 8 формируется код, записанный по это-, му адресу. Код с выхода блока оперативной памяти поступает на первый

ся

4 ГО

1Ч

вход компаратора 9, на второй вход которого поступает в это время сигнал логического нуля с элемента И 5. Если на выходе блока оперативной памяти 8 имеется сигнал логической единицы, то на выходе компаратора 9 появляется сигнал логического нуля, который, поступая на второй вход второго элемента И 10, запрещает про- хождение через него импульсов от генератора и, поступая на второй вход блока коррекции 12, сигнализирует о переходе датчика из одного состояния в другое. Генератор 11 выдает на сво- их выходах тактовые импульсы отрицательной полярности, сдвинутые относительно друг друга на 180°. При наличии сигнала логического нуля на первом входе (блок буферной памяти сво- боден) и под действием первого тактового импульса с первого выхода генератора /ТИ1/ на первом выходе блока коррекции 12 формируется сигнал разрешения записи, который поступает на вход блока буферной памяти. Тактовым импульсом с второго выхода генератора /ТИ2/ осуществляется запись кода в блок буферной памяти. Но записи не происходит, так как на входе сброса блока буферной памяти присутствует сигнал сброса с триггера 3. С приходом второго ТИ1 сигнал разрешения записи с первого выхода блока коррекции 12 снимается и формируется сигнал на втором выходе, который осуществляет запись кода логического нуля в блок оперативной памяти 8 по адресу регистра 2, При одинаковых сигналах на входах компаратора 9 на его выходе формируется сигнал логической единицы, разрешая прохождение импульсов через элемент И. 10. Очередной импульс переключает регистр 2 адреса для опроса следующего датчика и снимает сиг- нал записи с второго выхода блока коррекции. Аналогично записывается код логического нуля во все ячейки блока оперативной памяти, где до этого была записана логическая единица. После окончания первого цикла опроса на выходе переполнения регистра 2 адреса появляется сигнал, который устанавливает триггер 3 в исходное положение, тем самым подключая через элемент И 5 выход мультиплексора 5 к входу блока оперативной памяти 8, а также снимая сигнал сброса с блоков оперативной памяти и управления.

Во втором и последующих циклах опроса код от датчика, перешедшего в аварийное состояние /код логической единицы/, не соответствует коду с выхода блока оперативной памяти 8 /код логического нуля/. На выходе компаратора 9 появляется сигнал логического нуля, который запрещает прохождение ТИ1 через элемент И 10, а, поступая на второй вход блока коррекции, сигнализирует о переходе датчика в аварийное состояние. При сигнале логического нуля на первом входе блока коррекции /блок буферной памяти свободен/ и под действием первого ТИ1 на первом выходе блока коррекции формируется сигнал разрешения записи, который поступает на вход блока буферной памяти. Первый ТИ2 записывает код адреса и код изменения этого состояния в первый регистр блока буферной памяти. Второй ТИ1 снимает сигнал разрешения записи с первого выхода блока коррекции и формирует сигнал на втором выходе, который записывает в блок оперативной памяти код аварийного состояния датчика по адресу регистра 2. На выходе компаратора формируется сигнал разрешения для прохождения ТИ1 через элемент И 0, Второй ТИ2 сдвигает код сообщения из первого регистра блока буферной памяти во второй, а в первый записывает код 000.... Третий ТИ1 переводит регистр 2 адреса в следующее положение для опроса следующего датчика и снимает сигнал с второго выхода блока коррекции 12. Третий ТИ2 сдвигает код сообщения из второго регистра в следующий, а в первый два записываются 000.... Выявление перехода других датчиков из одного состояния в другое и запись сообщений об этих переходах в буферную память осуществляется аналогично описанному. Под действием ТИ2 код сообщения в блоке буферной памяти переписывается в последний регистр и на последнем его выходе появляется сигнал готовности. После обработки этого сообщения приходит сигнал квитирования /подтверждения чтения/, который фиксируется в блоке управления. Первый ТИ1 формирует на выходе блока управления сигнал разрешения на списывание. Первым ТИ2 код сообщения с последнего регистра списывается,- а в него записывается

516

код с предпоследнего регистра. Сообщение, записанное в первый регистр, формирует на выходе сигнал логической единицы, который сигнализирует в блок коррекции о занятости всех регистров блока буферной памяти. При этом сообщения в блок буферной памяти не будут записьюаться до тех пор, пока последний регистр блока буферной памяти не освободится от сообщения. По сигналу происходит сдвиг информации в регистрах на одну позицию. В результате первый регистр освобождается и снимается сигнал переполнения блока буферной памяти. Дальнейшая работа устройства происходит аналогично описанному. Сигнал вызова приходит на шину Вызов и фиксируется в блоке приема 13. Данный сигнал по сигналу с вы- хода переполнения регистра 2 подается на вход компаратора 9. Под действием сигнала вьпова на выходе компаратора появляется сигнал наличия информации /код логического нуля/ не только тогда, когда код датчика в данном цикле опроса не соответствует коду датчика в предыдущем цикле опроса /переход датчика из одного состояния в другое/, но и тогда, когда код датчика в данном и предыдущем циклах опроса соответствует аварийному состоянию /код логической единицы от датчика и с выхода блока оперативной памяти/. По сигналу наличия ин- формации происходит запись в блок буферной памяти кода адреса датчика, находящегося в аварийном состоянии, и информация о его состоянии. После опроса всех датчиков вторым сигналом с выхода переполнения регистра адреса 2 сигнал вызова на входе компара06

тора сбрасывается, а приемник возвращается в исходное положение. Таким образом осуществляется выявление и запись информации о датчиках, находящихся i в аварийном состоянии. Это позволяет получить оператору информацию о датчиках, находящихся в аварийном состоянии, что повышает надежность работы устройства. Блок приема сигнал вызова построен на двух D- триггерах серии 564. Сначала сигнал вызова фиксируется первым триггером. Затем импульсом с выхода переполнения регистра адреса перезаписывается во второй триггер, а первый триггер сбрасывается в исходное положение. После опроса всех датчиков вторым импульсом с выхода регистра адреса второй триггер возвращается в исходное положение.

Технико-экономические преимущества предлагаемого устройства по сравнению с прототипом заключаются в повышении надежности работы устройства за счет возможности получения в любой момент времени информации о датчиках, находящихся в аварийном состоянии.

Формула изобретения

Устройство для ввода информации по авт.св. N 1282107, отличающееся -тем, что, с целью повышения надежности устройства, в него введен блок приема сигнала Вызов, синхровход которого соединен с выходом переполнения регистра адреса, информационный вход является входом вызова устройства, выход блока приема сигнала Вызов подключен к третьему входу компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1985 |

|

SU1282107A1 |

| Устройство для реализации нормальных алгорифмов Маркова | 1987 |

|

SU1455345A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Процессор матричной вычислительной системы | 1987 |

|

SU1603395A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Адаптивное устройство для передачи информации | 1989 |

|

SU1735884A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Универсальный цифровой экстремальный мост переменного тока | 1987 |

|

SU1451607A1 |

| Устройство для ввода информации от датчиков | 1990 |

|

SU1691828A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

Изобретение относится к вычислительной технике и может быть использовано для сбора информации от датчиков в автоматизированных систе / мах управления технологическими процессами. Цель изобретения - повышение надежности. Устройство содержит Лормирователь 1, регистр адреса 2, триггер 3, мультиплексор- 4, элементы И 5, 10, блок управления 6, блок буферной памяти 7, блок оперативной памяти 8, компаратор 9, генератор 11, блок коррекции 12, блок приема сигнала Вызов. Повышение надежности устройства заключается в возможности получения в любой момент времени информации о датчиках, находящихся в аварийном состоянии. 1 ил. г (Л

Авторы

Даты

1991-04-23—Публикация

1989-03-23—Подача