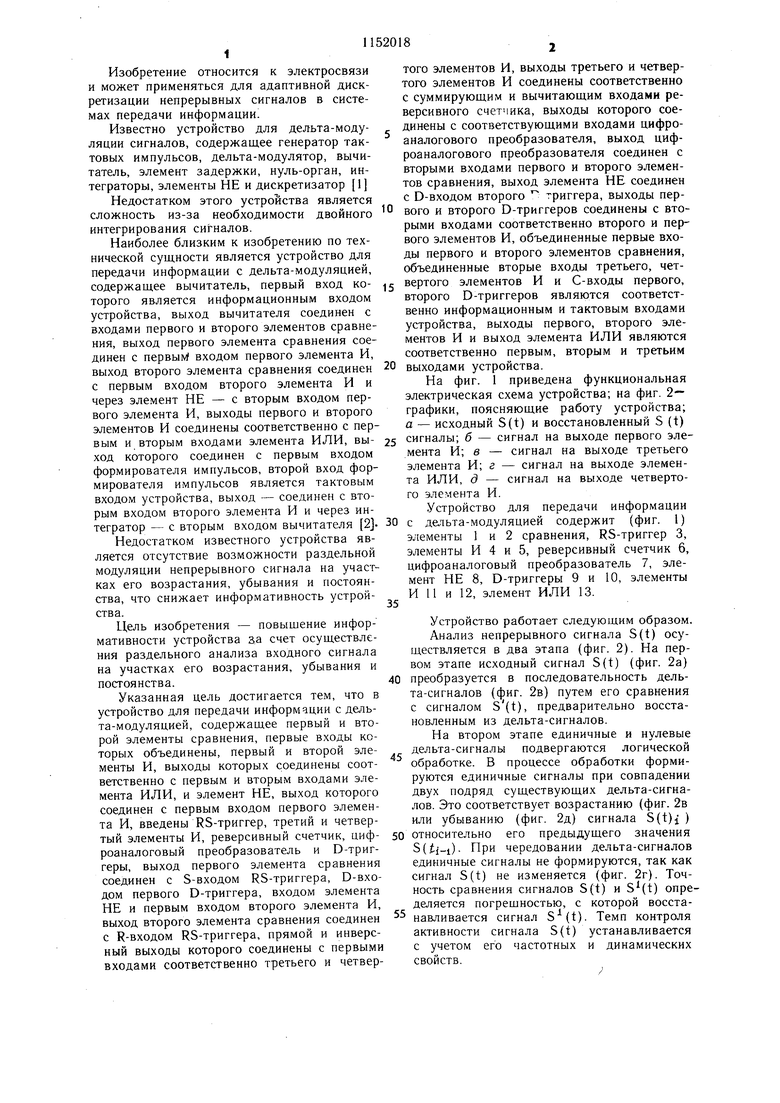

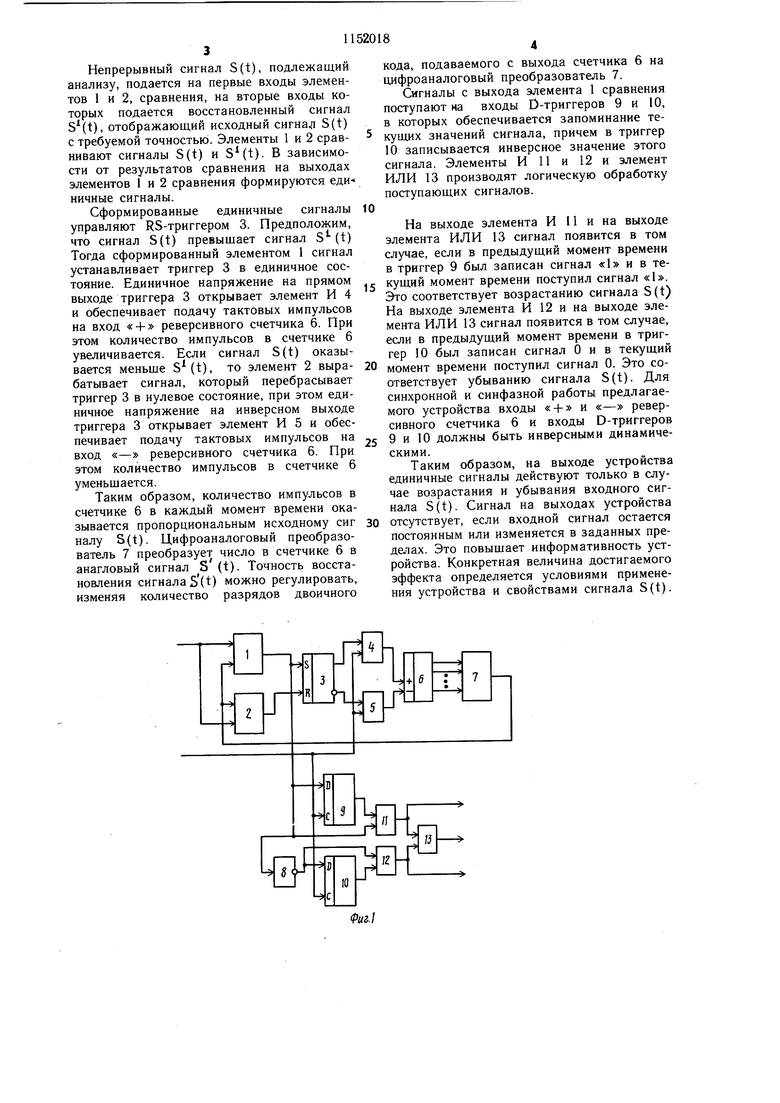

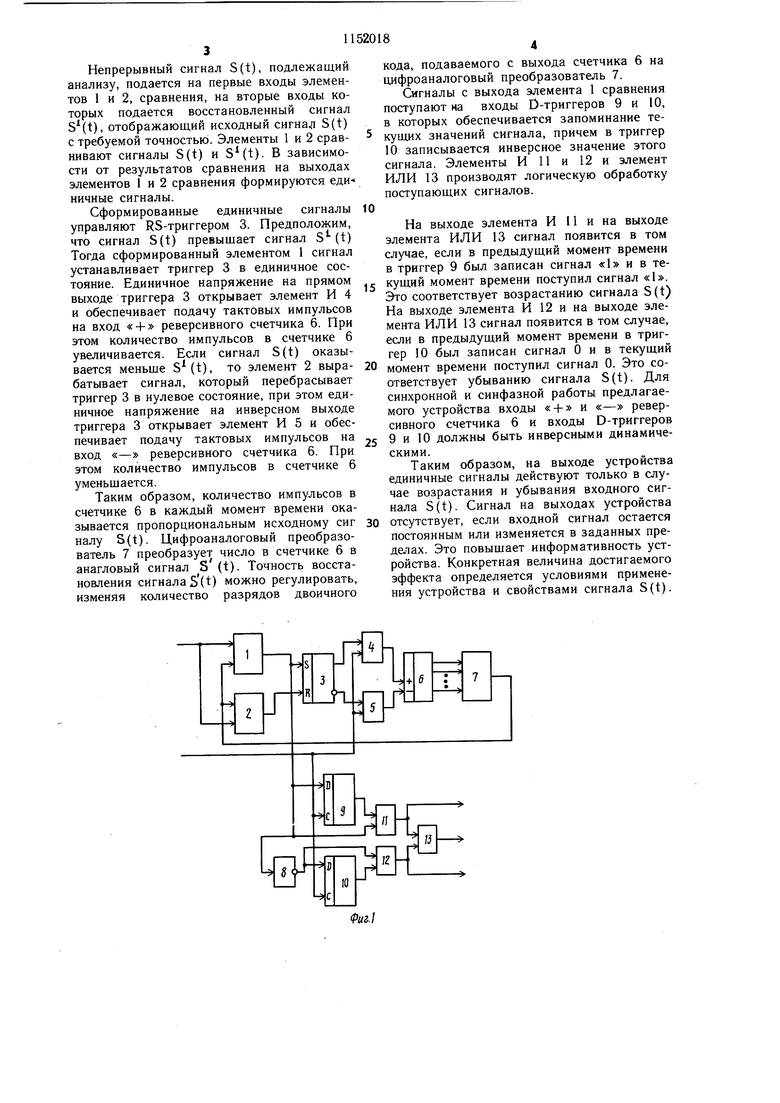

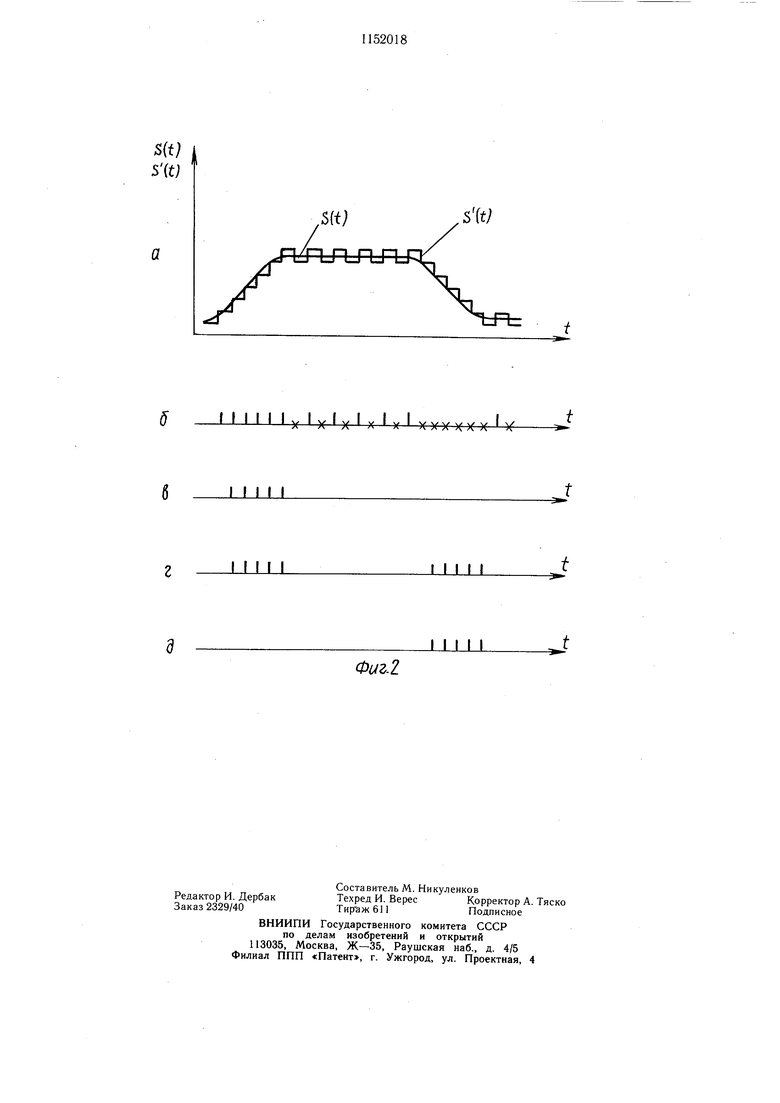

Изобретение относится к электросвязи и может применяться для адаптивной дискретизации непрерывных сигналов в системах передачи информации Известно устройство для дельта-модуляции сигналов, содержащее генератор тактовых импульсов, дельта-модулятор, вычитатель, элемент задержки, нуль-орган, интеграторы, элементы НЕ и дискретизатор 1 Недостатком этого устройства является сложность из-за необходимости двойного интегрирования сигналов. Наиболее близким к изобретению по технической сущности является устройство для передачи информации с дельта-модуляцией, содержащее вычитатель, первый вход которого является информационным входом устройства, выход вычитателя соединен с входами первого и второго элементов сравнения, выход первого элемента сравнения соединен с nepBbiivi входом первого элемента И, выход второго элемента сравнения соединен с первым входом второго элемента И и через элемент НЕ - с вторым входом первого элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с первым входом формирователя импульсов, второй вход формирователя импульсов является тактовым входом устройства, выход - соединен с вторым входом второго элемента И и через интегратор - с вторым входом вычитателя 2. Недостатком известного устройства является отсутствие возможности раздельной модуляции непрерывного сигнала на участках его возрастания, убывания и постоянства, что снижает информативность устройства. Цель изобретения - повышение информативности устройства за счет осуществления раздельного анализа входного сигнала на участках его возрастания, убывания и постоянства. Указанная цель достигается тем, что в устройство для передачи информации с дельта-модуляцией, содержащее первый и второй элементы сравнения, первые входы которых объединены, первый и второй элементы И, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, и элемент НЕ, выход которого соединен с первым входом первого элемента И, введены RS-триггер, третий и четвертый элементы И, реверсивный счетчик, цифроаналоговый преобразователь и D-триггеры, выход первого элемента сравнения соединен с S-входом RS-триггера, D-входом первого D-триггера, входом элемента НЕ и первым входом второго элемента И, выход второго элемента сравнения соединен с R-входом RS-триггера, прямой и инверсный выходы которого соединены с первыми входами соответственно третьего и четвертого элементов И, выходы третьего и четвертого элементов И соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, выходы которого соединены с соответствующими входами цифроаналогового преобразователя, выход цифроаналогового преобразователя соединен с вторыми входами первого и второго элементов сравнения, выход элемента НЕ соединен с D-входом второго триггера, выходы первого и второго D-триггеров соединены с вторыми входами соответственно второго и первого элементов И, объединенные первые входы первого и второго элементов сравнения, объединенные вторые входы третьего, четвертого элементов И и С-входы первого, второго D-триггеров являются соответственно информационным и тактовым входами устройства, выходы первого, второго элементов И и выход элемента ИЛИ являются соответственно первым, вторым и третьим выходами устройства. На фиг. 1 приведена функциональная электрическая схема устройства; на фиг. 2- графики, поясняющие работу устройства; а - исходный S(t) и восстановленный S (t) сигналы; б - сигнал на выходе первого элемента И; 8 - сигнал на выходе третьего элемента И; г - сигнал на выходе элемента ИЛИ, д - сигнал на выходе четвертого элемента И. Устройство для передачи информации с дельта-модуляцией содержит (фиг. 1) элементы 1 и 2 сравнения, RS-триггер 3, элементы И 4 и 5, реверсивный счетчик 6, цифроаналоговый преобразователь 7, элемент НЕ 8, D-триггеры 9 и 10, элементы И 11 и 12, элемент ИЛИ 13. Устройство работает следующим образом, Анализ непрерывного сигнала S(t) осуществляется в два этапа (фиг. 2). На первом этапе исходный сигнал S(t) (фиг. 2а) преобразуется в последовательность дельта-сигналов (фиг. 2в) путем его сравнения с сигналом S(t), предварительно восстановленным из дельта-сигналов. На втором этапе единичные и нулевые дельта-сигналы подвергаются логической обработке. В процессе обработки формируются единичные сигналы при совпадении двух подряд существующих дельта-сигналов. Это соответствует возрастанию (фиг. 2в или убыванию (фиг. 2д) сигнала S(t)i ) относительно его предыдущего значения S(). При чередовании дельта-сигналов единичные сигналы не формируются, так как сигнал S(t) не изменяется (фиг. 2г). Точность сравнения сигналов S(t) и S(t) определяется погрешностью, с которой восстанавливается сигнал S(t). Темп контроля активности сигнала S(t) устанавливается с учетом его частотных и динамических свойств. Непрерывный сигнал S(t), подлежащий анализу, подается на первые входы элементов 1 и 2, сравнения, на вторые входы которых подается восстановленный сигнал S(t), отображающий исходный сигнал S(t) с требуемой точностью. Элементы 1 и 2 сравнивают сигналы S(t) и S(t). В зависимости от результатов сравнения на выходах элементов 1 и 2 сравнения формируются еди ничные сигналы. Сформированные единичные сигналы управляют RS-триггером 3. Предположим, что сигнал S(t) превыщает сигнал S (t) Тогда сформированный элементом 1 сигнал устанавливает триггер 3 в единичное состояние. Единичное напряжение на прямом выходе триггера 3 открывает элемент И 4 и обеспечивает подачу тактовых импульсов на вход « + реверсивного счетчика 6. При этом количество импульсов в счетчике 6 увеличивается. Если сигнал S(t) оказывается меньще ), то элемент 2 вырабатывает сигнал, который перебрасывает триггер 3 в нулевое состояние, при этом единичное напряжение на инверсном выходе триггера 3 открывает элемент И 5 и обеспечивает подачу тактовых импульсов на вход «- реверсивного счетчика 6. При этом количество импульсов в счетчике 6 уменьщается. Таким образом, количество импульсов в счетчике 6 в каждый момент времени оказывается пропорциональным исходному сиг налу S(t). Цифроаналоговый преобразователь 7 преобразует число в счетчике 6 в анагловый сигнал S (t). Точность восстановления сигнала S(t) можно регулировать, изменяя количество разрядов двоичного кода, подаваемого с выхода счетчика 6 на щ1фроаналоговый преобразователь 7. Сигналы с выхода элемента 1 сравнения поступают на входы D-триггеров 9 и 10, в которых обеспечивается запоминание текущих значений сигнала, причем в триггер 10 записывается инверсное значение этого сигнала. Элементы И 11 и 12 и элемент ИЛИ 13 производят логическую обработку поступающих сигналов. На выходе элемента И 11 и на выходе элемента ИЛИ 13 сигнал появится в том случае, если в предыдущий момент времени в триггер 9 был записан сигнал «1 и в текущий момент времени поступил сигнал «1. Это соответствует возрастанию сигнала S(t) j-ja выходе элемента И 12 и на выходе элемента ИЛИ 13 сигнал появится в том случае, gf-jj g предыдущий момент времени в тригpgp ю был записан сигнал О и в текущий момент времени поступил сигнал 0. Это соответствует убыванию сигнала S(t). Для синхронной и синфазной работы предлагаемого устройства входы «-t- и «- реверсивного счетчика 6 и входы D-триггеров 9 и 10 должны быть инверсными динамическими. Таким образом, на выходе устройства единичные сигналы действуют только в случае возрастания и убывания входного сигнала S(t). Сигнал на выходах устройства отсутствует, если входной сигнал остается постоянным или изменяется в заданных пределах. Это повышает информативность устройства. Конкретная величина достигаемого эффекта определяется условиями применения устройства и свойствами сигнала S(t).

5(t) S(tj

fl

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивного преобразования аналоговых сигналов в код | 1989 |

|

SU1615772A1 |

| Анализатор активности непрерывных сигналов | 1987 |

|

SU1438004A2 |

| Устройство для контроля аналого-цифрового преобразователя | 1986 |

|

SU1585897A1 |

| Устройство слежения за дорожкой дискового носителя информации | 1987 |

|

SU1614031A1 |

| Устройство слежения за информационной дорожкой дискового носителя информации | 1984 |

|

SU1167649A1 |

| Устройство для измерения времени установления выходного сигнала цифро-аналоговых преобразователей | 1985 |

|

SU1298916A1 |

| Число-импульсный следящий электропривод | 1983 |

|

SU1124256A1 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Устройство для контроля и управления процессом турбинного бурения | 1987 |

|

SU1461881A1 |

| Устройство для передачи сигналов приращений | 1981 |

|

SU955163A1 |

УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ, содержащее первый и второй элементы сравнения, первые входы которых объединены, первый и второй элемнты И, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, и элемент НЕ, выход которого соединен с первым входом первого элемента И, отличающееся тем, что, с целью повышения информативности устройства, в него введены RS-триггер, третий и четвертый элементы И, реверсивный счетчик, цифроаналоговый преобразователь и D-триггеры, выход первого элемента сравнения соединен с S-входом RS-триггера, D-входом первого D-триггера, входом элемента НЕ и первым входом второго элемента И, выход второго элемента сравнения соединен с R-входом RS-триггера, прямой и инверсный выходы которого соединены с первыми входами соответственно третьего и четвертого элементов И, выходы третьего и четвертого элементов И соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, выходы которого соединены с соответствующими входами цифроаналогового преобразователя, выход цифроаналогового преобразователя соединен с вторыми входами первого и второго элементов сравнения, выход элемента НЕ соединен с D-входом второго D-триггера, выходы первого и второго D-триггеров соединены с вторыми (Л входами соответственно второго и первого элементов И, объединенные первые входы с первого и второго элементов сравнения, объединенные вторые входы третьего, четвертого элементов И и С-входы первого, второго D-триггеров являются соответственно инфор.мационным и тактовым входами устройства, выходы первого, второго элементов И и выход элемента ИЛИ являются соответственно первым, вторым и третьим выходами устройства. сд ьо

M I I I I у I у I I .. i J

I M I I

I M I

ХУУ XX X V

I I I MJ

t

I I I I I

Фаг.2.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство дельта-модуляции с двойным интегрированием | 1981 |

|

SU982193A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Венедиктов М | |||

| Д., Женевский Ю | |||

| П | |||

| Марков В | |||

| В., Эйдус Г | |||

| С | |||

| Дельта-модуляция | |||

| Теория и применение | |||

| М | |||

| «Связь, 1976 | |||

| с | |||

| Подъемник для выгрузки и нагрузки барж сплавными бревнами, дровами и т.п. | 1919 |

|

SU149A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-12-14—Подача